本发明属于数字时钟的技术领域;具体涉及一种多数字电子设备同步的随机误差估计系统的及其估计方法。

背景技术:

电子设备具有非常广泛的应用,现如今以数字化的设备居多。相较于模拟设备,数字设备具有体积小、重量轻、处理速度快、兼容性强、易于维护和智能化等优点。电子设备数字化的概念在于,设备的工作不再是连续的,而是被量化为一个个时间上相同的微小步骤来间断执行的。而推动和控制设备按照这种步骤执行的源,就是数字时钟,常以方波或正弦波的形式出现。

在设计对精度有一定要求的测试测量设备时,误差分析与误差估计是一个重要的环节。以本专利涉及的同步随机误差为例,总随机误差形成的过程比包含多项随机误差,其是由各单项随机误差的综合影响所确定的,因此,误差估计的概念即为,根据给定测量结果总随机误差指标,选择设计方案;分析设计过程所有随机误差的来源,估计各个单项随机误差的大小,保证设计结果在允许的随机误差范围之内。

但是设备的精度如何,具体的指标只有在设备制作完成之后才能测得。如果最终制作的设备精度不符合指标要求,推倒重做不仅让费资源与时间,也不符合设计测试测量设备的步骤。因此在制作设备之前,需要通过理论与经验的推导、建模等,获得所需指标的估计方法,才能确保所设计的设备在制作完成后符合要求,减少不必要的浪费。

技术实现要素:

本发明提供一种多数字电子设备同步的随机误差估计系统的估计方法,用于解决在设计多设备同步的系统时,如何有效地为每个设计环节估计同步随机误差的问题,以保证时钟的同步随机误差在指标允许的范围之内。

本发明通过以下技术方案实现:

一种多数字电子设备同步的随机误差估计系统,所述随机误差估计系统包括初始多路器、a个时钟缓冲器、xmm走线、ymm补偿走线、设备x和设备y,所述随机误差估计系统分为两路路径,所述第一条路径为初始多路器经过nx次频率变换操作、mx次多路复制操作、xmm走线长度和a个时钟缓冲器连接设备x,所述第二条路径为初始多路器经过ny次频率变换操作、my次多路复制操作、xmm走线长度和ymm补偿走线长度连接设备y。

一种多数字电子设备同步的随机误差估计系统的估计方法,所述估计方法包括以下步骤,

步骤1:根据多设备同步的系统需求,确定总的同步随机误差需求,记为小于t0;

步骤2:选择所需要的频率变换器、多路器元器件的型号;

步骤3:计算由于频率变换操作引起的抖动而带来的随机误差t1;

步骤4:计算由于多路复制操作引起的偏移而带来的随机误差t2;

步骤5:估算走线中同轴电缆引起的随机误差t3;

步骤6:估算走线中射频连接器引起的随机误差t4;

步骤7:估算走线中pcb布线引起的随机误差t5;

步骤8:将步骤3-步骤7中的随机误差t1-t5直接相加,即为随机误差估计。

进一步的,所述步骤1频率变换芯片给出相位噪声的参数,因为每个频率变换器的相位噪声是固定的,而抖动的大小则会受输出时钟频率的影响,因此同一个频率变换器,抖动是不固定的,抖动和相位噪声是同一种现象时钟的不稳定性的不同解释:抖动是在时域的表述,而相位噪声则是在频域的表述,表示时钟信号除在理想频率之外其他频率分量的功率谱密度大小。

进一步的,所述步骤3的随机误差t1具体为,将相位噪声转化为抖动的公式如下,

式中jrms——时钟抖动振幅的均方根;

l(f)——频谱上距离中心频率fc偏移f的频率点上的相位噪声;

fc——输出时钟中心频率,在此处即为设备的的工作频率。

进一步的,所述步骤4的随机误差t2具体为,根据路径上每个多路器所需输出时钟的信号格式,对应查找到多路器中给出的偏移值,计算其引起的随机误差的公式如下,

t2=ti ts1 ts2 … tsn

式中ts0——初始多路器造成的偏移;

ts1~tsn——分别为m个多路器造成的偏移。

进一步的,所述步骤5的随机误差t3具体为,同轴电缆介电材料具有因电缆弯曲而改变的特性,电缆弯曲程度不同导致了介电常数的不一致性,电缆供应商的数据手册通常会规定特定弯曲半径和频率下相位误差,根据其来估算其造成的随机误差的公式如下,

式中

f——电缆上承载时钟的频率。

进一步的,所述步骤6的随机误差t4具体为,每个连接器可能会在时钟路径之间增加至多3ps同步误差,因此可由如下公式进行估计,

t4≈nc×3ps

式中nc——时钟路径上射频连接器的个数。

进一步的,所述步骤7的随机误差t5具体为,估算pcb布线的传输线总电容、传输线总电感的公式如下,

式中l——导线长度;

w——线宽;

h——导线与参考平面的高度;

t——导线铜厚;

εγ——pcb板材的介电常数;

估算pcb走线和传输线电感电容对信号造成的延时大小可分别由如下公式给出,

对导线长度l进行估计后,获得两条时钟路径上布线长度δl、寄生电容δc、寄生电感δl的差别,再利用方和根的方式进行合成,通过如下公式获得pcb走线带来的同步随机误差,

进一步的,所述步骤8具体为,若和小于所提总同步误差需求t0,则设计与误差估计完成;若和超过所提总同步误差需求t0,则返回重新进行设计,并重复步骤3~步骤8,直到设计结果符合预定需求,误差估计结束。

本发明的有益效果是:

(1)为多数字电子设备的同步设计提供了很好的精度校验方法,大幅提高首次设计结果符合预期指标需求的成功率,避免了产品多次迭代设计造成资源的浪费;

(2)本专利提出的方法考虑因素全面,充分考虑实际工程应用条件与限制,同时紧密结合理论推导,估计结果准确性好。

(3)本专利提出的方法可用于绝大部分数字电子设备的同步设计中,应用范围广;

(4)本专利提出的方法具有计算简单、易于理解、计算速度快、计算效率高的特点;

附图说明

附图1现有技术中多设备同步系统结构图。

附图2本发明的初步简化的时钟路径图。

附图3本发明的最终简化的时钟路径图。

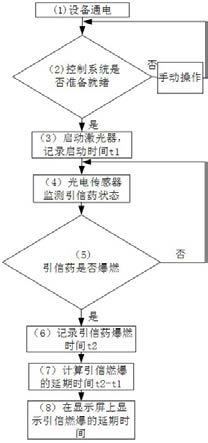

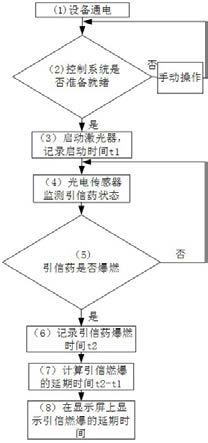

附图4本发明的系统整体相位误差估计方法示例图。

附图5本发明的步骤流程图。

具体实施方式

下面将结合本发明实施例中的附图对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1,图2,图3所示,时钟发生器提供原始的时钟源信号,为时钟信号的起点;频率变换器可对输入时钟进行分频、倍频等处理;多路缓冲器将输入的单一时钟复制为多路同频同相的时钟;各个设备接收最终的时钟信号,为时钟信号的终点;每一条走线均代表一个时钟信号的路径。图中实线框代表必须存在的元件,虚线框代表可能存在的元件,视具体应用需求所定。此处需要特别说明,图1仅为多设备同步系统的简化结构,实际应用中,市场上常见的多路器可提供至多24条时钟输出通道,且每个通道之后所连接的结构均有可能为多路器1后所接三种结构中的任意一种,此外多路器还可进行串联。

根据图1所示,总随机误差即为与最终到达设备1至设备5走线上所承载时钟信号的同步随机误差;而各个单项同步随机误差,分别来源于频率变换器、多路器、走线等多个部分。同步随机误差是在多路器1及其之后的结构中出现的,故将其记为初始多路器。在做到达设备x和设备y的两条时钟路径之间的同步随机误差分析时,可设自初始多路器之后,到达设备x时时钟共经过了nx个频率变换器、mx个中间多路器,并将所有走线统称为走线x0;同理到达设备y时时钟共经过了ny个频率变换器、my个中间多路器,所有走线统称为走线y0,这样便可将图1简化为图2所示的结构。

进一步地,不管是频率变换器还是多路器中,为了提高时钟信号的驱动能力,经常会在器件中加入多个时钟缓冲器,但缓冲器会造成输入输出之间的相位延迟,延迟量与半导体工艺流片硅含量的一致性有关。以现有的技术,由于流片一致性而造成的延时不同的随机同步误差可以忽略;同时,缓冲器的数量以及造成的延迟时间值都是可以确定的。因此由于不同时钟路径上由于缓冲器数量不同而导致的同步误差为系统可确定误差,是可以补偿的,常用方法为走线补偿。因此可设路径x比路径y中多了a个缓冲器,只留下对时钟同步误差有影响的部分,将图2最终简化为图3所示的结构。

一种多数字电子设备同步的随机误差估计系统,所述随机误差估计系统包括初始多路器、a个时钟缓冲器、xmm走线、ymm补偿走线、设备x、设备y、ny个频率变换器、my个中间多路器、nx个频率变换器和mx个中间多路器,所述随机误差估计系统分为两路路径,所述初始多路器的第一条路径包括与nx个频率变换器相连接,所述nx个频率变换器与mx个中间多路器相连接,所述mx个中间多路器与走线x0相连接,所述走线x0与设备x相连接,所述初始多路器的第二条路径包括与ny个频率变换器相连接,所述ny个频率变换器与my个中间多路器相连接,所述my个中间多路器与走线y0相连接,所述走线y0与设备y相连接;

图3所示,所述第一条路径为初始多路器经过nx次频率变换操作、mx次多路复制操作、xmm走线长度和a个时钟缓冲器连接设备x,所述第二条路径为初始多路器经过ny次频率变换操作、my次多路复制操作、xmm走线长度和ymm补偿走线长度连接设备y。

一种多数字电子设备同步的随机误差估计系统的估计方法,所述随机误差估计方法包括以下步骤,

步骤1:根据多设备同步的系统需求,确定总的同步随机误差需求,记为小于t0(ps);

步骤2:选择所需要的频率变换器、多路器元器件的型号;

步骤3:计算由于频率变换操作引起的抖动而带来的随机误差t1;

步骤4:计算由于多路复制操作引起的偏移而带来的随机误差t2;

步骤5:估算走线中同轴电缆引起的随机误差t3;

步骤6:估算走线中射频连接器引起的随机误差t4;

步骤7:估算走线中pcb布线引起的随机误差t5;

步骤8:将步骤3-步骤7中的随机误差t1-t5直接相加,即为随机误差估计。

进一步的,所述步骤1频率变换芯片给出相位噪声的参数,因为每个频率变换器的相位噪声是固定的,而抖动的大小则会受输出时钟频率的影响,因此同一个频率变换器,抖动是不固定的,抖动和相位噪声是同一种现象时钟的不稳定性的不同解释:抖动是在时域的表述,而相位噪声则是在频域的表述,表示时钟信号除在理想频率之外其他频率分量的功率谱密度大小。根据这个概念,当如图3所示多个频率变换操作串行连接时,造成的总抖动并不是每个频率变换操作造成抖动的简单叠加,故应该首先算出所有频率变换操作的一个整体的相位噪声值,相位噪声的获取方法如下:将输入时钟的相位噪声与各个频率转换器的相位噪声曲线画在同一个波德图中,取顶层包络,如图4所示。

进一步的,所述步骤3的随机误差t1具体为,将相位噪声转化为抖动的公式如下,

式中jrms——时钟抖动振幅的均方根(s);

l(f)——频谱上距离中心频率fc偏移f的频率点上的相位噪声(dbc/hz);

fc——输出时钟中心频率,在此处即为设备的的工作频率(hz)。

进一步的,所述步骤4的随机误差t2具体为,根据路径上每个多路器所需输出时钟的信号格式(单端或差分),对应查找到多路器中给出的偏移值,计算其引起的随机误差的公式如下,

t2=ti ts1 ts2 … tsn

式中ts0——初始多路器造成的偏移(ps);

ts1~tsn——分别为m个多路器造成的偏移(ps)。

进一步的,所述步骤5的随机误差t3具体为,同轴电缆介电材料具有因电缆弯曲而改变的特性,电缆弯曲程度不同导致了介电常数的不一致性。电缆供应商的数据手册通常会规定特定弯曲半径和频率下相位误差,根据其来估算其造成的随机误差的公式如下,

式中

f——电缆上承载时钟的频率(ghz)。

进一步的,所述步骤6的随机误差t4具体为,射频连接器在安装时的松紧程度的不一致性会带来同步随机误差,这种误差很难量化,所以每个连接器可能会在时钟路径之间增加至多3ps同步误差,因此可由如下公式进行估计,

t4≈nc×3ps

式中nc——时钟路径上射频连接器的个数。

进一步的,所述步骤7的随机误差t5具体为,pcb布线而造成的随机误差主要来源于pcb不等长以及寄生电感电容的影响,估算pcb布线的传输线总电容、传输线总电感的公式如下,

式中l——导线长度(cm);

w——线宽(cm);

h——导线与参考平面的高度(cm);

t——导线铜厚(cm);

εγ——pcb板材的介电常数(mm);

估算pcb走线和传输线电感电容对信号造成的延时大小可分别由如下公式给出,

pcb布线在正常工艺下造成的不等长可按总长度的0.5%来估算;造成的寄生电容可按传输线总电容的15%估算;造成的寄生电感可按传输线总电感的10%估算,因此在对导线长度l进行估计后,获得两条时钟路径上布线长度δl、寄生电容δc、寄生电感δl的差别,再利用方和根的方式进行合成,通过如下公式获得pcb走线带来的同步随机误差,

进一步的,所述步骤8具体为,若和小于所提总同步误差需求t0,则设计与误差估计完成;若和超过所提总同步误差需求t0,则返回重新进行设计,采取如放宽总同步误差需求、更换性能更好的频率变换器或多路器、减少布线长度等措施,并重复步骤3~步骤8,直到设计结果符合预定需求,误差估计结束。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。