[0001]

本公开涉及一种半导体装置,特别涉及一种具有嵌入式静态随机存取存储器(sram)单元的半导体装置。

背景技术:

[0002]

半导体集成电路(integrated circuit,ic)工业已经历了指数性的成长。在ic发展的过程中,功能密度(functional density,例如:每单位芯片面积的互连装置的数量)通常会增加,而几何尺寸(例如:使用制造工艺所能产生的最小组件(或线路))则会缩小。这种微缩的过程通常会通过提高生产效率及降低相关成本来提供益处。这种微缩也增加了ic加工及制造的复杂性,且为了实现这些进步,在ic制造方面也需要相似的发展。

[0003]

举例来说,静态随机存取存储器(static random-access memory,sram)单元(cell)常被整合到半导体装置中以增加功能密度。这样的应用范围包括工业及科学子系统、车用电子、手机、数码相机、微处理器等。为了满足对更高sram密度的需求,需要持续微缩半导体特征尺寸,并持续最佳化sram单元的布局及选路(routing)。

技术实现要素:

[0004]

本公开实施例提供一种双端sram。上述双端sram包括基板;第一主动区及第二主动区,位于基板上,并大致上沿着第一方向呈纵向指向;第一栅极电极及第二栅极电极,位于基板上,并大致上沿着垂直于第一方向的第二方向呈纵向指向。第一栅极电极接合第一主动区以形成上述双端sram的第一传输闸晶体管,而第二栅极电极接合第二主动区以形成上述双端sram的第二传输闸晶体管。上述双端sram还包括第一栅极接点,被设置于第一栅极电极上,并与第一栅极电极电性连接,以及包括第一源极/漏极接点,大致上沿着第二方向呈纵向指向。第一源极/漏极接点直接接触第一传输闸晶体管的源极/漏极特征以及第二传输闸晶体管的源极/漏极特征。第一栅极接点的一部分及第一源极/漏极接点的一部分自基板的一顶部表面处于相同的垂直层位,且沿着第一方向对准。

[0005]

本公开实施例提供一种双端sram单元。上述双端sram单元包括位于基板上的第一传输闸晶体管以及第二传输闸晶体管。第一传输闸晶体管包括第一栅极电极的一部分,第一栅极电极接合第一主动区的一部分。第二传输闸晶体管包括第二栅极电极的一部分,第二栅极电极接合第二主动区的一部分。第一栅极电极以及第二栅极电极连接至上述双端sram单元的不同字线。第一主动区及第二主动区大致上沿着第一方向呈纵向指向。第一栅极电极以及第二栅极电极大致上沿着垂直于第一方向的第二方向呈纵向指向。上述双端sram单元还包括第一栅极接点,被设置于第一栅极电极上,以及包括第一源极/漏极接点,大致上沿着第二方向呈纵向指向。第一源极/漏极接点被设置于第一传输闸晶体管的源极/漏极特征以及第二传输闸晶体管的源极/漏极特征两者上。第一源极/漏极接点被以相同于或低于第一栅极接点的一顶部表面的垂直层位设置。

[0006]

本公开实施例提供双端sram单元的一种布局。上述布局包括位于p型井上的第一

主动区、第二主动区、第三主动区、以及第四主动区,其中每个第一主动区、第二主动区、第三主动区、以及第四主动区大致上沿着第一方向呈纵向指向。上述布局还包括第一栅极电极,位于第一主动区及第二主动区上;第二栅极电极,位于第三主动区及第四主动区上;以及第三栅极电极,位于第一主动区、第二主动区、第三主动区、以及第四主动区上。每个第一栅极电极、第二栅极电极、以及第三栅极电极大致上沿着与第一方向垂直的第二方向呈纵向指向。上述布局还包括源极/漏极接点特征,以俯视图来看被设置于第一栅极电极与第三栅极电极之间,以及第二栅极电极与第三栅极电极之间。源极/漏极接点特征接触第一主动区上的第一源极/漏极特征、第二主动区上的第二源极/漏极特征、第三主动区上的第三源极/漏极特征、以及第四主动区上的一第四源极/漏极特征。

附图说明

[0007]

本公开的实施方式可自下列详细说明及阅读附图而得到最佳的理解。应注意的是,根据产业的标准作法,各种特征并未依比例绘制。事实上,各种特征的尺寸可能会任意增减以使说明清晰易懂。

[0008]

图1是根据本公开多种实施方式所示,具有嵌入式sram单元的集成电路(ic)的简化方框图。

[0009]

图2根据本公开实施例,显示双端(dual-port,dp)sram单元的示意图。

[0010]

图3至图5是根据本公开一些实施例所示,图2的双端sram单元的布局的一部分的俯视图。

[0011]

图6a及图6b是根据本公开一些实施例所示,图2的双端sram单元的一部分的截面图。

[0012]

图7是根据本公开一些实施例所示,图2的双端sram单元的布局的一部分的俯视图。

[0013]

图8a及图8b是根据本公开一些实施例所示,图2的双端sram单元的一部分的截面图。

[0014]

图9及图10是根据本公开一些实施例所示,图2的双端sram单元的布局的一部分的俯视图。

[0015]

附图标记说明:

[0016]

100:半导体装置

[0017]

102:sram宏码

[0018]

200:双端sram单元

[0019]

201,203:虚线圆圈

[0020]

bl-a,bl-b:位元线

[0021]

bl-a_bar,bl-b_bar:位元线

[0022]

wl:字线

[0023]

pg1~pg4:传输闸晶体管

[0024]

pu1,pu2:上拉晶体管

[0025]

pd1,pd2:下拉晶体管

[0026]

204:主动区

[0027]

204-1~204-10:主动区

[0028]

210:栅极电极

[0029]

210-1~210-6:栅极电极

[0030]

213:源极/漏极特征

[0031]

213-1~213-28:源极/漏极特征

[0032]

220:源极/漏极接点

[0033]

220-1~220-10:源极/漏极接点

[0034]

222:切割图案

[0035]

230:栅极接点

[0036]

230-1~230-6:栅极接点

[0037]

240:源极/漏极通孔插塞

[0038]

240-1~240-10:源极/漏极通孔插塞

[0039]

aa,bb:线段

[0040]

202:基板

[0041]

206:隔离结构

[0042]

208:介电层

[0043]

209-1~209-4:掺杂的半导体层

[0044]

211:硅化层

[0045]

210-2d:栅极介电层

[0046]

210-2m:栅极金属层

[0047]

210-3d:栅极介电层

[0048]

210-3m:栅极金属层

[0049]

s1:间隔

[0050]

250:金属线

[0051]

250-1~250-11:金属线

[0052]

215:互连层

[0053]

217:蚀刻停止层

[0054]

218:ild层

[0055]

260:通孔

[0056]

260-1~260-4:通孔

[0057]

270:金属线

[0058]

270-1~270-4:金属线

[0059]

280:通孔

[0060]

280-1~280-2:通孔

[0061]

290:金属线

[0062]

290-1~290-2:金属线

[0063]

300-1:金属线

具体实施方式

[0064]

以下的公开提供许多不同实施例或范例,用以实施本公开的不同特征。本公开的各部件及排列方式,其特定范例叙述于下以简化说明。理所当然的,这些范例并非用以限制本公开。举例来说,若叙述中有着第一特征成形于第二特征之上或上方,其可能包含第一特征与第二特征以直接接触成形的实施例,亦可能包含有附加特征形成于第一特征与第二特征之间,而使第一特征与第二特征间并非直接接触的实施例。此外,本公开可在多种范例中重复参考数字及/或字母。该重复的目的为简化及清晰易懂,且本身并不规定所讨论的多种实施例及/或配置间的关系。

[0065]

进一步来说,本公开可能会使用空间相对术语,例如“在

…

下方”、“下方”、“低于”、“在

…

上方”、“高于”及类似词汇,以便于叙述附图中一个元件或特征与其他元件或特征间的关系。除了附图所描绘的方位外,空间相对术语亦欲涵盖使用中或操作中的装置其不同方位。设备可能会被转向不同方位(旋转90度或其他方位),而此处所使用的空间相对术语则可相应地进行解读。再进一步来说,当一数字或一数字范围以“大约”、“大概”或类似的用语描述,该用语旨在涵盖所述数字的 /-10%,除非另有说明。举例来说,用语“约5nm”所涵盖的尺寸范围自4.5nm至5.5nm。

[0066]

本公开涉及半导体装置及制造方法,特别涉及具有嵌入式sram单元或sram宏码的集成电路(ic)。通过利用先进光刻(lithography)的高分辨率,sram单元的布局比起其他设计得到优选的最佳化,例如通过在单次曝光中提供20纳米(nm)或小于诸如次8nm的分辨率的极紫外光(extreme ultraviolet)光刻。除非使用多重图案化,否则无法通过193nm浸润式(immersion)光刻技术实现这种分辨率。此外,使用单次曝光能降低由多重图案化中可能的未对准(misalignment)所引起的变化。具体来说,本实施例的sram单元的布局简化了其他设计上的金属选路(routing)。

[0067]

图1显示具有sram宏码102的半导体装置100。半导体装置,举例来说,可为微处理器、特殊应用集成电路(application specific integrated circuit,asic)、现场可程序化闸阵列(field programmable gate array,fpga)、或系数字信号处理器(digital signal processor,dsp)。半导体装置100的确实功能并不限于所提供的内容。存储器宏码102包括多个双端sram单元,双端sram单元的范例示意图显示于图2。存储器宏码102亦可包括其他类型的sram单元,例如单端sram单元(未附图)以及多个周边逻辑电路(peripheral logic circuit,未图示)。sram单元用于存储存储器位元,而周边逻辑电路则用于执行各种功能,例如写入及/或读取位址解码器(address decoder)、字/位元选择器、数据驱动器(data driver)、存储器自我测式等。每个sram单元及逻辑电路可被实施为平面晶体管(planar transistor)、鳍式场效晶体管(finfet)、栅极全环(gate-all-around,gaa)纳米片晶体管、gaa纳米线晶体管、或其他类型的晶体管。此外,每个sram单元及逻辑电路可包括各种接点(contact)特征(或接点)、通孔(via)以及金属线,以用于连接晶体管的源极、漏极以及栅极电极(或端子)来形成集成电路。

[0068]

图2显示双端(dp)sram单元200的示意图。双端sram单元200包括八个晶体管(8t)。因此亦被称为8t双端sram。在多种实施例中,双端sram单元200可用8个或更多个晶体管来实施。参照图2,8t双端sram单元200包括两个pmosfet(例如:pmos finfet)作为上拉晶体管pu1及上拉晶体管pu2、两个nmosfet(例如:nmos finfet)作为下拉晶体管pd1及下拉晶体管

pd2、两个nmosfet(例如:nmos finfet)作为传输闸晶体管pg1及传输闸晶体管pg2、以及两个nmosfet(例如:nmos finfet)作为传输闸晶体管pg3及传输闸晶体管pg4。上拉晶体管pu1与下拉晶体管pd1耦接以形成反相器(inverter,反相器-1)。上拉晶体管pu2与下拉晶体管pd2耦接形成另一个反相器(反相器-2)。反相器(反相器-1及反相器-2)交叉耦接以形成双端sram单元200的存储单元(storage unit)。双端sram单元200具有两个端,端a以及端b。传输闸晶体管pg1及传输闸晶体管pg2的源极或漏极连接到端a的位元线bl-a以及bl-a_bar。传输闸晶体管pg1及传输闸晶体管pg2的栅极电极连接到端a的字线(端-a wl)。相似地,传输闸晶体管pg3及传输闸晶体管pg4的源极或漏极连接到端b的位元线bl-b以及bl-b_bar。传输闸晶体管pg3及传输闸晶体管pg4的栅极电极连接到端b的字线(端-b wl)。传输闸晶体管pg1、传输闸晶体管pg2、传输闸晶体管pg3、以及传输闸晶体管pg4的其他源极和漏极(连接到位元线与字线的那些除外)耦接到双端sram单元200的存储单元。在各种实施例中,每个上拉晶体管pu1、上拉晶体管pu2、下拉晶体管pd1、下拉晶体管pd2、传输闸晶体管pg1、传输闸晶体管pg2、传输闸晶体管pg3、以及传输闸晶体管pg4可包括一或多个用于增强性能的晶体管。本公开的一个实施方式涉及上拉晶体管pu1、下拉晶体管pd1、传输闸晶体管pg1、和传输闸晶体管pg3之间的金属选路(由虚线圆圈201所指示),以及上拉晶体管pu2、下拉晶体管pd2、传输闸晶体管pg2、和传输闸晶体管pg4之间的金属选路(由虚线圆圈203所指示)的最佳化,将于下文进行讨论。

[0069]

图3根据本实施例,显示双端sram单元200的布局图。为了简单起见,图3中的布局仅显示了主动区(active region)以及栅极电极。参照图3,双端sram单元200包括诸如主动区204-n(其中n=1~10)的主动区204,以及诸如栅极电极210-m(其中m=1~6)的栅极电极210。主动区204大致上沿着第一方向y呈纵向指向(oriented lengthwise),而栅极电极210大致上沿着垂直于第一方向y的第二方向x呈纵向指向。在一个实施例中,主动区204可包括用于finfet的鳍片或鳍片主动区,或者在另一个实施例中,主动区204可包括用于gaa fet的垂直堆叠的多个纳米线或纳米片。主动区204可采用其他合适的形式或形状。在本实施例中,主动区204-1至204-4被设置于p型井上,而主动区204-7至204-10被设置于另一个p型井上,且主动区204-5至204-6被设置于n型井上,其中n型井被夹在两个p型井之间。

[0070]

在一个实施例中,栅极电极210可包括高k值金属栅极结构(意即在高k值栅极介电层上具有一或多个金属层),且在多种实施例中可包括其他材料及/或配置。栅极电极210被设置在主动区204上并接合(engage)主动区204,以形成用于双端sram单元200的各种晶体管。具体来说,栅极电极210-1接合主动区204-1及主动区204-2,以形成两个n型fet(例如:n型finfet)以构成传输闸晶体管pg3。栅极电极210-2接合主动区204-1、主动区204-2、主动区204-3、以及主动区204-4,以形成四个n型fet(例如:n型finfet)以构成下拉晶体管pd1。栅极电极210-2亦接合主动区204-5,以形成p型fet(例如:p型finfet)来作为上拉晶体管pu1。栅极电极210-3接合主动区204-3及主动区204-4,以形成两个n型fet(例如:n型finfet)以构成传输闸晶体管pg1。栅极电极210-4接合主动区204-7、主动区204-8、主动区204-9、以及主动区204-10,以形成四个n型fet(例如:n型finfet)以构成下拉晶体管pd2。栅极电极210-4亦接合主动区域204-6,以形成p型fet(例如:p型finfet)来作为上拉晶体管pu2。栅极电极210-5接合主动区204-7及主动区204-8,以形成两个n型fet(例如:n型finfet)以构成传输闸晶体管pg2。栅极电极210-6接合主动区204-9及主动区204-10,以形

成两个n型fet(例如:n型finfet)以构成传输闸晶体管pg4。

[0071]

图3亦显示各种晶体管的源极/漏极特征,例如形成于栅极电极210两侧的主动区204之上或之中的源极/漏极特征213-q(其中q=1~28),其中在下文中,源极/漏极特征213-q(其中q=1~28)被统称为源极/漏极特征213。在一个实施例中,源极/漏极特征213可包括n型掺杂的硅或p型的硅锗,且可通过掺杂、外延生长(epitaxial growth)、应变(straining)、或其他技术来形成。一些晶体管可能共享源极/漏极特征。举例来说,传输闸晶体管pg3的晶体管与下拉晶体管pd1中的一些晶体管,可共享形成于主动区204-1及主动区204-2之上或之中的源极/漏极特征213-5及213-6。传输闸晶体管pg1中的晶体管与下拉晶体管pd1中的一些晶体管,可共享形成于主动区204-3和主动区204-4之上或之中的源极/漏极特征213-7及213-8。传输闸晶体管pg2的晶体管与下拉晶体管pd2的一些晶体管,可共享形成于主动区204-7和主动区204-8之上或之中的源极/漏极特征213-21及213-22,而传输闸晶体管pg4的晶体管与下拉晶体管pd2的一些晶体管,可共享形成于主动区204-9和主动区204-10之上或之中的源极/漏极特征213-23及213-24。

[0072]

图4是根据本实施例所示,双端sram单元200的布局图。图4中的布局包括如上所述的主动区204及栅极电极210(为了简单起见,在图4中并未标记),且进一步包括源极/漏极接点(或称“md”),例如源极/漏极接点220-p(其中p=1~10)。源极/漏极接点220大致上沿方向x呈纵向指向。图4进一步显示可用于产生源极/漏极接点220的各种切割图案222。在一个范例中,用于源极/漏极接点220的初始图案沿着方向x被形成为三个连续的片状,例如以euv光刻形成。随后,以具有切割图案222的形状的蚀刻遮罩蚀刻三个连续的片状。三个连续的片状的剩余部分成为源极/漏极接点220的最终图案。最终图案可被用于在介电层中蚀刻沟槽以曝露源极/漏极特征。最后,将一或多种金属填充到沟槽中以形成源极/漏极接点220。其他形成源极/漏极接点220的方法也是可用的。举例来说,初始连续图案可被用于在介电层中蚀刻沟槽以曝露源极/漏极特征。接着,将一或多种金属填充到沟槽中,随后使用切割图案222对其进行蚀刻(或切割)。

[0073]

仍旧参照图4,源极/漏极接点220被设置在双端sram单元200中的晶体管的各种源极/漏极特征213上,并与各种源极/漏极特征213接触。具体来说,源极/漏极接点220-1被设置在源极/漏极特征213-1~4上。源极/漏极接点220-2被设置在源极/漏极特征213-5~8与213-14上。源极/漏极接点220-3被设置在源极/漏极特征213-9~10上。源极/漏极接点220-4被设置在源极/漏极特征213-11~12上。源极/漏极接点220-5被设置在源极/漏极特征213-13上。源极/漏极接点220-6被设置在源极/漏极特征213-16上。源极/漏极接点220-7被设置在源极/漏极特征213-17~18上。源极/漏极接点220-8被设置在源极/漏极特征213-19~20上。源极/漏极接点220-9被设置在源极/漏极特征213-15与213-21~213-24上,而源极/漏极接点220-10被设置在源极/漏极特征213-25~213-28上。具体来说,每个源极/漏极接点220在双端sram单元200的一层内形成为连续的片状,源极/漏极特征213之间的连接是使用源极/漏极接点220进行的,且不会使用源极/漏极接点上方的选路资源(routing resource),这与其他设计不同,在其他设计中,源极/漏极特征之间的某些连接是经由源极/漏极接点上方的一或多个互连层进行选路。利用更为简单的选路,本实施例提供了相较其他设计更加紧凑的设计。

[0074]

图5是根据本实施例所示,双端sram单元200的布局图。图5中的布局包括如上所述

的主动区204、栅极电极210、源极/漏极接点220,且进一步包括诸如栅极接点230-r(其中r=1~6)的栅极接点(或称“vg”)230以及诸如源极/漏极通孔插塞(via plug)240-s(其中s=1~10)的源极/漏极通孔插塞(或称“vd”)240。为了简单起见,除了源极/漏极特征213-5~213-8之外,图5中并未标记源极/漏极特征213。栅极接点230被设置于栅极电极210上,并与栅极电极210直接接触。具体来说,栅极接点230-1、230-2、230-3、230-4、230-5、以及230-6分别被设置于栅极电极210-1、210-3、210-4、210-2、210-5、以及210-6上,并与这些栅极电极直接接触。

[0075]

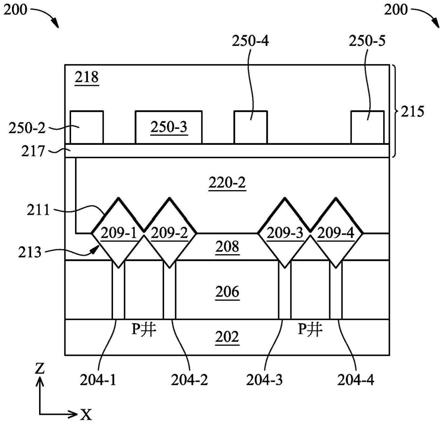

图6a显示沿着图5的aa线段的双端sram单元200的截面图。图6b显示沿着图5的bb线段的双端sram单元200的截面图。一并参照图5、图6a及图6b,双端sram单元200包括基板202,基板202上形成有主动区204。在此实施例中,主动区204是连接到基板202的鳍片主动区。双端sram单元200还包括位在基板202上并隔离各个主动区204的隔离结构206。

[0076]

基板202可包括:硅基板(例如:硅晶圆)或诸如锗的其他半导体;化合物半导体,包括碳化硅、氮化镓、砷化镓、磷化镓、磷化铟、砷化铟、以及锑化铟;合金半导体,包括硅锗、砷磷化镓(gallium arsenide phosphide)、磷化铝铟、砷化铝镓、砷化镓铟、磷化镓铟、以及砷磷化镓铟(gallium indium arsenide phosphide);或其组合。在一些实施例中,基板202可包括绝缘层上硅(silicon-on-insulator,soi)基板。基板202包括各种掺杂结构(例如:p井或n井),且可被应变(strained)或应力(stressed)以提高性能。

[0077]

鳍片状的主动区204可包括一或多种半导体材料,例如硅、锗或其他合适的半导体材料。在一个实施例中,鳍片状的主动区204可包括两种不同半导体材料交替堆叠的薄层,例如交替堆叠的硅薄层与硅锗薄层。鳍片状的主动区204可另外包括诸如磷或砷的n型掺杂物,或是诸如硼或铟的p型掺杂物。

[0078]

隔离结构206可包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fluoride-doped silicate glass,fsg)、低k值介电材料、及/或其他合适的绝缘材料。隔离结构206可为浅沟槽隔离(shallow trench isolation,sti)特征。其他隔离结构,例如场氧化物(field oxide)、硅局部氧化(local oxidation of silicon,locos)、及/或其他合适的结构也是合适的。隔离结构206可包括多层结构,例如具有与鳍片状的主动区204相邻的一或多个热氧化衬垫层(liner layer)。

[0079]

在本实施例中,源极/漏极特征213包括掺杂的半导体层209,且进一步包括位在掺杂的半导体层209上的硅化(silicide)层211。图6a显示范例性掺杂的半导体层209-1~209-4,其中在本文中,掺杂的半导体层209-1~209-4可统称为掺杂的半导体层209。相邻的半导体层209可以合并(如图6a所示),或者可以是分开的。掺杂的半导体层209可包括具有n型掺杂物的外延生长硅、具有p型掺杂物的外延生长硅锗、或是其他合适的材料。硅化层211可包括硅化钛、硅化镍、硅化钴、硅化钨、或其他硅化物。

[0080]

每个栅极电极210包括位在栅极介电层上的栅极金属层。图6b显示栅极电极210-2及210-3,其中栅极电极210-2包括位在栅极介电层210-2d之上的栅极金属层210-2m,而栅极电极210-3包括位在栅极介电层210-3d上的栅极金属层210-3m。栅极介电层210-2d以及210-3d可包括一或多种高k值介电材料(或一或多层高k值介电材料),例如氧化硅铪(hafnium silicon oxide,hfsio)、氧化铪(hfo2)、氧化铝(al2o3)、氧化锆(zro2)、氧化镧(la2o3)、氧化钛(tio2)、氧化钇(y2o3)、钛酸锶(srtio3)、或其组合。栅极金属层210-2m以及

210-3m可包括一或多个金属层,例如功函数金属层(work function metal layer)、导电阻挡层(conductive barrier layer)、以及金属填充层。根据装置的类型(pfet或nfet),功函数金属层可为p型或n型功函数层。p型功函数层可选自但不限于:氮化钛(tin)、氮化钽(tan)、钌(ru)、钼(mo)、钨(w)、铂(pt)、或其组合。n型功函数层可选自但不限于:钛(ti)、铝(al)、碳化钽(tac)、碳氮化钽(tacn)、氮硅化钽(tasin)、氮硅化钛(tisin)、或其组合。金属填充层可包括铝(al)、钨(w)、钴(co)、及/或其他合适的材料。

[0081]

双端sram单元200还包括位在隔离结构206上且覆盖源极/漏极特征213及栅极电极210的介电层208。介电层208可包括一或多种介电材料,例如氮化硅、氧化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fsg)、低k值介电材料、及/或其他合适的绝缘材料。源极/漏极接点220(图6a及图6b所示的源极/漏极接点220-2)被设置于介电层208中。栅极接点230(图6b所示的栅极接点230-2)亦被设置于介电层208中。在一个实施例中,源极/漏极接点220-2的至少一部分,被设置在与栅极接点230-2的顶部表面相同或较低的垂直层位(vertical level,或称垂直高度)处。在另一个实施例中,整个源极/漏极接点220-2,被设置在与栅极接点230-2的顶部表面相同或较低的垂直层位处。

[0082]

在本实施例中,源极/漏极接点220-2的一部分以及栅极接点230-2的一部分,自基板202的顶部表面起,垂直地处于同一水平,并沿着方向y对准(见图5的线段b-b及图6b)。栅极接点230-2与源极/漏极接点220-2之间沿着方向y之间隔s1,小于193nm浸润式光刻的单次曝光所能获得的分辨率,但等于或大于euv光刻所能获得的分辨率。举例来说,在一实施例中,间隔s1被制造为小于40nm,例如小于20nm或小于10nm。在一些设计中,在源极/漏极特征213-5~213-8上的源极/漏极接点在接点层位处被制成数个分隔的片状,以避免与栅极接点230-2短路。具体来说,在那些设计中,源极/漏极特征213-5~213-8上的源极/漏极接点并未延伸到区域nc(由图5中的虚线框表示)中,区域nc是自栅极接点230-2沿着方向y朝栅极电极210-2延伸的区域。为了连接源极/漏极特征213-5~213-6与源极/漏极特征213-7~213-8,这些设计将需要自更高的互连层进行选路。在本实施例中,源极/漏极接点220-2及栅极接点230-2是使用诸如euv光刻的先进光刻所定义。因此,即使是在间隔s1小于40nm(例如:小于20nm)时,源极/漏极接点220-2仍旧可以延伸通过区域nc,且不必担心与栅极接点230-2短路。这有利地简化了双端sram单元200的互连选路、降低了源极/漏极互连电阻、并释放了金属层选路资源用于其他信号,例如电源、接地、位元线、以及字线。上面关于源极/漏极接点220-2与栅极接点230-2的讨论,同样适用于源极/漏极接点220-9与栅极接点230-5。源极/漏极通孔插塞240被设置在各种源极/漏极接点220上。源极/漏极通孔插塞240可被设置在与栅极接点230相同的垂直层位处,或是高于栅极接点230的垂直层位处。

[0083]

图7是根据本实施例所示,双端sram单元200的布局图。图7中的布局包括如上所述的主动区204、栅极电极210、源极/漏极接点220、栅极接点230、以及源极/漏极接点插塞240,且进一步包括诸如金属线250-1~250-11的金属线250。为了简单起见,图7中并未标出所有特征。在本实施例中,金属线250-1、250-3、250-5、250-7、250-9、和250-11,以及金属线250-2、250-4、250-6、250-8、和250-10,是在双重图案化工艺中由不同的图案化工艺所定义的(一者具有颜色b,而另一者具有颜色a)。替代性地,金属线250-1~250-11可由单一图案化工艺来定义。金属线250-1~250-11大致上沿着方向y呈纵向指向。

[0084]

金属线250-1被设置在栅极接点230-1上并连接到栅极接点230-1,且金属线250-1

4。金属线270大致上沿着方向x呈纵向指向。通孔260及金属线270被设置在互连层215上方的互连层(未图示)中,例如金属-2互连层。具体来说,金属线270-2及270-3是端a的字线选路的一部分。可使用双重图案化工艺来定义金属线270,其中金属线270-1及270-4在一个图案化工艺中被定义,而金属线270-2及270-3在另一个图案化工艺中被定义。替代性地,可以使用单一图案化工艺来定义金属线270。为了简单起见,图9中并未标出所有特征。

[0088]

图10是根据本实施例所示,双端sram单元200的布局图。图10中的布局包括图3、图4、图5、图7、以及图9所示的所有特征,且进一步包括分别设置在第二层位的金属线270-1及270-4上的第二层位的通孔280-1及280-2,以及包括设置在第二层位的通孔280-1及280-2上的第三层位的金属线290-1及290-2。第三层位的金属线290-1及290-2大致上沿方向y呈纵向指向。图10中的布局还包括第四层位的金属线300-1,第四层位的金属线300-1是端b的字线选路的一部分。经由第三层位的通孔(未图示)进行自第四层位的金属线300-1到较低层位(例如金属线290-1及290-2)的连接。

[0089]

尽管并非旨于限制,但本公开提供诸多益处。举例来说,本公开提供了用于双端sram单元的紧凑设计。在此设计中,同一个端(端a或端b)的传输闸晶体管及下拉晶体管的源极/漏极特征,经由单一源极/漏极接点连接,而无需使用更高层位的选路资源。该源极/漏极接点与附近的栅极接点之间的空间可以做得非常小。这导致在接触层位的布局非常紧凑。此外,由于接触层位上的简单选路,因此释放了较高互连层(例如:金属-1层)上的一些选路资源以用于其他信号,例如电源线、接地线、位元线、以及字线,进而降低这些线路上的电阻。具体来说,可将接地线做得特别宽以降低接地电阻,进而提高双端sram单元的性能。

[0090]

在一个范例性实施方式中,本公开直指一种双端sram。上述双端sram包括基板;第一主动区及第二主动区,位于基板上,并大致上沿着第一方向呈纵向指向;第一栅极电极及第二栅极电极,位于基板上,并大致上沿着垂直于第一方向的第二方向呈纵向指向。第一栅极电极接合第一主动区以形成上述双端sram的第一传输闸晶体管,而第二栅极电极接合第二主动区以形成上述双端sram的第二传输闸晶体管。上述双端sram还包括第一栅极接点,被设置于第一栅极电极上,并与第一栅极电极电性连接,以及包括第一源极/漏极接点,大致上沿着第二方向呈纵向指向。第一源极/漏极接点直接接触第一传输闸晶体管的源极/漏极特征以及第二传输闸晶体管的源极/漏极特征。第一栅极接点的一部分及第一源极/漏极接点的一部分自基板的一顶部表面处于相同的垂直层位,且沿着第一方向对准。

[0091]

在双端sram的一个实施例中,沿着第一方向自第一栅极接点的一部分至第一源极/漏极接点的一部分的距离小于40纳米。在进一步的实施例中,上述距离小于20纳米。

[0092]

在一个实施例中,上述双端sram还包括第三主动区及第四主动区,位于基板上并大致上沿着第一方向呈纵向指向。第一栅极电极接合第三主动区以形成上述双端sram的第三晶体管。第二栅极电极接合第四主动区以形成上述双端sram的第四晶体管。第一源极/漏极接点被设置于第三晶体管的源极/漏极特征以及第四晶体管的源极/漏极特征上。

[0093]

在双端sram的一个实施例中,第一源极/漏极接点的至少一部分,被以与第一栅极接点的顶部表面相同或更低的垂直层位设置。

[0094]

在另一个实施例中,上述双端sram还包括第一互连层,位于第一栅极接点及第一源极/漏极接点上。第一互连层包括大致上沿着第一方向呈纵向指向的第一金属线及第二金属线,第一金属线直接位于第一栅极接点上并与第一栅极接点连接,而第二金属线直接

位于第二主动区上。在进一步的实施例中,上述双端sram还包括第三栅极电极,位于基板上并大致上沿着第二方向呈纵向指向。第三栅极电极接合第一主动区以形成上述双端sram的第一下拉晶体管,且第三栅极电极接合第二主动区以形成上述双端sram的第二下拉晶体管。上述双端sram还包括第二源极/漏极接点,大致上沿着第二方向呈纵向指向。第二源极/漏极接点直接接触第一下拉晶体管的源极/漏极特征以及第二下拉晶体管的源极/漏极特征。上述双端sram还包括通孔插塞,设置于第二源极/漏极接点与第二金属线之间,并电性连接第二源极/漏极接点及第二金属线。在进一步的实施例中,双端sram还包括金属对金属通孔插塞,设置于第一金属线上,以及包括第三金属线,直接设置于金属对金属通孔插塞上,并大致上沿着第二方向呈纵向指向。

[0095]

在双端sram的一些实施例中,每个第一传输闸晶体管的源极/漏极特征以及第二传输闸晶体管的源极/漏极特征,包括一半导体层上的一硅化特征,其中第一源极/漏极接点直接接触上述硅化特征。

[0096]

在双端sram的一些实施例中,第一主动区及第二主动区包括多个鳍片主动区,而第一传输闸晶体管及第二传输闸晶体管包括多个finfet。

[0097]

在另一个范例性实施方式中,本公开直指一种双端sram单元。上述双端sram单元包括位于基板上的第一传输闸晶体管以及第二传输闸晶体管。第一传输闸晶体管包括第一栅极电极的一部分,第一栅极电极接合第一主动区的一部分。第二传输闸晶体管包括第二栅极电极的一部分,第二栅极电极接合第二主动区的一部分。第一栅极电极以及第二栅极电极连接至上述双端sram单元的不同字线。第一主动区及第二主动区大致上沿着第一方向呈纵向指向。第一栅极电极以及第二栅极电极大致上沿着垂直于第一方向的第二方向呈纵向指向。上述双端sram单元还包括第一栅极接点,被设置于第一栅极电极上,以及包括第一源极/漏极接点,大致上沿着第二方向呈纵向指向。第一源极/漏极接点被设置于第一传输闸晶体管的源极/漏极特征以及第二传输闸晶体管的源极/漏极特征两者上。第一源极/漏极接点被以相同于或低于第一栅极接点的一顶部表面的垂直层位设置。

[0098]

在双端sram单元的一个实施例中,第一传输闸晶体管的源极/漏极特征亦为上述双端sram单元的第一下拉晶体管的源极/漏极特征,而第二传输闸晶体管的源极/漏极特征亦为上述双端sram单元的第二下拉晶体管的源极/漏极特征。

[0099]

在双端sram单元的一个实施例中,第一栅极接点的一部分与第一源极/漏极接点的一部分,自基板的顶部表面处于相同的垂直层位,且沿着第一方向以小于20纳米彼此间隔。

[0100]

在一个实施例中,上述双端sram单元还包括第一金属线以及第二金属线,大致上沿着第一方向呈纵向指向。第一金属线直接位于第一栅极接点上并与第一栅极接点连接。第二金属线直接位于第二主动区上且宽于第二主动区。在进一步的实施例中,上述双端sram单元还包括互连通孔插塞,被设置于第一金属线上,以及包括第三金属线,大致上沿着第二方向呈纵向指向,并被直接设置于互连通孔插塞上。第三金属线为上述双端sram单元的字线的其中一个。在另一个实施例中,上述双端sram单元还包括第二栅极接点,被设置于第二栅极电极上,以及包括第三金属线,大致上沿着第一方向呈纵向指向,其中第三金属线直接位于第二栅极接点上并与第二栅极接点连接。

[0101]

在双端sram单元的一个实施例中,第二金属线宽于第一金属线。

[0102]

在又一个范例性实施方式中,本公开直指双端sram单元的一种布局。上述布局包括位于p型井上的第一主动区、第二主动区、第三主动区、以及第四主动区,其中每个第一主动区、第二主动区、第三主动区、以及第四主动区大致上沿着第一方向呈纵向指向。上述布局还包括第一栅极电极,位于第一主动区及第二主动区上;第二栅极电极,位于第三主动区及第四主动区上;以及第三栅极电极,位于第一主动区、第二主动区、第三主动区、以及第四主动区上。每个第一栅极电极、第二栅极电极、以及第三栅极电极大致上沿着与第一方向垂直的第二方向呈纵向指向。上述布局还包括源极/漏极接点特征,以俯视图来看被设置于第一栅极电极与第三栅极电极之间,以及第二栅极电极与第三栅极电极之间。源极/漏极接点特征接触第一主动区上的第一源极/漏极特征、第二主动区上的第二源极/漏极特征、第三主动区上的第三源极/漏极特征、以及第四主动区上的一第四源极/漏极特征。在一个实施例中,上述布局还包括被设置于第一栅极电极上的栅极接点。在进一步的实施例中,沿着第一方向自栅极接点至源极/漏极接点的距离小于40纳米。

[0103]

前述内文概述多项实施例的特征,如此可使于本技术领域中技术人员优选地了解本公开的实施方式。本技术领域中技术人员应当理解他们可轻易地以本公开为基础设计或修改其他工艺及结构,以完成相同的目的及/或达到与本文介绍的实施例或范例相同的优点。本技术领域中技术人员亦需理解,这些等效结构并未脱离本公开的构思及范围,且在不脱离本公开的构思及范围的情况下,可对本公开进行各种改变、置换以及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。