1.本公开涉及一种制品、一种集成电路及一种制造集成电路的方法。

背景技术:

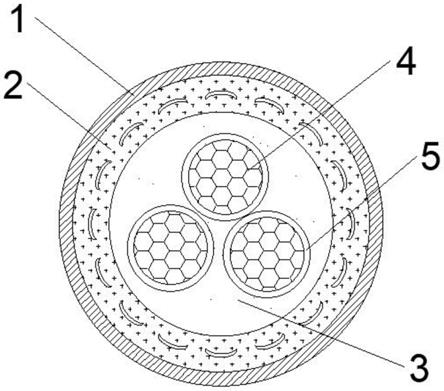

2.图1例示了在堆叠芯片的制造中使用的常规结构100。例如,结构100包括:第一层,该第一层包括多个处理元件(pe)102和邻接的金属层104;以及第二层,该第二层包括联接至邻接的金属层108的相同数量的存储元件(memory element)(me)106。第一层和第二层通过例如混合键合(hybrid bonding)层110彼此键合。

3.相邻的处理元件102中的各对相邻的处理元件通过各自的划线112彼此分隔开,并且相邻的存储元件106中的各对相邻的存储元件通过各自的划线114彼此分隔开。作为制造工艺的一部分,沿着划线112和划线114切割结构100,以产生独立的单元(例如,独立的堆叠芯片),芯片中的各个芯片由单个块组成,该单个块包括处理元件102之一和存储元件106之一。这已知为基于块的设计。

4.划线112和划线114的一个目的是保护处理元件102和存储元件106中的电路和其它部件在切割工艺期间不受损坏。因此,被划线112和划线114占据的区域不包含连接至处理元件102或存储元件106的布线或其它部件。因此,各个处理元件102与其相邻的处理元件隔离开,并且类似地,各个存储元件106与其相邻的存储元件隔离开。

5.每个芯片包括一个块(单个处理元件和单个存储元件)的芯片在诸如电信器件的器件中很有用。还存在需要比由单块芯片提供的计算和存储资源更大的计算和存储资源的其它更复杂的应用(例如,数据中心)。在那些更复杂的应用中,每个芯片包括超过一个块的更大芯片将是有利的。然而,如上所述,在彼此隔离开的独立的块之间不可能进行块间通信。因此,每个芯片包括单个块的基于块的设计无法轻松扩展到需要更大芯片的应用。

技术实现要素:

6.根据本发明的实施方式提供了针对上述问题的解决方案。根据本发明的实施方式涉及更大的多块芯片,该更大的多块芯片包括允许在划线周围或绕过划线并因此在块之间进行通信的特征。根据本发明的实施方式还涉及允许将基于块的堆叠芯片扩展到更大的多块芯片的制造工艺。

7.在实施方式中,堆叠芯片或集成电路包括第一层,所述第一层包括第一器件和第二器件。例如,所述第一器件可以是处理元件,并且所述第二器件可以是处理元件。第一划线位于所述第一器件与所述第二器件之间并且将所述第一器件与所述第二器件分隔开。导电连接部(connection)(块间连接部)横跨(traverse)所述划线并且联接至所述第一器件和所述第二器件。

8.在实施方式中,所述堆叠芯片或集成电路还包括第二层,所述第二层包括第三器件和第四器件。例如,所述第三器件可以是存储元件,并且所述第四器件可以是存储元件。混合键合层位于所述第一层与所述第二层之间。第二划线位于所述第三器件与所述第四器

件之间并且将所述第三器件与所述第四器件分隔开。在这些实施方式中,所述块间连接部位于所述第一层与所述第二层之间。

9.在一实施方式中,所述块间连接部是利用片上网络(noc)互连架构层实现的。在另一实施方式中,所述块间连接部是利用后道工序(beol)层实现的。在又一实施方式中,所述块间连接部是利用重新分布层(rdl)实现的。在再一实施方式中,所述块间连接部位于所述混合键合层与所述第二层之间,并且是利用层(例如,noc互连架构层或beol层)并且还使用所述混合键合层实现的。

10.在实施方式中,所述堆叠芯片或集成电路还包括位于所述第一器件与所述第二器件之间的第三划线,并且金属部分(volume of metal)位于所述第一划线与所述第三划线之间。在这些实施方式中,所述块间连接部包括从所述第一层的第一金属层穿过所述混合键合层、所述第二层的第一金属层、所述混合键合层、所述金属部分、所述混合键合层、所述第二层的第二金属层和所述混合键合层到所述第一层的第二金属层的路径。

11.因此,根据本发明的实施方式使得能够在划线周围以及在块之间进行通信,并且允许将基于块的堆叠芯片扩展到更大的多块芯片。

12.在阅读了各个附图中例示的实施方式的以下详细描述之后,本领域普通技术人员将认识到本发明的各种实施方式的这些目的和优点以及其它目的和优点。

附图说明

13.并入本说明书中并形成本说明书的一部分的附图例示了本公开的实施方式并且与详细描述一起用于解释本公开的原理,在附图中,相同的附图标记表示相同的元件。

14.图1是例示了在基于块的集成电路或芯片的制造中使用的常规结构的框图。

15.图2、图3、图4、图5和图6是根据本发明的实施方式中的多块堆叠芯片的框图。

16.图7是根据本发明的实施方式中的用于制造类似于图2至图6中的多块堆叠芯片的多块堆叠芯片的方法的示例的流程图。

具体实施方式

17.现在将详细参照本公开的各种实施方式,在附图中例示了所述各种实施方式的示例。尽管结合这些实施方式进行了描述,但是将理解,所述实施方式并不旨在将本公开限制于这些实施方式。相反,本公开旨在涵盖可以包括在由所附权利要求限定的本公开的精神和范围内的另选例、修改例和等同例。此外,在本公开的以下详细描述中,阐述了许多具体细节以提供对本公开的透彻理解。然而,应当理解,可以在不具有这些具体细节的情况下实践本公开。在其它情况下,未详细描述公知方法、过程、部件和电路,以免不必要地模糊本公开的各方面。

18.在用于制造半导体器件的过程、逻辑块、处理以及操作的其它符号表示方面呈现了以下详细描述的一些部分。这些描述和表示是半导体器件制造领域的技术人员用来将其工作的实质最有效地传达给本领域其他技术人员的手段。在本技术中,过程、逻辑块、工艺等被认为是导致期望结果的步骤或指令的自洽序列。这些步骤是需要对物理量进行物理操纵的步骤。然而,应记住,所有这些和类似术语应与适当的物理量相关联,并且仅仅是应用于这些量的方便标签。除非从下面的讨论中另外明确指出,否则应理解,贯穿本技术,利用

诸如“形成”、“连接”、“键合”、“沉积”等的术语的讨论是指半导体器件制造的动作和工艺(例如,图7的流程图700)。“层”可以包括一个或更多个层:它可以指单个层,或者可以指包括其它层(子层)的层。结构、芯片、集成电路等在本文中可以称为制品(article of manufacture)。

19.应理解,附图不一定按比例绘制,并且仅示出了所描绘的器件和结构的一部分以及形成那些结构的各个层。为了简化讨论和例示,虽然实际上可以存在或形成超过一个或两个的器件或结构,但是可以仅描述一个或两个器件或结构。而且,尽管讨论了某些元件、部件和层,但是根据本发明的实施方式不限于那些元件、部件和层。例如,除了所讨论的元件、部件、层等之外,还可以存在其它元件、部件、层等。

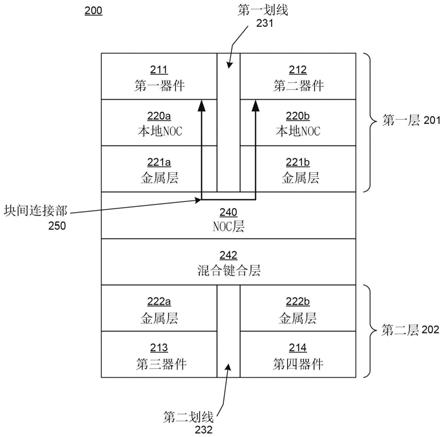

20.图2是根据本发明的实施方式中的多块芯片或多块集成电路(在本文中称为堆叠芯片200)的框图。

21.堆叠芯片200包括第一层201,该第一层201包括第一器件211和第二器件212。第一器件211可以是但不限于第一处理元件,并且第二器件212可以是但不限于第二处理元件。通常,处理元件例如是能够执行一个或更多个处理的通用处理器内核。处理元件可以是但不限于中央处理单元(cpu)。

22.第一层201还包括本地(local)片上网络(noc)架构层220a和220b以及金属层221a和221b。本地noc架构层220a和220b将相邻处理元件中的部件互连。即,例如,本地noc架构层220a将第一器件211中的部件彼此连接。一般而言,noc架构层包括二维或三维金属丝网拓扑。

23.第一划线231位于第一器件211与第二器件212之间并且将第一器件与第二器件分隔开。第一划线231也延伸进入并穿过noc架构层220a和220b以及金属层221a和221b。

24.在实施方式中,堆叠芯片200还包括第二层202,该第二层202包括第三器件213和第四器件214。第三器件213可以是但不限于存储元件,并且第四器件214可以是但不限于存储元件。存储元件可以是但不限于动态随机存取存储器(dram)或静态ram(sram)。另选地,第三器件213和/或第四器件214可以是处理元件。

25.第二层202还包括金属层222a和222b。第二划线232位于第三器件213与第四器件214之间并且将第三器件与第四器件分隔开。第二划线232也延伸进入并穿过金属层222a和222b。

26.混合键合层242位于第一层201与第二层202之间。通常,混合键合描述了这样一种类型的键合,即,其将金属互连与某种其它形式的键合(例如,硅热键合(silicon fusion bonding))相结合。即,混合键合可以包括例如允许通过混合键合而键合的层之间的通信的布线。因此,例如,第一器件211与第三器件213之间的通信可以穿过混合键合层242发生。

27.在图2的实施方式中,导电连接部(块间连接部250)横跨第一划线231(绕过第一划线231;跨越第一划线231或在第一划线231周围延伸)并且连接至第一器件211和第二器件212。块间连接部250在划线231下方(相对于图2中的堆叠芯片200的定向)位于第一层201与第二层202之间。具体地,块间连接部250位于混合键合层242与第一层201之间,并且使用第二或全局noc互连架构层240来实现,该第二或全局noc互连架构层240包括连接第一器件211和第二器件212的布线。

28.块间连接部250因此允许第一器件211与第二器件212之间的通信(例如,电信号的

交换)。第一层201中的其它器件可以类似地连接:例如,可以经由横跨第二器件与第三器件之间的划线的另一块间连接部将第三器件连接至第二器件212等。

29.图3是根据本发明的实施方式中的多块芯片或多块集成电路(在本文中称为堆叠芯片300)的框图。

30.与图2的堆叠芯片200相似,堆叠芯片300包括横跨第一划线231并且连接至第一器件211和第二器件212的导电连接部(块间连接部350)。

31.与堆叠芯片200相比,使用后道工序(beol)层340来实现块间连接部350,该beol层340包括连接第一器件211和第二器件212的布线。

32.因此,块间连接部350允许第一器件211与第二器件212之间的通信(例如,电信号的交换)。第一层201中的其它器件可以类似地连接。

33.此外,与noc互连架构层240相比,beol层340(和块间连接部350)仅在堆叠芯片旨在用于需要多块芯片的更复杂的用途(例如,数据中心)时才可以添加至该堆叠芯片。换句话说,如果终端用户(例如,客户)打算在仅需要单块芯片的器件中使用堆叠芯片,则在制造芯片时或在制造第一层201中的器件时,不需要形成beol层340。另一方面,如果终端用户打算在需要多块芯片的器件中使用堆叠芯片,则在制造芯片时或在制造第一层201中的器件时形成beol层340。

34.图4是根据本发明的实施方式中的多块芯片或多块集成电路(在本文中称为堆叠芯片400)的框图。

35.分别类似于图2的堆叠芯片200和图3的堆叠芯片300,堆叠芯片400包括横跨第一划线231并且连接至第一器件211和第二器件212的导电连接部(块间连接部450)。

36.与堆叠芯片200和300相比,块间连接部450是使用重新分布层(rdl)440实现的,该rdl 440包括连接第一器件211和第二器件212的布线。

37.因此,块间连接部450允许第一器件211与第二器件212之间的通信(例如,电信号的交换)。第一层201中的其它器件可以类似地连接。

38.类似于图3的beol层340,rdl 440(和块间连接部450)仅在堆叠芯片旨在用于需要多块芯片的更复杂的用途(例如,数据中心)时才可以添加至该堆叠芯片。

39.图5是根据本发明的实施方式中的多块芯片或多块集成电路(在本文中称为堆叠芯片500)的框图。

40.分别与图2的堆叠芯片200和图3的堆叠芯片300相比,堆叠芯片500包括块间连接部550,该块间连接部550是使用位于第二层202与混合键合层242之间的层540实现的。层540可以是noc架构层或beol层。块间连接部550使用层540中的布线和混合键合层242中的布线来横跨第一划线231并且连接第一器件211和第二器件212。

41.因此,块间连接部550允许第一器件211与第二器件212之间的通信(例如,电信号的交换)。第一层201中的其它器件可以类似地连接。

42.当实现为beol层时,层540(和块间连接部550)仅在堆叠芯片旨在用于需要多块芯片的更复杂的用途(例如,数据中心)时才可以添加至该堆叠芯片。换句话说,如果终端用户打算在仅需要单块芯片的器件中使用堆叠芯片,则在制造芯片时或在制造第二层202中的器件时,不需要形成(beol)层540。另一方面,如果终端用户打算在需要多块芯片的器件中使用堆叠芯片,则在制造芯片时或在制造第二层202中的器件时形成(beol)层540。

43.图6是根据本发明的实施方式中的多块芯片或多块集成电路(在本文中称为堆叠芯片600)的框图。

44.堆叠芯片600包括位于第一器件211与第二器件212之间以及位于第一划线231与第二器件212之间的第三划线633。金属部分660位于第一划线231与第三划线633之间。部分(volume)670可以包含硅,但是不被使用。

45.块间连接部650横跨划线231、232和633并且连接第一器件211和第二器件212。更具体地,第一器件211与第二器件212之间的块间连接部650包括从第一层201中的金属层221a、穿过混合键合层242、穿过第二层202中的金属层222a、往回穿过混合键合层242、穿过金属部分660、往回穿过混合键合层242、穿过第二层202中的金属层222b、往回穿过混合键合层242到第一层201中的金属层221b的路径。

46.因此,块间连接部650允许第一器件211与第二器件212之间的通信(例如,电信号的交换)。第一层201中的其它器件可以类似地连接。

47.总之,根据本发明的实施方式使得能够跨越划线并且在块之间进行通信,并且允许将基于块的堆叠芯片扩展到更大的多块芯片。

48.图7是根据本发明的实施方式中的用于制造多块堆叠芯片(类似于以上结合图2至图6描述的多块堆叠芯片)的方法或工艺的示例的流程图700。

49.在图7中,被描述为单独的框的操作可以在同一工艺步骤中(即,在相同的时间间隔内,在前一工艺步骤之后并且在下一工艺步骤之前)组合并执行。而且,可以以与以下描述的顺序不同的顺序执行操作。此外,可以与本文讨论的工艺和步骤一起执行制造工艺和步骤;即,在本文示出和描述的步骤之前、之间和/或之后可以存在许多工艺步骤。重要的是,根据本发明的实施方式可以结合这些其它(也许是常规的)工艺和步骤来实现,而不会显著干扰所述工艺和步骤。一般而言,根据本发明的实施方式可以代替常规工艺的一部分,而不会显著影响外围工艺和步骤。

50.进一步参照图2至图6描述图7。框702和框704涉及图2至图6的实施方式。在框702,在基板(未示出)上形成包括第一器件211和第二器件212的第一层201。

51.在框704,形成第一划线231。第一划线231位于第一器件211与第二器件212之间并且将第一器件与第二器件分隔开。

52.在框706,在图2至图4的实施方式中,形成导电块间连接部(连接部250、350或450)。块间连接部250、350、450横跨第一划线231并且连接第一器件211和第二器件212。

53.在一些实施方式中(例如,图5和图6的实施方式,以及可选地图2至图4的实施方式),该方法还包括框708、框710和框712的操作。

54.在框708,形成包括第三器件213和第四器件214的第二层202。

55.在框710,形成第二划线232。第二划线232位于第三器件213与第四器件214之间并且将第三器件与第四器件分隔开。

56.在框712,在第一层201与第二层202之间形成混合键合层242。

57.在一些实施方式中(例如,图5的实施方式),在框714,在混合键合层242与第二层202之间形成层540。层540包括穿过混合键合层242而连接至第一器件211和第二器件212的布线,从而形成块间连接部550。块间连接部550横跨第一划线231并且连接第一器件211和第二器件212。

58.在其它实施方式中(例如,图6的实施方式),在框716,在第一器件211与第二器件212之间以及在第一划线231与第二器件212之间形成第三划线633,并且在第一划线231与第三划线633之间沉积金属部分660。由此形成块间连接部650,该块间连接部650包括上面在图6的讨论中描述的路径。块间连接部650横跨第一划线231(以及第三划线633)并且连接第一器件211和第二器件212。

59.尽管前述公开使用特定框图、流程图和示例阐述了各种实施方式,但是本文中描述和/或例示的各个框图部件、流程图步骤、操作和/或部件可以使用各种硬件配置、软件配置或固件配置(或其任何组合)单独地和/或共同地实现。另外,包含在其它部件内的部件的任何公开都应视为示例,因为可以实现许多其它架构来实现相同功能。

60.本文描述和/或例示的工艺参数和步骤顺序仅通过示例的方式给出,并且可以根据需要改变。例如,尽管可以以特定顺序示出或讨论本文中例示和/或描述的步骤,但是不一定必须以例示或讨论的顺序来执行这些步骤。本文描述和/或例示的各种示例方法还可以省略本文描述或例示的步骤中的一个或更多个步骤,或者除了所公开的步骤之外还包括附加步骤。

61.尽管已经以特定于结构特征和/或方法动作的语言描述了主题,但是应当理解,本公开中限定的主题不必限于上述特定特征或动作。相反,以上描述的特定特征和动作被公开为实现本公开的示例形式。

62.因此描述了根据本发明的实施方式。尽管已经在特定实施方式中描述了本公开,但是应理解,本发明不应被解释为受这些实施方式的限制,而应根据所附权利要求书来解释。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。