1.本公开涉及一种显示设备,并且更具体地,涉及一种电平偏移电路及包括其的源极驱动器。

背景技术:

2.通常,要求显示设备的源极驱动器在其源输出级中具有低电阻,以便以高速显示具有高分辨率的图像。为此,已知的源极驱动器包括使用多路复用器的输出电路,该多路复用器由在高电压范围内操作的高压元件组成。

3.从源极驱动器的芯片尺寸的观点来看,由高压元件组成的多路复用器成为负担。为此,源极驱动器通过采用由在中间电压范围内操作的中间电压元件组成的多路复用器将源输出级保持在低电阻,以减小芯片尺寸。

4.多路复用器需要在高电压范围内摆动的逻辑信号,以减小源输出级的电阻。可以使用带高压元件的电平偏移电路将在高电压范围内摆动的逻辑信号提供给多路复用器。

5.此外,从多路复用器输出至源输出级的源信号也在高电压范围内摆动。因此,可以使用带在高电压范围内操作的高压元件的输入箝位电路和输出箝位电路来输出源信号,并且将源信号的摆动范围箝位至高电压范围。

6.因此,由于使用高压元件来配置电路,所以常规的源极驱动器具有增加芯片尺寸的问题。

技术实现要素:

7.各种实施方式旨在提供一种能够通过仅使用在中间电压范围内操作的中间电压元件来处理具有高电压范围的逻辑信号的电平偏移电路,以及包括其的源极驱动器。

8.在实施方式中,源极驱动器可包括:电平偏移电路,配置为通过偏移第一逻辑信号的电平来输出第二逻辑信号和第三逻辑信号;以及多路复用器,配置为响应于第二逻辑信号和第三逻辑信号将第一源信号或第二源信号传送至第一焊盘或第二焊盘。电平偏移电路可包括:第一电平偏移器,配置为通过偏移第一逻辑信号的电平来输出第一输入信号和第二输入信号;第二电平偏移器,配置为通过偏移第一逻辑信号的电平来输出第三输入信号和第四输入信号;以及输出电路,配置为响应于第二输入信号和第四输入信号输出第二逻辑信号,并响应于第一输入信号和第三输入信号输出第三逻辑信号。

9.在实施方式中,电平偏移电路可包括:第一电平偏移器,配置为通过偏移第一逻辑信号的电平来输出第一输入信号和第二输入信号;第二电平偏移器,配置为通过偏移第一逻辑信号的电平来输出第三输入信号和第四输入信号;以及输出电路,配置为响应于第二输入信号和第四输入信号输出第二逻辑信号,并响应于第一输入信号和第三输入信号输出第三逻辑信号。输出电路可以通过使用在第一电压范围内操作的上拉元件和在第二电压范围内操作的下拉元件来输出各自具有包括第一电压范围和第二电压范围的第三电压范围的第二逻辑信号和第三逻辑信号。

10.根据实施方式,由于仅使用在中间电压范围内操作的中间电压元件来配置能够处理具有高电压范围的逻辑信号的电路,所以可以减小芯片尺寸。

11.此外,由于在工艺中可以省略高电压掩膜层,因此可以降低生产成本。

附图说明

12.图1是根据实施方式的源极驱动器的框图。

13.图2示出根据实施方式的包括电平偏移电路的源极驱动器。

14.图3示出根据实施方式的电平偏移电路的输出电路。

15.图4是示出根据实施方式的电平偏移电路的操作的图。

具体实施方式

16.实施方式旨在提供一种能够通过仅使用在中间电压范围内操作的中间电压元件来处理具有高电压范围的信号的电平偏移电路以及包括其的源极驱动器。

17.在实施方式中,中间电压范围可以定义为由正放大器输出的第一源信号的摆动范围,或者可以定义为由负放大器输出的第二源信号的摆动范围。在这种情况下,第一源信号的摆动范围可以命名为第一电压范围,并且第二源信号的摆动范围可以命名为第二电压范围。

18.在实施方式中,高电压范围可以定义为从第一电压范围的最高电压到第二电压范围的最低电压的电压范围。在这种情况下,高电压范围可以命名为第三电压范围。

19.在实施方式中,中间电压元件可以定义为在第一电压范围或在第二电压范围中操作的元件。

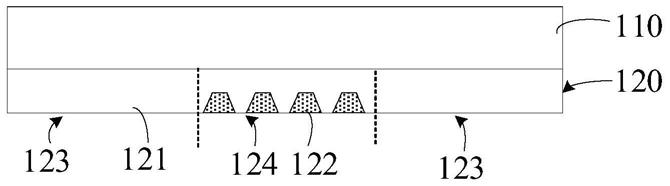

20.图1是根据实施方式的源极驱动器100的框图。在这种情况下,仅示出其中通过一对通道将一对源信号s1和源信号s2提供至显示面板(未示出)的示例,但是这是为了方便描述,并且本公开不限于此。

21.参照图1,源极驱动器100可包括正放大器pamp、负放大器namp、多路复用器mv_mux、电平偏移电路10,以及箝位电路20a和箝位电路20b。

22.正放大器pamp可以放大正数据pdata并将放大的数据输出为第一源信号s1。负放大器namp可以放大负数据ndata并将放大的数据输出为第二源信号s2。在这种情况下,正放大器pamp可以在第一电压范围内操作。负放大器namp可以在第二电压范围内操作。

23.尽管未示出,源极驱动器100还可包括锁存图像数据的锁存电路和通过使用灰度电压将图像数据转换为正数据pdata和负数据ndata的数字模拟转换器。

24.多路复用器mv_mux可以将第一源信号s1输出为第一输出信号out1,并且可以将第二源信号s2输出为第二输出信号out2。可选地,多路复用器mv_mux可将第一源信号s1输出为第二输出信号out2,并且可将第二源信号s2输出为第一输出信号out1。

25.路复用器mv_mux可以基于由电平偏移电路10提供的逻辑信号cs2和逻辑信号cs2b的逻辑电平,分别将第一源信号s1和第二源信号s2输出为第一输出信号out1和第二输出信号out2,或者分别将第一源信号s1和第二源信号s2输出为第二输出信号out2和第一输出信号out1。

26.可以使用在第一电压范围内操作的中间电压元件或在第二电压范围内操作的中

间电压元件来配置多路复用器mv_mux。例如,多路复用器mv_mux可包括将第一源信号s1转换为第一输出信号out1的第一正开关电路、将第一源信号s1转换为第二输出信号out2的第二正开关电路、将第二源信号s2转换为第二输出信号out2的第一负开关电路,以及将第二源信号s2转换为第一输出信号out1的第二负开关电路。

27.此外,多路复用器mv_mux的每个开关电路可包括在中间电压范围内操作并且串联联接的开关。每个开关可以响应于逻辑信号cs2和逻辑信号cs2b而接通或关断。

28.电平偏移电路10可以通过偏移具有低电压电平的第一逻辑信号cs1的电平来向多路复用器mv_mux输出第二逻辑信号cs2和第三逻辑信号cs2b。在这种情况下,第三逻辑信号cs2b可以是第二逻辑信号cs2的反相信号。

29.箝位电路20a和箝位电路20b可以将第一输出信号out1和第二输出信号out2箝位至第一电压范围或第二电压范围。例如,箝位电路20a和箝位电路20b中的每个可包括串联联接的二极管。可以使用在中间电压范围内操作的元件来配置每个二极管。

30.图2示出根据实施方式的包括电平偏移电路10的源极驱动器100。

31.参考图2,电平偏移电路10可包括第一电平偏移器12a、第二电平偏移器12b和输出电路14。

32.第一电平偏移器12a可以通过偏移第一逻辑信号cs1的电平来输出第一输入信号pin和第二输入信号pinb。第二输入信号pinb可以是第一输入信号pin的反相信号。第一电平偏移器12a可以在第一电压范围(即,第一源信号s1的摆动范围)内操作。

33.第二电平偏移器12b可以通过偏移第一逻辑信号cs1的电平来输出第三输入信号nin和第四输入信号ninb。第四输入信号ninb可以是第三输入信号nin的反相信号。第二电平偏移器12b可以在第二电压范围(即,第二源信号s2的摆动范围)内操作。

34.输出电路14可以响应于第二输入信号pinb和第四输入信号ninb来输出第二逻辑信号cs2,并且可以响应于第一输入信号pin和第三输入信号nin来输出第三逻辑信号cs2b。

35.输出电路14可包括在第一电压范围内操作的上拉元件,并且可包括在第二电压范围内操作的下拉元件。此外,输出电路14可以输出第二逻辑信号cs2和第三逻辑信号cs2b,第二逻辑信号cs2和第三逻辑信号cs2b可以在从第一电压范围的最高电压至第二电压范围的最低电压的第三电压范围内摆动。

36.正放大器pamp可以放大正数据pdata并将放大的数据输出为第一源信号s1。负放大器namp可以放大负数据ndata并将放大的数据输出为第二源信号s2。在这种情况下,正放大器pamp可以在第一电压范围内操作,并且负放大器namp可以在第二电压范围内操作。

37.多路复用器mv_mux可以基于第二逻辑信号cs2和第三逻辑信号cs2b的逻辑电平,分别将第一源信号s1和第二源信号s2输出为第一输出信号out1和第二输出信号out2,或者分别将第一源信号s1和第二源信号s2输出为第二输出信号out2和第一输出信号out1。

38.多路复用器mv_mux可包括第一正开关电路、第二正开关电路、第一负开关电路和第二负开关电路。第一正开关电路可以将第一源信号s1作为第一输出信号out1传送至第一焊盘。第二正开关电路可以将第一源信号s1作为第二输出信号out2传送至第二焊盘。第一负开关电路可以将第二源信号s2作为第二输出信号out2传送至第二焊盘。第二负开关电路可以将第二源信号s2作为第一输出信号out1传送至第一焊盘。

39.第一正开关电路、第二正开关电路、第一负开关电路和第二负开关电路中的每个

可包括在中间电压范围内操作且串联联接的开关。每个开关可以配置为至少一个nmos晶体管或pmos晶体管。

40.第一箝位电路20a可以联接在多路复用器mv_mux和第一焊盘之间,并且可以将输出至第一焊盘的第一输出信号out1箝位至第一电压范围或第二电压范围。

41.第二箝位电路20b可以联接在多路复用器mv_mux和第二焊盘之间,并且可以将输出至第二焊盘的第二输出信号out2箝位至第一电压范围或第二电压范围。

42.第一箝位电路20a和第二箝位电路20b可包括串联联接的第一二极管和第二二极管以及串联联接的第三二极管和第四二极管。

43.第一二极管和第二二极管可以将第一输出信号out1或第二输出信号out2箝位至第一电压范围。第三二极管和第四二极管可以将第一输出信号out1或第二输出信号out2箝位至第二电压范围。

44.图3示出根据实施方式的电平偏移电路10的输出电路14。

45.参照图3,电平偏移电路10的输出电路14可包括第一输出电路30,第一输出电路30通过基于第二输入信号pinb和第四输入信号ninb的逻辑电平的上拉操作或下拉操作来输出第二逻辑信号cs2,并且可包括第二输出电路40,第二输出电路40通过基于第一输入信号pin和第三输入信号nin的逻辑电平的上拉操作或下拉操作来输出第三逻辑信号cs2b。

46.第一输出电路30可包括配置为响应于第二输入信号pinb上拉驱动第二逻辑信号cs2的第一上拉电路32、联接在第一上拉电路32和从其输出第二逻辑信号cs2的第一输出级之间的第一分压电路34、配置为响应于第四输入信号ninb下拉驱动第二逻辑信号cs2的第一下拉电路38,以及联接在第一下拉电路38和第一输出级之间的第二分压电路36。

47.第一上拉电路32可包括串联联接的第一pmos元件和第二pmos元件。第一pmos元件和第二pmos元件可具有共同联接的源极端子和体端子(body terminal),并且可具有向其施加第二输入信号pinb的栅极端子。第一上拉电路32可以在第一电压范围内操作。

48.第一下拉电路38可包括串联联接的第一nmos元件和第二nmos元件。第一nmos元件和第二nmos元件可以具有共同联接的源极端子和体端子,并且可以具有向其施加第四输入信号ninb的栅极端子。第一下拉电路38可以在第二电压范围内操作。

49.第一分压电路34可包括串联联接的第三pmos元件和第四pmos元件。第三pmos元件和第四pmos元件中的每个可具有共同联接的源极端子和体端子,并且可具有向其施加接地电压gnd的栅极端子。第一分压电路34可以基于第二输入信号pinb和第四输入信号ninb的逻辑电平在第一电压范围或在第二电压范围内操作。

50.第二分压电路36可包括串联联接的第三nmos元件和第四nmos元件。第三nmos元件和第四nmos元件中的每个可具有共同联接的源极端子和体端子,并且可具有向其施加接地电压gnd的栅极端子。第二分压电路36可以基于第二输入信号pinb和第四输入信号ninb的逻辑电平在第一电压范围或在第二电压范围内操作。

51.第二输出电路40可包括配置为响应于第一输入信号pin上拉驱动第三逻辑信号cs2b的第二上拉电路42、联接在第二上拉电路42和从其输出第三逻辑信号cs2b的第二输出级之间的第三分压电路44、配置为响应于第三输入信号nin下拉驱动第三逻辑信号cs2b的第二下拉电路48,以及联接在第二下拉电路48和第二输出级之间的第四分压电路46。

52.第二上拉电路42可包括串联联接的第一pmos元件和第二pmos元件。第一pmos元件

和第二pmos元件可以具有共同联接的源极端子和体端子,并且可以具有向其施加第一输入信号pin的栅极端子。第二上拉电路42可以在第一电压范围内操作。

53.第二下拉电路48可包括串联联接的第一nmos元件和第二nmos元件。第一nmos元件和第二nmos元件可以具有共同联接的源极端子和体端子,并且可以具有向其施加第三输入信号nin的栅极端子。第二下拉电路48可以在第二电压范围内操作。

54.第三分压电路44可包括串联联接的第三pmos元件和第四pmos元件。第三pmos元件和第四pmos元件中的每个可具有共同联接的源极端子和体端子,并且可具有向其施加接地电压gdnd的栅极端子。第三分压电路44可以基于第一输入信号pin和第三输入信号nin的逻辑电平在第一电压范围或在第二电压范围内操作。

55.第四分压电路46可包括串联联接的第三nmos元件和第四nmos元件。第三nmos元件和第四nmos元件中的每个可具有共同联接的源极端子和体端子,并且可具有向其施加接地电压gndn的栅极端子。第四分压电路46可以基于第一输入信号pin和第三输入信号nin的逻辑电平在第一电压范围或在第二电压范围内操作。

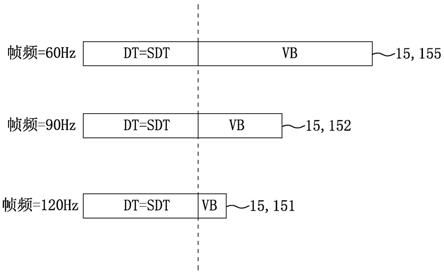

56.图4是示出根据实施方式的电平偏移电路的操作的图。

57.图4示出上拉驱动第二逻辑信号cs2的第一输出电路30的操作和下拉驱动第三逻辑信号cs2b的第二输出电路40的操作。在这种情况下,第二逻辑信号cs2可以具有第一电压范围的最高电压电平,并且第三逻辑信号cs2b可以具有第二电压范围的最低电压电平。

58.如下描述第一输出电路30的操作。第一上拉电路32可以响应于第二输入信号pinb而接通。第一分压电路34可以响应于接地电压而接通。此外,响应于接地电压,可以关断第一输出电路30的第一下拉电路38,并且可以关断第一输出电路30的第二分压电路36。在这种情况下,第二分压电路36可以防止中间电压元件由于具有第一电压范围的最高电压电平的第二逻辑信号cs2而损坏。

59.如下描述第二输出电路40的操作。第二上拉电路42可以响应于第一输入信号pin而关断。第三分压电路44可以响应于接地电压而关断。此外,响应于接地电压,可以接通第二输出电路40的第二下拉电路48,并且可以接通第二输出电路40的第四分压电路46。在这种情况下,第三分压电路44可以防止中间电压元件由于具有第二电压范围的最低电压电平的第三逻辑信号cs2b而损坏。

60.如图1至图4中所示的实施方式,第一电压范围示出为8v至0v,第二电压范围示出为0v至

‑

8v,并且第三电压范围示出为8v至

‑

8v,但是本公开不限于此。

61.如上所述,由于可以仅使用在中间电压范围内操作的中间电压元件来配置能够处理具有高电压范围的信号的电路,因此实施方式能够减小芯片尺寸。此外,由于可以在工艺中省略高电压掩膜层,因此实施方式可以降低生产成本。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。