技术特征:

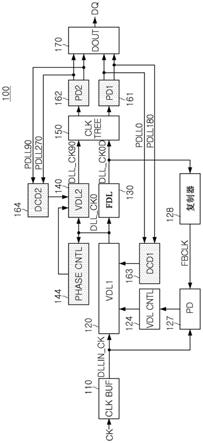

1.一种多相时钟发生器,包括:第一可变延迟线,被配置为接收参考时钟,并且生成延迟时钟;第二可变延迟线,被配置为接收所述延迟时钟,并且生成第二相位延迟时钟;固定延迟线,被配置为接收所述延迟时钟,并且生成第一相位延迟时钟;延迟线控制器,被配置为根据所述参考时钟与反馈时钟之间的第一相位差,控制所述第一可变延迟线;相位控制器,被配置为根据所述延迟时钟与所述第二相位延迟时钟之间的第二相位差,控制所述第二可变延迟线;时钟树,被配置为接收所述第一相位延迟时钟和所述第二相位延迟时钟;第一分相器,被配置为将从所述时钟树接收的所述第一相位延迟时钟进行相位分离,以输出第一分频时钟和第三分频时钟;第二分相器,被配置为将从所述时钟树接收的所述第二相位延迟时钟进行相位分离,以输出第二分频时钟和第四分频时钟;第一占空比检测器,被配置为检测所述第一分频时钟与所述第三分频时钟之间的第一占空比误差;以及第二占空比检测器,被配置为检测所述第二分频时钟与所述第四分频时钟之间的第二占空比误差,其中,所述第一可变延迟线根据所述第一占空比误差被控制,并且所述第二可变延迟线根据所述第二占空比误差被控制。2.根据权利要求1所述的多相时钟发生器,还包括:时钟缓冲器,被配置为缓冲第一相位时钟,并且输出所述参考时钟。3.根据权利要求1所述的多相时钟发生器,还包括:复制器,被配置为从所述固定延迟线接收所述第一相位延迟时钟,并且输出所述反馈时钟;以及相位检测器,被配置为检测来自所述复制器的所述反馈时钟与所述参考时钟之间的第一相位差。4.根据权利要求3所述的多相时钟发生器,其中,所述第一可变延迟线包括:第一粗略延迟线,被配置为接收所述参考时钟,并且根据第一粗略码值延迟所述参考时钟;第一精细延迟线,被配置为接收从所述第一粗略延迟线输出的时钟,并且根据第一精细码值延迟来自所述第一粗略延迟线的时钟;和第一占空比误差校正器,被配置为根据所述第一占空比误差,校正从所述第一精细延迟线接收的时钟。5.根据权利要求4所述的多相时钟发生器,其中,所述延迟线控制器包括:粗略延迟线控制器,被配置为响应于所述第一相位差,输出所述第一粗略码值;以及精细延迟线控制器,被配置为响应于所述第一相位差,输出所述第一精细码值。6.根据权利要求3所述的多相时钟发生器,其中,所述第二可变延迟线包括:第二粗略延迟线,被配置为接收所述延迟时钟,并且根据第二粗略码值延迟所述延迟时钟;

第二精细延迟线,被配置为接收从所述第二粗略延迟线输出的时钟,并且根据第二精细码值延迟从所述第二粗略延迟线输出的时钟;以及第二占空比误差校正器,被配置为根据所述第二占空比误差,校正从所述第二精细延迟线输出的时钟。7.根据权利要求6所述的多相时钟发生器,其中,所述相位控制器根据所述延迟时钟与从所述第二精细延迟线输出的时钟之间的第二相位差,输出所述第二粗略码值和所述第二精细码值。8.根据权利要求1所述的多相时钟发生器,其中,所述第一相位延迟时钟具有与所述参考时钟相同的相位,并且所述第二相位延迟时钟的相位相对于所述参考时钟的相位偏移了90度。9.根据权利要求1所述的多相时钟发生器,其中,所述第一分频时钟具有与所述参考时钟相同的相位,所述第二分频时钟的相位相对于所述参考时钟的相位偏移了90度,所述第三分频时钟的相位相对于所述参考时钟的相位偏移了180度,并且所述第四分频时钟的相位相对于所述参考时钟的相位偏移了270度。10.根据权利要求1所述的多相时钟发生器,还包括:输出缓冲器,被配置为接收所述第一分频时钟、所述第二分频时钟、所述第三分频时钟和所述第四分频时钟,并且输出数据。11.一种包括多相时钟发生器的存储器装置,所述存储器装置包括:延迟锁定环电路,被配置为接收参考时钟,并且输出延迟时钟;时钟树,被配置为接收所述延迟时钟,并且输出所述延迟时钟;固定延迟线,被配置为接收所述延迟时钟,并且输出第一相位延迟时钟;第二可变延迟线,配置为将所述延迟时钟进行相移,以生成第二相位延迟时钟;相位控制器,被配置为根据所述延迟时钟与所述第二相位延迟时钟之间的第二相位差,控制所述第二可变延迟线;第一分相器,被配置为将所述第一相位延迟时钟进行相位分离,以输出第一分频时钟和第三分频时钟;第二分相器,被配置为将所述第二相位延迟时钟进行相位分离,以输出第二分频时钟和第四分频时钟;第一占空比检测器,被配置为检测所述第一分频时钟与所述第三分频时钟之间的第一占空比误差;以及第二占空比检测器,被配置为检测所述第二分频时钟与所述第四分频时钟之间的第二占空比误差,其中,所述延迟锁定环电路根据所述第一占空比误差被控制,并且所述第二可变延迟线根据所述第二占空比误差被控制。12.根据权利要求11所述的存储器装置,其中,所述延迟锁定环电路包括:第一可变延迟线,被配置为接收所述参考时钟,并且生成所述延迟时钟;复制器,被配置为接收从所述第一可变延迟线输出的所述延迟时钟,并且输出反馈时钟;

相位检测器,被配置为检测所述参考时钟与所述反馈时钟之间的第一相位差;以及延迟线控制器,被配置为根据所述第一相位差,控制所述第一可变延迟线。13.根据权利要求12所述的存储器装置,其中,所述第一可变延迟线包括:第一粗略延迟线,被配置为接收所述参考时钟,并且根据第一粗略码值延迟所述参考时钟;第一精细延迟线,被配置为接收从所述第一粗略延迟线输出的时钟,并且根据第一精细码值延迟来自所述第一粗略延迟线的时钟;以及第一占空比误差校正器,被配置为根据所述第一占空比误差,校正来自所述第一精细延迟线的时钟。14.根据权利要求13所述的存储器装置,其中,所述延迟线控制器包括:粗略延迟线控制器,被配置为响应于第一相位差,输出所述第一粗略码值;以及精细延迟线控制器,被配置为响应于第一相位差,输出所述第一精细码值。15.根据权利要求11所述的存储器装置,其中,所述第一分相器和所述第二分相器将接收到的时钟分离为具有180度的相位差。16.一种生成存储器装置的多相时钟的方法,所述方法包括:启动延迟锁定环操作以接收参考时钟并生成延迟时钟;对所述参考时钟执行粗略锁定操作;确定所述粗略锁定操作是否完成;当所述粗略锁定操作完成时,在对应于所述延迟时钟的第一分频时钟与第三分频时钟之间执行第一占空比误差校正操作的同时执行精细锁定操作;将基于所述延迟时钟生成的至少一个相位延迟时钟进行相位分离,以生分相时钟;以及在对应于所述分相时钟的第二分频时钟与第四分频时钟之间执行第二占空比误差校正操作。17.根据权利要求16所述的方法,还包括:在所述粗略锁定操作未完成时,重新执行所述粗略锁定操作。18.根据权利要求16所述的方法,其中,所述相位分离包括:通过固定延迟线输出所述延迟时钟作为第一相位延迟时钟;通过使所述延迟时钟通过可变延迟线生成第二相位延迟时钟;对所述第一相位延迟时钟进行相位分离,以生成所述第一分频时钟和所述第三分频时钟;以及对所述第二相位延迟时钟进行相位分离,以生成所述第二分频时钟和所述第四分频时钟。19.根据权利要求18所述的方法,其中,所述第一相位延迟时钟的相位与所述延迟时钟的相位相同,并且所述第二相位延迟时钟的相位相对于所述延迟时钟的相位偏移了90度。20.根据权利要求18所述的方法,还包括:通过时钟树接收所述第一相位延迟时钟和所述第二相位延迟时钟;以及通过所述时钟树输出所述第一相位延迟时钟和所述第二相位延迟时钟。

技术总结

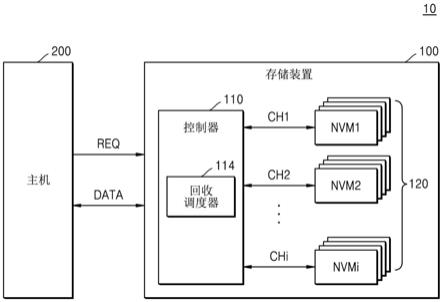

提供了多相时钟发生器、存储器装置和生成多相时钟的方法。该多相时钟发生器包括第一可变延迟线和第二可变延迟线;第一分相器,被配置为将从时钟树输出的第一相位延迟时钟进行相位分离,以输出第一分频时钟和第三分频时钟;第二分相器,被配置为将从时钟树输出的第二相位延迟时钟进行相位分离,以输出第二分频时钟和第四分频时钟;第一占空比检测器,被配置为检测第一分频时钟与第三分频时钟之间的第一占空比误差;以及第二占空比检测器,被配置为检测第二分频时钟与第四分频时钟之间的第二占空比误差。第一可变延迟线根据第一占空比误差被控制,并且第二可变延迟线根据第二占空比误差被控制。空比误差被控制。空比误差被控制。

技术研发人员:崔训对 崔佳滥

受保护的技术使用者:三星电子株式会社

技术研发日:2021.05.08

技术公布日:2021/11/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。