技术特征:

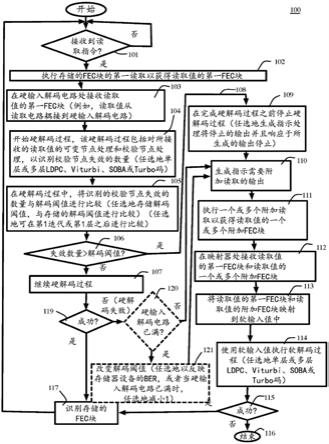

1.一种用于解码的方法,包括:在硬输入解码电路处接收读取值的第一前向纠错(fec)块,所述读取值的第一fec块的每个位表示存储的fec块的对应位;由所述硬输入解码电路开始硬解码过程,所述硬解码过程包括对所述读取值的第一fec块的可变节点处理和校验节点处理以识别校验节点失效的数量;在所述硬解码过程期间,将所识别的校验节点失效的数量与解码阈值进行比较;当所识别的校验节点失效的数量不大于所述解码阈值时,由所述硬输入解码电路继续所述硬解码过程;当所识别的校验节点失效的数量大于所述解码阈值时:在完成所述硬解码过程之前停止所述硬解码过程;生成指示需要附加读取的输出;在映射器处接收所述读取值的第一fec块和读取值的一个或多个附加fec块,所述读取值的一个或多个附加fec块中的每个附加fec块的每个位表示所述存储的fec块的对应位;将所述读取值的第一fec块和所述读取值的一个或多个附加fec块映射到软输入值中;以及对所述软输入值执行软解码过程以识别解码的fec块。2.根据权利要求1所述的方法,其中将所识别的校验节点失效的数量与解码阈值进行比较包括将单层纠错码的第一迭代中的所述校验节点失效的数量与所述解码阈值进行比较,停止所述硬解码过程包括不对所述读取值的第一fec块执行所述单层纠错码的任何后续迭代。3.根据权利要求1所述的方法,其中所述硬解码过程和所述软解码过程包括执行多层低密度奇偶校验(ldpc)纠错码。4.根据权利要求1所述的方法,其中所述硬解码过程和所述软解码过程包括执行选自由viterbi码、软输出viterbi算法(sova)码和turbo码组成的组的纠错码。5.根据权利要求1所述的方法,其中将所识别的校验节点失效的数量与解码阈值进行比较还包括将多层纠错码的第一迭代的第一层中的所述失效的数量与所述解码阈值进行比较,并且其中停止所述硬解码过程包括不对所述读取值的第一fec块执行所述多层纠错码的任何后续迭代。6.根据权利要求1所述的方法,还包括:通过从闪存存储器控制器的读取电路向所述fec块已存储在其上的一个或多个闪存存储器设备发送读取命令来执行所述存储的fec块的第一读取,并且响应于发送读取命令,在所述读取电路处接收所述读取值的第一fec块;将所述读取值的第一fec块耦接到所述硬输入解码电路;以及响应于所生成的指示需要附加读取的输出,通过从所述闪存存储器控制器的所述读取电路向所述fec块已存储在其上的所述一个或多个闪存存储器设备发送一个或多个附加读取命令来执行一个或多个附加读取,以及响应于发送一个或多个附加读取命令,接收所述读取值的一个或多个附加fec块。7.根据权利要求1所述的方法,其中继续所述硬解码过程还包括继续所述硬解码过程,直到所述硬解码过程已经成功识别所述存储的fec块或已经失败,并且在完成所述硬解码

过程之前停止所述硬解码过程还包括在所述硬解码过程已经成功识别所述存储的fec块或已经失败之前停止所述硬解码过程。8.根据权利要求1所述的方法,还包括在所述非易失性存储装置的寿命期间改变所述解码阈值以反映所述闪存存储器设备的误码率(ber)。9.根据权利要求1所述的方法,还包括当所述硬输入解码电路已满时改变所述解码阈值。10.根据权利要求1所述的方法,还包括当所述硬输入解码电路已满时增量地减小所述解码阈值。11.根据权利要求1所述的方法,还包括:生成指示所述硬输入解码电路何时已满的输出;接收包括码率值和阈值控制值的用户输入;基于所接收的码率值和阈值控制值来识别所述解码阈值;以及存储所识别的解码阈值。12.一种解码器,包括:硬输入解码电路,所述硬输入解码电路被配置为接收读取值的第一前向纠错(fec)块,所述读取值的第一fec块的每个位表示存储的fec块的对应位,并开始硬解码过程,所述硬解码过程包括对所述读取值的第一fec块的可变节点处理和校验节点处理以识别校验节点失效的数量;解码控制器,所述解码控制器耦接到所述硬输入解码电路,所述解码控制器被配置为在所述硬解码过程期间将所识别的校验节点失效的数量与解码阈值进行比较,当所识别的校验节点失效的数量大于所述解码阈值时,生成指示所述硬输入解码电路将停止所述纠错码的处理的输出,并且当所识别的校验节点失效的数量大于所述解码阈值时,生成指示需要附加读取的输出,其中响应于指示所述硬输入解码电路将停止所述纠错码的处理的所述输出,所述硬输入解码电路能够操作以在完成所述硬解码过程之前停止所述硬解码过程;映射器,所述映射器被配置为响应于所生成的指示需要附加读取的输出而接收所述读取值的第一fec块和读取值的附加fec块,并且被配置为将所述读取值的第一fec块和所述读取值的附加fec块映射到软输入值中;以及软输入解码电路,所述软输入解码电路耦接到所述映射器,所述软输入解码电路被配置为对所述软输入值执行软解码过程以从所述软输入值中识别解码的fec块。13.根据权利要求12所述的解码器,其中所述解码控制器被配置为将单层纠错码的第一迭代中所识别的校验节点失效的数量与所述解码阈值进行比较,并且被配置为当所述纠错码的所述第一迭代中的所识别的校验节点失效的数量大于所述解码阈值时,生成指示所述硬输入解码电路将停止所述纠错码的处理的输出。14.根据权利要求12所述的解码器,其中所述解码控制器被配置为将第一迭代的第一层中的所识别的校验节点失效的数量与所述解码阈值进行比较,并且被配置为当所述纠错码的所述第一迭代的所述第一层中所识别的校验节点失效的数量大于所述解码阈值时,生成指示所述硬输入解码电路将停止所述纠错码的处理的输出。15.根据权利要求12所述的解码器,其中所述解码控制器被配置为基于由用户输入的

码率值和由所述用户输入的阈值控制值来识别所述解码阈值。16.根据权利要求12所述的解码器,其中所述解码控制器被配置为通过在存储的查找表中执行所述输入码率值和阈值控制值的查找来识别所述解码阈值,以识别对应的解码阈值。17.根据权利要求12所述的解码器,其中所述解码控制器被配置为当所述硬输入解码电路已满时增量地减小所述解码阈值。18.根据权利要求12所述的解码器,其中所述硬解码过程和所述软解码过程各自包括执行选自由viterbi码、软输出viterbi算法(sova)码、turbo码和低密度奇偶校验(ldpc)码组成的组的纠错码。19.一种存储器控制器,包括:输入和输出电路;编码器,所述编码器被配置用于将在所述输入和输出电路处接收的数据编码到前向纠错(fec)块中;写入电路,所述写入电路耦接到所述编码器,所述写入电路被配置用于将所述fec块存储在非易失性存储装置上;读取电路,所述读取电路被配置用于读取所存储的fec块;硬输入解码电路,所述硬输入解码电路被配置为接收读取值的第一fec块,所述读取值的第一fec块的每个位表示所存储的fec块的对应位,并开始硬解码过程,所述硬解码过程包括对所述读取值的第一fec块的可变节点处理和校验节点处理以识别校验节点失效的数量;解码控制器,所述解码控制器耦接到所述硬输入解码电路,所述解码控制器被配置为在所述硬解码过程期间将所识别的校验节点失效的数量与解码阈值进行比较,当所识别的校验节点失效的数量大于所述解码阈值时,生成指示所述硬输入解码电路将停止所述纠错码的处理的输出,并且当所识别的校验节点失效的数量大于所述解码阈值时,生成指示需要附加读取的输出,其中响应于指示所述硬输入解码电路将停止所述纠错码的处理的所述输出,所述硬输入解码电路能够操作以在完成所述硬解码过程之前停止所述硬解码过程;映射器,所述映射器被配置为响应于所生成的指示需要附加读取的输出而接收所述读取值的第一fec块和读取值的附加fec块,并且被配置为将所述读取值的第一fec块和所述读取值的附加fec块映射到软输入值中;以及软输入解码电路,所述软输入解码电路耦接到所述映射器,所述软输入解码电路被配置为对所述软输入值执行软解码过程以识别解码的fec块。20.根据权利要求19所述的存储器控制器,其中所述解码控制器被配置为当所述硬输入解码电路已满时增量地减小所述解码阈值。

技术总结

本发明公开了一种用于解码的方法和装置。该方法包括:接收读取值的第一前向纠错(FEC)块;开始硬解码过程,其中识别校验节点失效的数量;以及在该硬解码过程期间,将所识别的校验节点失效的数量与解码阈值进行比较。当所识别的校验节点失效的数量不大于该解码阈值时,继续该硬解码过程。当所识别的校验节点失效的数量大于该解码阈值时,该方法包括:在完成该硬解码过程之前停止该硬解码过程;生成指示需要附加读取的输出;接收读取值的一个或多个附加FEC块,将该读取值的第一FEC块和该读取值的附加FEC块映射到软输入值中;以及对该软输入值执行软解码过程。值执行软解码过程。值执行软解码过程。

技术研发人员:P

受保护的技术使用者:微芯片技术股份有限公司

技术研发日:2020.03.05

技术公布日:2022/2/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。