技术特征:

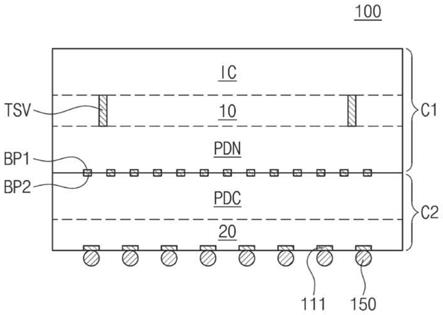

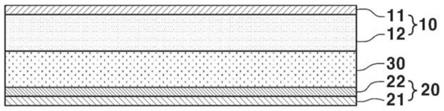

1.一种半导体封装,包括:第一半导体芯片,包括逻辑结构;以及第二半导体芯片,接合到所述第一半导体芯片,其中,所述第一半导体芯片包括:在第一半导体衬底的第一表面上并与所述逻辑结构连接的信号线,在所述第一半导体衬底的第二表面上的电力输送网络,所述第二表面与所述第一表面相对,以及穿通过孔,穿透所述第一半导体衬底并将所述电力输送网络连接到所述逻辑结构,并且其中,所述第二半导体芯片包括电容器层,所述电容器层在第二半导体衬底上并且与所述电力输送网络相邻。2.根据权利要求1所述的半导体封装,其中,所述第一半导体芯片的所述电力输送网络包括多个第一接合焊盘以及与所述第一接合焊盘连接的多条电力线,所述第二半导体芯片的所述电容器层包括在所述第二半导体衬底上的电力去耦电容器和与所述电力去耦电容器连接的第二接合焊盘,以及所述第一接合焊盘接合到所述第二接合焊盘。3.根据权利要求2所述的半导体封装,还包括:在所述第一接合焊盘和所述第二接合焊盘之间的连接端子,所述连接端子将所述第一接合焊盘连接到所述第二接合焊盘。4.根据权利要求1所述的半导体封装,其中,所述第一半导体衬底的侧表面与所述第二半导体衬底的侧表面竖直对准。5.根据权利要求1所述的半导体封装,其中,所述电容器层包括在所述第二半导体衬底上的多个电力去耦电容器,以及所述电力去耦电容器中的每一个包括:在所述第二半导体衬底上的底部电极焊盘,在所述底部电极焊盘上的多个底部电极,以均匀厚度覆盖所述底部电极的电容器介电层,以及在所述电容器介电层上的顶部电极,所述顶部电极覆盖所有底部电极。6.根据权利要求1所述的半导体封装,其中,所述逻辑结构包括:在所述第一半导体衬底的第一表面上的有源图案,在所述第一半导体衬底中的掩埋电力轨,以及将所述掩埋电力轨连接到所述有源图案的有源接触部,并且所述穿通过孔将所述掩埋电力轨连接到所述电力输送网络。7.根据权利要求6所述的半导体封装,还包括:在所述有源图案之间的器件隔离层,其中,所述器件隔离层的顶表面低于所述有源图案的顶表面,以及所述掩埋电力轨在所述器件隔离层中。

8.根据权利要求6所述的半导体封装,其中,所述穿通过孔的直径在50nm至150nm的范围内。9.根据权利要求6所述的半导体封装,其中,所述穿通过孔的竖直长度在300nm至1μm的范围内。10.一种半导体封装,包括:第一半导体衬底;第二半导体衬底;在所述第一半导体衬底和所述第二半导体衬底之间的电力输送网络;以及在所述电力输送网络和所述第二半导体衬底之间的电容器层。11.根据权利要求10所述的半导体封装,还包括:多个第一接合焊盘,连接到所述电力输送网络;以及多个第二接合焊盘,连接到所述电容器层,其中,所述第一接合焊盘接合到所述第二接合焊盘。12.根据权利要求11所述的半导体封装,其中,所述电容器层包括多个电力去耦电容器,以及所述多个电力去耦电容器在所述第二半导体衬底上并连接到所述第二接合焊盘。13.根据权利要求12所述的半导体封装,其中,所述电力去耦电容器中的每一个包括:在所述第二半导体衬底上的底部电极焊盘;在所述底部电极焊盘上的多个底部电极;以均匀的厚度覆盖所述底部电极的电容器介电层;以及在所述电容器介电层上的顶部电极,所述顶部电极覆盖所有底部电极。14.根据权利要求10所述的半导体封装,还包括:在所述第一半导体衬底上的逻辑结构;以及多个穿通过孔,穿透所述第一半导体衬底并连接到所述逻辑结构,其中,所述第一半导体衬底具有彼此相对的第一表面和第二表面,所述逻辑结构设置在所述第一半导体衬底的第一表面上,所述电力输送网络在所述第一半导体衬底的第二表面上,以及所述电力输送网络连接到所述穿通过孔。15.根据权利要求14所述的半导体封装,其中,所述逻辑结构包括:有源图案,在所述第一半导体衬底的第一表面上;栅极结构,跨所述有源图案;有源接触部,在所述栅极结构两侧并与所述有源图案接触;以及掩埋电力轨,在所述第一半导体衬底的第一表面和第二表面之间并连接到所述有源接触部,其中,所述电力输送网络通过所述穿通过孔电连接到所述掩埋电力轨。16.根据权利要求10所述的半导体封装,还包括:在所述第一半导体衬底的第一表面上的逻辑结构;穿通过孔,穿透所述第一半导体衬底并连接到所述逻辑结构;多个第一接合焊盘,在所述第一半导体衬底的第二表面上并连接到所述穿通过孔;以

及多个第二接合焊盘,接合到所述第一接合焊盘,所述第二接合焊盘通过所述第一接合焊盘连接到所述电力输送网络。17.一种半导体封装,包括:第一半导体衬底,具有第一表面和与所述第一表面相对的第二表面;有源图案,在所述第一半导体衬底的第一表面上;有源接触部,连接到所述有源图案;信号线,在所述有源接触部上并连接到所述有源接触部;掩埋电力轨,在所述第一半导体衬底中并连接到所述有源图案;穿通过孔,穿透所述第一半导体衬底并连接到所述掩埋电力轨;在所述第一半导体衬底的第二表面上的电力输送网络,所述电力输送网络包括连接到所述穿通过孔的电力线;第一接合焊盘,连接到所述电力输送网络;电容器层,包括在第二半导体衬底的第三表面上的电力去耦电容器,所述第三表面面向所述电力输送网络;以及第二接合焊盘,连接到所述电力去耦电容器,其中,所述第一接合焊盘和所述第二接合焊盘彼此接合。18.根据权利要求17所述的半导体封装,其中,所述掩埋电力轨部分地掩埋在所述第一半导体衬底中。19.根据权利要求17所述的半导体封装,其中,所述第一半导体衬底的侧表面与所述第二半导体衬底的侧表面对准。20.根据权利要求17所述的半导体封装,其中,所述电力去耦电容器中的每一个包括:在所述第二半导体衬底上的底部电极焊盘;在所述底部电极焊盘上的多个底部电极;以均匀的厚度覆盖所述底部电极的电容器介电层;以及在所述电容器介电层上的顶部电极,所述顶部电极覆盖所有底部电极。

技术总结

提供一种半导体封装,该半导体封装包括第一半导体芯片和与第一半导体芯片接合的第二半导体芯片,第一半导体芯片包括逻辑结构。第一半导体芯片可以包括:在第一半导体衬底的第一表面上并与逻辑结构连接的信号线;在第一半导体衬底的第二表面上的电力输送网络,第二表面与第一表面相对;以及穿通过孔,穿透第一半导体衬底并将电力输送网络连接到逻辑结构。第二半导体芯片可以包括电容器层,所述电容器层在第二半导体衬底上并且与电力输送网络相邻。在第二半导体衬底上并且与电力输送网络相邻。在第二半导体衬底上并且与电力输送网络相邻。

技术研发人员:李满浩 宋垠锡 金京范 吴琼硕 张彦铢

受保护的技术使用者:三星电子株式会社

技术研发日:2021.09.23

技术公布日:2022/5/20

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。