技术特征:

1.一种装置,包括:解码器电路,用于将一个或多个指令解码成从数据缓存加载数据的第一微操作、依赖于所述第一微操作的第二微操作、以及依赖于所述第二微操作的第三微操作;执行电路,用于执行所述第一微操作、所述第二微操作、以及所述第三微操作;以及预留站电路,包括加载推测跟踪器电路,并且所述预留站电路耦合在所述解码器电路和所述执行电路之间,所述加载推测跟踪器电路用于:针对所述第三微操作的预留站条目,跟踪所述第一微操作在所述数据缓存中的进度,以响应于所述第一微操作对在所述数据缓存中的数据的错失而针对所述第三微操作生成取消指示,其中,所述加载推测跟踪器电路用于:响应于所述第一微操作被调遣到所述数据缓存中而开始跟踪所述第一微操作在所述数据缓存中的进度。2.如权利要求1所述的装置,其中所述数据缓存包括多个流水线级,并且所述加载推测跟踪器电路用于只在所述多个流水线级的如下真子集中跟踪所述第一微操作的进度,该真子集包括确定是否存在所述数据缓存中的数据的错失的流水线级。3.如权利要求1所述的装置,其中所述数据缓存包括多个流水线级,并且所述加载推测跟踪器电路用于只在所述多个流水线级中的第二流水线级和紧挨在所述第二流水线级之前的第一流水线级中跟踪所述第一微操作的进度,所述第二流水线级确定是否存在所述数据缓存中的数据的错失。4.如权利要求1所述的装置,其中所述取消指示用于在所述第三微操作唤醒依赖微操作之前取消所述第三微操作。5.如权利要求1所述的装置,其中所述预留站电路包括统一推测状态传播和执行矩阵电路,所述统一推测状态传播和执行矩阵电路包括所述预留站条目,用于向用于所述第三微操作的预留站条目发送所述第一微操作在所述数据缓存中的进度的状态指示,并且在微操作的一个或多个生产者微操作被调遣来执行时向用于该微操作的预留站条目发送唤醒指示。6.如权利要求1所述的装置,其中所述预留站电路包括:第一拾取器电路,用于把在当前周期中接收其准备好执行指示的微操作进行发送以供执行;以及第二拾取器电路,用于把在先前周期中接收了其准备好执行指示的微操作进行发送以供执行。7.如权利要求6所述的装置,其中所述预留站电路还包括计数器,用于对多个微操作中的每一个微操作的一个或多个操作对象准备好执行的周期的数目进行计数。8.如权利要求6所述的装置,还包括第二执行电路,其中所述执行电路包括单周期结果旁路输入,所述第二执行电路不包括单周期结果旁路输入,并且所述第一拾取器电路用于发送微操作以在所述执行电路上执行,并且所述第二拾取器电路用于发送微操作以在所述第二执行电路上执行但不在所述执行电路上执行。9.如权利要求1至8中任一项所述的装置,其中所述第二微操作经由对于直接依赖于所述第一微操作的微操作的链式依赖性而间接依赖于所述第一微操作。10.一种方法,包括:用处理器的解码器电路将一个或多个指令解码成从所述处理器的数据缓存加载数据的第一微操作、依赖于所述第一微操作的第二微操作、以及依赖于所述第二微操作的第三微操作;

针对所述第三微操作填充所述处理器的预留站电路的预留站条目;以及响应于针对所述第三微操作填充所述预留站条目,由所述预留站电路的加载推测跟踪器电路跟踪所述第一微操作在所述数据缓存中的进度,以响应于所述第一微操作对在所述数据缓存中的数据的错失而针对所述第三微操作生成取消指示,其中,所述加载推测跟踪器电路响应于所述第一微操作被调遣到所述数据缓存中而开始跟踪所述第一微操作在所述数据缓存中的进度。11.如权利要求10所述的方法,其中所述数据缓存包括多个流水线级,并且所述方法还包括:只在所述多个流水线级的如下真子集中由所述加载推测跟踪器电路跟踪所述第一微操作的进度,所述真子集包括确定是否存在所述数据缓存中的数据的错失的流水线级。12.如权利要求10所述的方法,其中所述数据缓存包括多个流水线级,并且所述方法还包括:只在所述多个流水线级中的第二流水线级和紧挨在所述第二流水线级之前的第一流水线级中由所述加载推测跟踪器电路跟踪所述第一微操作的进度,所述第二流水线级确定是否存在所述数据缓存中的数据的错失。13.如权利要求10所述的方法,其中所述取消指示在被拾取来执行的所述第三微操作唤醒依赖微操作之前取消所述第三微操作。14.如权利要求10所述的方法,其中所述预留站电路包括统一推测状态传播和执行矩阵电路,所述统一推测状态传播和执行矩阵电路包括所述预留站条目,并且所述方法还包括:由所述统一推测状态传播和执行矩阵电路将所述第一微操作在所述数据缓存中的进度的状态指示发送到用于所述第三微操作的预留站条目,并且在微操作的一个或多个生产者微操作被调遣来执行时向用于该微操作的预留站条目发送唤醒指示。15.如权利要求10所述的方法,还包括:由所述预留站电路的第一拾取器电路把在当前周期中接收其准备好执行指示的微操作进行发送以供执行;以及由所述预留站电路的第二拾取器电路把在先前周期中接收了其准备好执行指示的微操作进行发送以供执行。16.如权利要求15所述的方法,还包括:由所述预留站电路的计数器对多个微操作中的每一个微操作的一个或多个操作对象准备好执行的周期的数目进行计数。17.如权利要求15所述的方法,其中由所述第一拾取器电路进行发送以供执行是向所述处理器中包括单周期结果旁路输入的执行电路进行发送,并且由所述第二拾取器电路进行发送以供执行是向所述处理器中不包括单周期结果旁路输入的第二执行电路进行发送。18.一种装置,包括:存储器;以及处理器,包括:与所述存储器耦合的数据缓存,解码器电路,用于将一个或多个指令解码成从所述数据缓存加载数据的第一微操作、依赖于所述第一微操作的第二微操作、以及依赖于所述第二微操作的第三微操作,执行电路,用于执行所述第一微操作、所述第二微操作、以及所述第三微操作,以及预留站电路,包括加载推测跟踪器电路,并且所述预留站电路耦合在所述解码器电路和所述执行电路之间,所述加载推测跟踪器电路用于:针对所述第三微操作的预留站条目,

跟踪所述第一微操作在所述数据缓存中的进度,以响应于所述第一微操作对在所述数据缓存中的数据的错失而针对所述第三微操作生成取消指示,其中,所述加载推测跟踪器电路用于:响应于所述第一微操作被调遣到所述数据缓存中而开始跟踪所述第一微操作在所述数据缓存中的进度。19.如权利要求18所述的装置,其中所述数据缓存包括多个流水线级,并且所述加载推测跟踪器电路用于只在所述多个流水线级的如下真子集中跟踪所述第一微操作的进度,所述真子集包括确定是否存在所述数据缓存中的数据的错失的流水线级。20.如权利要求18所述的装置,其中所述数据缓存包括多个流水线级,并且所述加载推测跟踪器电路用于只在所述多个流水线级中的第二流水线级和紧挨在所述第二流水线级之前的第一流水线级中跟踪所述第一微操作的进度,所述第二流水线级确定是否存在所述数据缓存中的数据的错失。21.如权利要求18所述的装置,其中所述取消指示用于在被拾取来执行的所述第三微操作唤醒依赖微操作之前取消所述第三微操作。22.如权利要求18所述的装置,其中所述预留站电路包括统一推测状态传播和执行矩阵电路,所述统一推测状态传播和执行矩阵电路包括所述预留站条目,用于向用于所述第三微操作的预留站条目发送所述第一微操作在所述数据缓存中的进度的状态指示,并且在微操作的一个或多个生产者微操作被调遣来执行时向用于该微操作的预留站条目发送唤醒指示。23.如权利要求18所述的装置,其中所述预留站电路包括:第一拾取器电路,用于把在当前周期中接收其准备好执行指示的微操作进行发送以供执行;以及第二拾取器电路,用于把在先前周期中接收了其准备好执行指示的微操作进行发送以供执行。24.如权利要求23所述的装置,其中所述预留站电路还包括计数器,用于对多个微操作中的每一个微操作的一个或多个操作对象准备好执行的周期的数目进行计数。25.如权利要求23所述的装置,还包括第二执行电路,其中所述执行电路包括单周期结果旁路输入,所述第二执行电路不包括单周期结果旁路输入,并且所述第一拾取器电路用于发送微操作以在所述执行电路上执行,并且所述第二拾取器电路用于发送微操作以在所述第二执行电路上执行但不在所述执行电路上执行。

技术总结

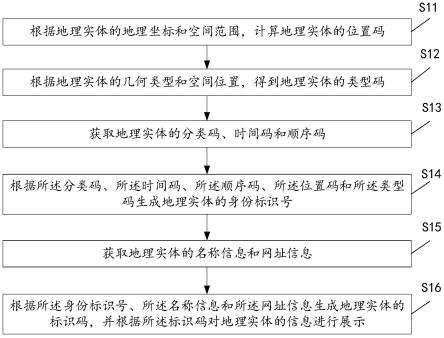

本公开描述了用于可缩放预留站的方法、系统和装置。在一种实施例中,硬件处理器核心包括:解码器电路,用于将一个或多个指令解码成从数据缓存加载数据的第一微操作,依赖于第一微操作的第二微操作,以及依赖于第二微操作的第三微操作;执行电路,用于执行第一微操作、第二微操作和第三微操作;以及预留站电路,包括加载推测跟踪器电路并且耦合在解码器电路和执行电路之间,加载推测跟踪器电路对于第三微操作的预留站条目,跟踪第一微操作在数据缓存中的进度,以响应于第一微操作对在数据缓存中的数据的错失而为第三微操作生成取消指示,其中加载推测跟踪器电路响应于第一微操作被调遣到数据缓存中而开始跟踪第一微操作在数据缓存中的进度。缓存中的进度。缓存中的进度。

技术研发人员:温

受保护的技术使用者:英特尔公司

技术研发日:2021.10.13

技术公布日:2022/6/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。