技术特征:

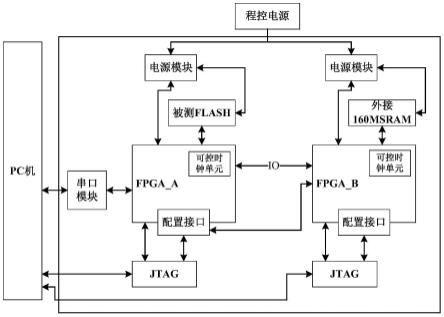

1.一种基于fpga的flash应用验证系统,其特征在于:包括pc机、flash应用验证板和程控电源;flash应用验证板包括两块fpga、串口模块、电源模块、配置存储器接插件、jtag和sram;其中两块fpga分别记为fpga_a和fpga_b;当验证被测flash的擦写读功能时,被测flash与fpga_a的io口连接;当验证被测flash的jtag功能和存储器配置功能时,被测flash与配置存储器接插件连接,所述配置存储器接插件为fpga的配置接口;串口模块用于连接pc机和fpga_a,将pc机的擦、写、读指令发送给fpga_a,并将fpga_a反馈的结果反馈回pc机;fpga_a根据pc机的擦、写、读指令对被测flash进行擦、写、读测试,采集被测flash的输出数据,据此判断被测flash是否正常工作,判断结果反馈给串口模块;fpga_b采集正在进行工作的被测flash的所有输入输出数据,通过配置存储器接插件和jtag发送给pc机;pc机:当验证被测flash的擦写读功能时,向串口模块发送擦、写、读指令,接收fpga_a反馈的结果,并显示;当验证被测flash的jtag功能时,通过jtag向被测flash发送擦、写、读指令,通过jtag读取被测flash反馈的结果并显示;通过jtag向被测flash发送程序配置指令,以验证被测flash的存储器配置功能;对fpga_b采集的被测flash的所有输入输出数据进行实时显示;电源模块用于为flash应用验证板供电,程控电源为电源模块供电。2.根据权利要求1所述的一种基于fpga的flash应用验证系统,其特征在于:fpga_a内部集成了flash控制器和可控时钟单元,flash控制器接收pc机发送的擦、写、读指令,据此对被测flash进行擦写读功能验证,采集被测flash的输出数据,判断被测flash是否正常工作,判断结果反馈给串口模块;可控时钟单元为fpga_a内部pll,用于产生两种时钟频率,一种时钟频率用来维持fpga_a正常工作,另一种时钟频率作为被测flash的输入时钟频率。3.根据权利要求2所述的一种基于fpga的flash应用验证系统,其特征在于,flash控制器对被测flash进行擦写读功能验证的方法如下:flash控制器接收到pc机发送的擦指令后,将擦控制信号和地址发送给被测flash,被测flash执行擦除指令;执行完后flash控制器采集被测flash所有地址的数据,如果数据为ff,代表擦除成功,否则擦除失败;flash控制器接收到pc机发送的写指令后,将写控制信号、输入数据和地址发送给被测flash,直至所有地址写入完毕;flash控制器接收到pc机发送的读指令后,采集被测flash相应地址的输出数据,将输入数据和输出数据进行对比,当读操作执行结束时,若输入数据和输出数据一直相同,则被测flash的读写功能正常,如果输入数据和输出数据不一致,表示被测flash的读写功能异常。4.根据权利要求2所述的一种基于fpga的flash应用验证系统,其特征在于,pc机验证被测flash的jtag功能的实现方式如下:pc机读入预加载的数据;pc机通过jtag读取被测flash的id;

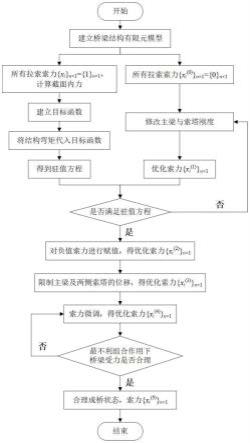

pc机通过jtag向被测flash发送擦指令,被测flash执行完擦指令后,pc机通过jtag对被测flash相应地址的数据通过校验和查空检查,若数据查空成功,说明擦除成功,否则失败;pc机通过jtag向被测flash发送写指令,将预加载的数据写入被测flash指定地址;pc机通过jtag向被测flash发送读指令,从指定地址读取数据,对读取的数据与预加载的数据进行校验,两者一致,则认为写和读成功。5.根据权利要求2所述的验证方法,其特征在于,验证被测flash的存储器配置功能的实现方法如下:pc机通过jtag向被测flash发送程序配置指令和配置码型数据,被测flash加载配置码型数据;fpga_a上设置了led灯,所述配置码型数据用于控制led灯实现跑马灯功能;被测flash完成加载后,观测fpga_a上的led灯,看其是否能实现跑马灯功能,若不能,则被测flash的存储器配置功能异常;若能,则被测flash断电再重新上电,此时若不能实现跑马灯功能,则被测flash的存储器配置功能异常,若仍能实现跑马灯功能,则对被测flash进行软复位;软复位后,若不能实现跑马灯功能,则被测flash的存储器配置功能异常;若仍能实现跑马灯功能,则被测的存储器配置功能正常。6.根据权利要求1所述的一种基于fpga的flash应用验证系统,其特征在于:fpga_b内部集成了flash控制器和可控时钟单元,fpga_b外挂sram,能够向sram发送控制信号、时钟、地址和数据,并且能够采集sram的输出数据。7.根据权利要求6所述的一种基于fpga的flash应用验证系统,其特征在于,fpga_b也能作为flash,此时fpga_a的jtag与fpga_b的io口相连;pc机通过jtag指令访问fpga_b,将测试程序下载到fpga_b里,此时的fpga_b变为被测flash;pc机通过jtag指令访问fpga_a,验证fpga_b作为被测flash的擦、写、读功能。8.根据权利要求7所述的一种基于fpga的flash应用验证系统,其特征在于,还能进行被测flash数字逻辑验证,方法如下:fpga_a的jtag与fpga_b的io口相连,被测flash与fpga_a的io口连接;将此时的fpga_b记为假flash;pc机通过串口模块向fpga_a发送操作指令,fpga_a根据该操作指令控制被测flash执行相应操作,并采集被测flash实时数据通过串口模块反馈给pc机;同时,pc机通过jtag向fpga_a发送操作指令,fpga_a根据该操作指令控制假flash执行相应操作,并采集假flash实时数据通过jtag反馈给pc机;pc机同时实时监测被测flash和假flash在工作时数据端的工作状态,以此判断被测flash数字逻辑是否准确。9.根据权利要求6所述的一种基于fpga的flash应用验证系统,其特征在于:电源模块包括第一电源模块和第二电源模块,第一电源模块为fpga_a、串口模块、被测flash供电,第二电源模块为fpga_b和外挂sram供电。10.根据权利要求1所述的一种基于fpga的flash应用验证系统,其特征在于:被测flash为spi子板、nor_flash子板或prom子板。

技术总结

本发明公开了一种基于FPGA的FLASH应用验证系统,包括PC机、FPGA应用验证板、FLASH子板。FPGA应用验证板设有两个FPGA芯片;每个FPGA芯片都与FLASH相连,可独立访问FLASH,对其进行验证操作;每个FPGA外接大容量160MbSRAM;更换FLASH子板可验证NOR_FLASH和SPI_FLASH。本发明同时公开了一种基于该系统的验证方法,该方法首先确定上电顺序,JTAG功能验证,数字逻辑验证,读写功能验证。本发明验证功能全面、通用性强,对一系列FLASH的应用验证具有重要意义。对一系列FLASH的应用验证具有重要意义。对一系列FLASH的应用验证具有重要意义。

技术研发人员:王佳 陈雷 陈茂鑫 李建成 董方磊 许凯亮 周涛 杨作涵

受保护的技术使用者:北京微电子技术研究所

技术研发日:2022.04.18

技术公布日:2022/7/1

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。