技术特征:

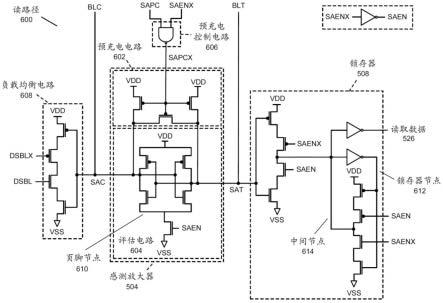

1.一种用于从电子装置中的存储器读取数据的读路径,其包括:感测放大器,所述感测放大器包括数据(sat)节点和数据补码(sac)节点;和锁存器,所述锁存器包括:输入三态反相器,其包括耦接在vdd与中间节点之间的第一和第二pmos晶体管以及耦接在vss与所述中间节点之间的第一和第二nmos晶体管,其中:所述第一pmos晶体管和所述第一nmos晶体管的栅极引线耦接到所述sat节点;所述第二pmos晶体管的栅极引线耦接到感测放大器启用补码(saenx)输入;并且所述第二nmos晶体管的栅极引线耦接到感测放大器启用(saen)输入;和输出驱动器,其具有耦接到所述中间节点的输出驱动器输入和耦接到数据输出节点的输出驱动器输出。2.如权利要求1所述的读路径,其还包括:负载均衡电路,所述负载均衡电路包括:负载均衡三态反相器,其包括耦接在vdd与vss之间的第三和第四pmos晶体管以及第三和第四nmos晶体管,其中:所述第三pmos晶体管和所述第三nmos晶体管的栅极引线耦接到所述sac节点;并且所述第四pmos晶体管和所述第四nmos晶体管的栅极引线耦接到禁用输入,所述禁用输入将所述第四pmos晶体管和所述第四nmos晶体管维持在关闭状态。3.如权利要求1所述的读路径,其还包括:所述感测放大器中的预充电电路,所述预充电电路耦接到所述sat节点和所述sac节点并且被配置为对所述sat节点和所述sac节点进行预充电;和预充电控制电路,所述预充电控制电路包括:感测放大器预充电(sapc)输入;saenx输入;以及感测放大器预充电补码(sapcx)输出,其耦接到所述预充电电路并且被配置为控制所述预充电电路何时对所述sat节点和所述sac节点进行预充电,所述预充电控制电路基于所述sapc输入和所述saenx输入的值来驱动所述sapcx输出上的信号。4.如权利要求3所述的读路径,其中所述预充电控制电路包括:nand逻辑门,其具有耦接到所述sapc输入的第一输入、耦接到所述saenx输入的第二输入和耦接到所述sapcx输出的第一输出。5.如权利要求3所述的读路径,其中所述预充电电路包括:耦接在vdd与所述sac节点之间的第一pmos晶体管;耦接在vdd与所述sat节点之间的第二pmos晶体管;以及耦接在所述sat节点与所述sac节点之间的第三pmos晶体管,其中用于所述第一、第二和第三pmos晶体管的栅极引线耦接到所述sapcx输出。6.如权利要求1所述的读路径,其中所述锁存器还包括:存储电路元件,其包括:锁存反相器,所述锁存反相器具有耦接到所述中间节点的锁存反相器输入和耦接到锁存器节点的锁存反相器输出;和锁存三态反相器,所述锁存三态反相器包括耦接在vdd与所述中间节点之间的第三和

第四pmos晶体管以及耦接在vss与所述中间节点之间的第三和第四nmos晶体管,其中:所述第三pmos晶体管和所述第三nmos晶体管的栅极引线耦接到所述锁存器节点;所述第四pmos晶体管的栅极引线耦接到所述saen输入;并且所述第四nmos晶体管的栅极引线耦接到所述saenx输入。7.如权利要求1所述的读路径,其中所述感测放大器包括:耦接到所述sat节点的位输入;耦接到所述sac节点的位补码输入;以及评估电路,其耦接到所述sat节点和所述sac节点并且被配置为基于所述位输入和所述位补码输入的值来输出所述sat节点上的sat信号和所述sac节点上的sac信号。8.如权利要求7所述的读路径,其还包括:一个或多个同步随机存取存储器(sram)单元,每个sram单元包括位输出和位补码输出,用于所述一个或多个sram位单元的所述位输出和所述位补码输出分别耦接到用于所述感测放大器的所述位输入和所述位补码输入。9.如权利要求7所述的读路径,其中所述评估电路包括:耦接在vdd与页脚节点之间的第一pmos晶体管和第一nmos晶体管,其中所述sac节点耦接到所述第一pmos晶体管与所述第一nmos晶体管之间的第一中间节点,并且所述sat节点耦接到用于所述第一pmos晶体管和所述第一nmos晶体管的栅极引线;耦接在vdd与页脚节点之间的第二pmos晶体管和第二nmos晶体管,其中所述sat节点耦接到所述第二pmos晶体管与所述第二nmos晶体管之间的第二中间节点,并且所述sac节点耦接到用于所述第二pmos晶体管和所述第二nmos晶体管的栅极引线;以及耦接在所述页脚节点与vss之间的第三nmos晶体管,其中用于所述第三nmos晶体管的栅极引线耦接到所述saen输入。10.一种电子装置,其包括:处理子系统;和耦接到所述处理子系统的存储器,所述存储器包括用于从所述存储器读取数据的至少一个读路径,所述至少一个读路径包括:感测放大器,所述感测放大器包括数据(sat)节点和数据补码(sac)节点;和锁存器,所述锁存器包括:输入三态反相器,其包括耦接在vdd与中间节点之间的第一和第二pmos晶体管以及耦接在vss与所述中间节点之间的第一和第二nmos晶体管,其中:所述第一pmos晶体管和所述第一nmos晶体管的栅极引线耦接到所述sat节点;所述第二pmos晶体管的栅极引线耦接到感测放大器启用补码(saenx)输入;并且所述第二nmos晶体管的栅极引线耦接到感测放大器启用(saen)输入;和输出驱动器,其具有耦接到所述中间节点的输出驱动器输入和耦接到数据输出节点的输出驱动器输出。11.如权利要求10所述的电子装置,其中所述至少一个读路径还包括:负载均衡电路,所述负载均衡电路包括:负载均衡三态反相器,其包括耦接在vdd与vss之间的第三和第四pmos晶体管以及第三和第四nmos晶体管,其中:

所述第三pmos晶体管和所述第三nmos晶体管的栅极引线耦接到所述sac节点;并且所述第四pmos晶体管和所述第四nmos晶体管的栅极引线耦接到禁用输入,所述禁用输入将所述第四pmos晶体管和所述第四nmos晶体管维持在关闭状态。12.如权利要求10所述的电子装置,其中所述至少一个读路径还包括:所述感测放大器中的预充电电路,所述预充电电路耦接到所述sat节点和所述sac节点并且被配置为对所述sat节点和所述sac节点进行预充电;和预充电控制电路,所述预充电控制电路包括:感测放大器预充电(sapc)输入;saenx输入;以及感测放大器预充电补码(sapcx)输出,其耦接到所述预充电电路并且被配置为控制所述预充电电路何时对所述sat节点和所述sac节点进行预充电,所述预充电控制电路基于所述sapc输入和所述saenx输入的值来驱动所述sapcx输出上的信号。13.如权利要求12所述的电子装置,其中所述预充电控制电路包括:nand逻辑门,其具有耦接到所述sapc输入的第一输入、耦接到所述saenx输入的第二输入和耦接到所述sapcx输出的第一输出。14.如权利要求12所述的电子装置,其中所述预充电电路包括:耦接在vdd与所述sac节点之间的第一pmos晶体管;耦接在vdd与所述sat节点之间的第二pmos晶体管;以及耦接在所述sat节点与所述sac节点之间的第三pmos晶体管,其中用于所述第一、第二和第三pmos晶体管的栅极引线耦接到所述sapcx输出。15.如权利要求10所述的电子装置,其中所述锁存器还包括:存储电路元件,其包括:锁存反相器,所述锁存反相器具有耦接到所述中间节点的锁存反相器输入和耦接到锁存器节点的锁存反相器输出;和锁存三态反相器,所述锁存三态反相器包括耦接在vdd与所述中间节点之间的第三和第四pmos晶体管以及耦接在vss与所述中间节点之间的第三和第四nmos晶体管,其中:所述第三pmos晶体管和所述第三nmos晶体管的栅极引线耦接到所述锁存器节点;所述第四pmos晶体管的栅极引线耦接到所述saen输入;并且所述第四nmos晶体管的栅极引线耦接到所述saenx输入。16.如权利要求10所述的电子装置,其中所述感测放大器包括:耦接到所述sat节点的位输入;耦接到所述sac节点的位补码输入;以及评估电路,其耦接到所述sat节点和所述sac节点并且被配置为基于所述位输入和所述位补码输入的值来输出所述sat节点上的sat信号和所述sac节点上的sac信号。17.如权利要求16所述的电子装置,其中所述存储器包括:一个或多个同步随机存取存储器(sram)单元,每个sram单元包括位输出和位补码输出,用于所述一个或多个sram位单元的所述位输出和所述位补码输出分别耦接到用于所述感测放大器的所述位输入和所述位补码输入。18.如权利要求16所述的电子装置,其中所述评估电路包括:

耦接在vdd与页脚节点之间的第一pmos晶体管和第一nmos晶体管,其中所述sac节点耦接到所述第一pmos晶体管与所述第一nmos晶体管之间的第一中间节点,并且所述sat节点耦接到用于所述第一pmos晶体管和所述第一nmos晶体管的栅极引线;耦接在vdd与页脚节点之间的第二pmos晶体管和第二nmos晶体管,其中所述sat节点耦接到所述第二pmos晶体管与所述第二nmos晶体管之间的第二中间节点,并且所述sac节点耦接到用于所述第二pmos晶体管和所述第二nmos晶体管的栅极引线;以及耦接在所述页脚节点与vss之间的第三nmos晶体管,其中用于所述第三nmos晶体管的栅极引线耦接到所述saen输入。19.一种集成电路,其包括:第一存储体,所述第一存储体包括一个或多个第一存储体sram单元、耦接到所述一个或多个第一存储体sram单元的第一存储体感测放大器以及耦接到所述第一存储体感测放大器的感测放大器(sat)输出的第一存储体共享锁存器输入三态反相器,所述第一存储体感测放大器和所述第一存储体共享锁存器输入三态反相器的评估电路由第一存储体感测放大器启用(saen)信号和/或第一存储体感测放大器启用补码(saenx)信号控制;第二存储体,所述第二存储体包括一个或多个第二存储体sram单元、耦接到所述一个或多个第二存储体sram单元的第二存储体感测放大器以及耦接到所述第二存储体感测放大器的sat输出的第二存储体共享锁存器输入三态反相器,所述第二存储体感测放大器和所述第二存储体共享锁存器输入三态反相器的评估电路由第二存储体saen信号和/或第二存储体saenx信号控制;以及共享锁存器,所述共享锁存器包括共享锁存器存储元件,所述共享锁存器存储元件具有一对背靠背的共享锁存反相器和共享锁存三态反相器,所述共享锁存反相器的共享锁存反相器输入耦接到所述第一存储体共享锁存器输入三态反相器和所述第二存储体共享锁存器输入三态反相器两者的输出,并且所述共享锁存三态反相器由共享锁存器启用(slen)信号和共享锁存器启用补码(slenx)信号控制,所述slen信号基于所述第一存储体saen信号和所述第二存储体saen信号的逻辑组合而生成,并且所述slenx信号基于所述第一存储体saenx信号和所述第二存储体saenx信号的逻辑组合而生成。20.如权利要求19所述的集成电路,其还包括:所述第一存储体感测放大器中的第一存储体预充电电路,所述第一存储体预充电电路由第一存储体感测放大器预充电补码(sapcx)信号控制,所述第一存储体sapcx信号基于第一存储体感测放大器预充电(sapc)信号和所述第一存储体saenx信号的逻辑组合而生成;和所述第二存储体感测放大器中的第二存储体预充电电路,所述第二存储体预充电电路由第二存储体sapcx信号控制,所述第二存储体sapcx信号基于第二存储体sapc信号和所述第二存储体saenx信号的逻辑组合而生成。21.如权利要求19所述的集成电路,其还包括:第一存储体负载均衡电路,所述第一存储体负载均衡电路耦接到所述第一存储体感测放大器的感测放大器补码(sac)节点并且被配置为近似地均衡第一电容负载,所述第一电容负载由所述第一存储体输入三态反相器提供给所述第一存储体感测放大器的所述sat节点;和

第二存储体负载均衡电路,所述第二存储体负载均衡电路耦接到所述第二存储体感测放大器的sac节点并且被配置为近似地均衡第二电容负载,所述第二电容负载由所述第二存储体输入三态反相器提供给所述第二存储体感测放大器的sat节点。

技术总结

一种用于从存储器读取数据的读路径包括感测放大器,所述感测放大器具有数据(SAT)输出节点、数据补码(SAC)输出节点和锁存器。所述锁存器包括输入三态反相器,其包括连接在VDD与中间节点之间的第一和第二PMOS晶体管以及连接在VSS与所述中间节点之间的第一和第二NMOS晶体管。所述第一PMOS晶体管和所述第一NMOS晶体管的栅极引线连接到所述SAT节点;所述第二PMOS晶体管的栅极引线连接到感测放大器启用补码输入;并且所述第二NMOS晶体管的栅极引线连接到感测放大器启用输入。所述锁存器还包括输出驱动器,其具有连接到所述中间节点的输入和连接到数据输出节点的输出。因此,所述锁存器具有所述SAT节点与所述数据输出节点之间的两个门延迟。之间的两个门延迟。之间的两个门延迟。

技术研发人员:阿里吉特

受保护的技术使用者:超威半导体公司

技术研发日:2020.11.04

技术公布日:2022/7/9

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。