技术特征:

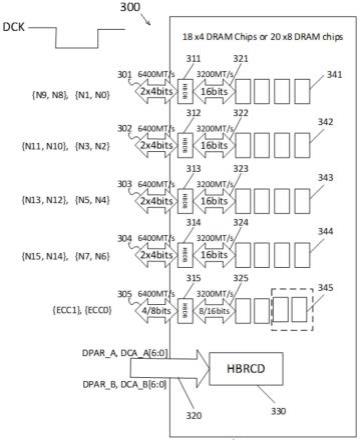

1.一种ddr5 dimm,其特征在于,包括第一子通道;所述第一子通道包括第一组数据缓存器和第一组dram芯片;所述第一组数据缓存器用于以第一速率通过第一组数据总线获取第一数据和第一ecc码,还用于以第二速率通过第二组数据总线将所述第一数据和所述第一ecc码存储至所述第一组dram芯片;所述第一组数据缓存器包括多个数据缓存器,所述第一组dram芯片包括多个dram芯片组,所述第一组数据总线包括多个主机侧数据总线,所述第二组数据总线包括多个存储侧数据总线;所述主机侧数据总线、所述数据缓存器、所述存储侧数据总线和所述dram芯片组一一对应。2.如权利要求1所述的ddr5 dimm,其特征在于,所述第一数据包括第一部分和第二部分,所述第一ecc码包括第一ecc数据和第二ecc数据;所述第一组数据缓存器用于在时钟的上升沿获取所述第一部分和所述第一ecc数据,还用于在时钟的下降沿获取所述第二部分和所述第二ecc数据;所述第一部分和所述第二部分均包括连续的多个半字节数据。3.如权利要求2所述的ddr5 dimm,其特征在于,所述第一组dram芯片均为

×

4dram芯片,所述第一ecc数据和所述第二ecc数据的长度均为半字节;所述多个数据缓存器中的每一个用于在时钟的上升沿获取所述第一部分中的2个半字节数据或第一ecc数据,还用于在时钟的下降沿获取所述第二部分中的2个半字节数据或第二ecc数据,还用于将获取的第一部分中的2个半字节数据和第二部分中的2个半字节数据存储至对应的dram芯片组,或者将获取的第一ecc数据和第二ecc数据存储至对应的dram芯片组。4.如权利要求3所述的ddr5 dimm,其特征在于,所述dram芯片组中的每一个dram芯片存储1个半字节数据,或者所述dram芯片组中的每一个dram芯片存储所述第一ecc数据或者所述第二ecc数据。5.如权利要求2所述的ddr5 dimm,其特征在于,所述第一组dram芯片均为

×

8dram芯片,所述第一ecc数据和所述第二ecc数据的长度均为一个字节;所述多个数据缓存器中的每一个用于在时钟的上升沿获取所述第一部分中的2个半字节数据或第一ecc数据,还用于在时钟的下降沿获取所述第二部分中的2个半字节数据或第二ecc数据,还用于将获取的第一部分中的2个半字节数据和第二部分中的2个半字节数据存储至对应的dram芯片组,或者将获取的第一ecc数据和第二ecc数据存储至对应的dram芯片组。6.如权利要求5所述的ddr5 dimm,其特征在于,所述第一部分中的2个半字节数据存储至对应的dram芯片组的一个dram芯片中,所述第二部分中的2个半字节数据存储至对应的dram芯片组的另一个dram芯片中;所述第一ecc数据存储至对应的dram芯片组的一个dram芯片中,所述第二ecc数据存储至对应的dram芯片组的另一个dram芯片中。7.如权利要求1至6中任一项所述的ddr5 dimm,其特征在于,所述第一子通道还包括时钟锁存驱动器,所述ddr5 dimm还包括第二子通道,所述第二子通道具有与所述第一子通道相同的结构,所述时钟锁存驱动器为所述第一子通道和所述第二子通道共用。8.一种存储系统,其特征在于,包括cpu、存储器控制器和如权利要求1至7中任一项所述的ddr5 dimm。9.一种存储系统的操作方法,所述存储系统包括存储器控制器和ddr5 dimm,其特征在于,所述操作方法包括:判断所述ddr5 dimm是否支持chipkill功能;

在所述ddr5 dimm支持chipkill功能时,进一步判断所述ddr5 dimm是否为

×

4dimm;在所述ddr5 dimm是

×

4dimm时,将接收的4个连续的数据位组合成与dram的数据宽度相同的一个半字节数据,对16个连续的半字节数据执行gf(24)空间的rs(18,16)码并生成2个长度为半字节的ecc数据以支持chipkill校正算法;在所述ddr5 dimm是

×

8dimm时,将两个连续的数据半字节组合成与dram的数据宽度相同的一个字节数据,对8个连续的字节数据执行gf(28)空间的rs(10,8)码并生成2个长度为一个字节的ecc数据以支持chipkill校正算法。10.如权利要求9所述的存储系统的操作方法,其特征在于,在所述ddr5 dimm是

×

4dimm时,将所述16个连续的半字节数据和所述2个长度为半字节的ecc数据分别写入18个

×

4dram芯片;在所述ddr5 dimm是

×

8dimm时,将所述8个连续的字节数据和所述2个长度为一个字节的ecc数据分别写入10个

×

8dram芯片。

技术总结

本发明公开了一种存储系统及其操作方法。该系统中的DDR5DIMM包括第一子通道;第一子通道包括第一组数据缓存器和第一组DRAM芯片;第一组数据缓存器(DB)用于以第一速率通过第一组数据总线获取第一数据和第一ECC码,还用于以第二速率通过第二组数据总线将所述第一数据和所述第一ECC码存储至所述第一组DRAM芯片。第一组数据缓存器包括多个数据缓存器,第一组DRAM芯片包括多个DRAM芯片组,第一组数据总线包括多个主机侧数据总线,第二组数据总线包括多个存储侧数据总线;主机侧数据总线、数据缓存器、存储侧数据总线和DRAM芯片组一一对应。本发明支持chipkill ECC功能,且芯片使用量少,成本和功耗低。成本和功耗低。成本和功耗低。

技术研发人员:黄明

受保护的技术使用者:芯动微电子科技(珠海)有限公司

技术研发日:2022.04.20

技术公布日:2022/7/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。