技术特征:

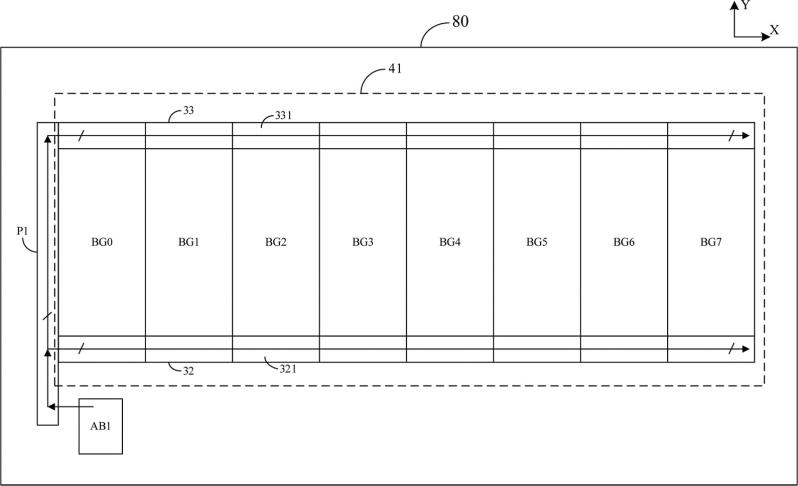

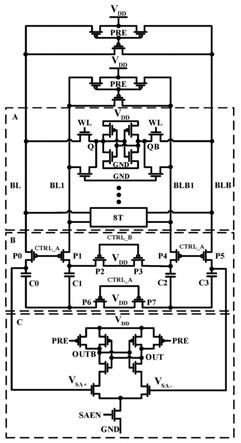

1.一种存储器,其特征在于,所述存储器包括至少一个阵列区;所述阵列区包括:存储体区、第一锁存区和第二锁存区;其中,所述第一锁存区耦接于所述存储体区的第一端,所述第二锁存区耦接于所述存储体区的第二端;所述存储体区的第一端和第二端为沿第一方向相对的两端;所述第一锁存区和所述第二锁存区,用于将熔丝数据锁存并传输到所述存储体区。2.根据权利要求1所述的存储器,其特征在于,所述存储体区包括:n个存储体组;所述第一锁存区包括:n个第一锁存单元;所述第二锁存区包括:n个第二锁存单元;n个所述存储体组、n个所述第一锁存单元和n个所述第二锁存单元分别沿第二方向依次排布;所述第二方向垂直于所述第一方向;n个所述存储体组,一一对应耦接n个所述第一锁存单元,以及,一一对应耦接n个所述第二锁存单元。3.根据权利要求1所述的存储器,其特征在于,所述存储器还包括:至少一个反熔丝阵列和至少一条信号路径;至少一条所述信号路径沿所述第一方向延伸,且设置于所述存储体区沿第二方向相对的两端中的至少一端;所述反熔丝阵列,用于存储和发送所述熔丝数据;所述信号路径,分别耦接所述反熔丝阵列、所述第一锁存区和所述第二锁存区,用于将所述熔丝数据传输到所述第一锁存区和所述第二锁存区。4.根据权利要求3所述的存储器,其特征在于,所述反熔丝阵列发送的所述熔丝数据为并行状态;所述存储器还包括:至少一个串行器;所述串行器,设置于所述反熔丝阵列和所述信号路径之间,分别耦接所述反熔丝阵列和所述信号路径,用于将所述反熔丝阵列发送的所述熔丝数据转化为串行状态,并传输到所述信号路径。5.根据权利要求4所述的存储器,其特征在于,所述存储器还包括:至少一个第一并行器和至少一个第二并行器;所述第一并行器,设置于所述信号路径和所述第一锁存区之间,分别耦接所述信号路径和所述第一锁存区,用于将所述信号路径传输的所述熔丝数据转化为并行状态,并传输到所述第一锁存区;所述第二并行器,设置于所述信号路径和所述第二锁存区之间,分别耦接所述信号路径和所述第二锁存区,用于将所述信号路径传输的所述熔丝数据转化为并行状态,并传输到所述第二锁存区。6.根据权利要求3所述的存储器,其特征在于,所述阵列区的数量为两个,包括:第一阵列区和第二阵列区;所述第一阵列区和所述第二阵列区沿所述第一方向相对设置;至少一个所述反熔丝阵列设置于所述第一阵列区和所述第二阵列区之间。7.根据权利要求6所述的存储器,其特征在于,所述反熔丝阵列的数量为一个;所述信号路径的数量为两条,包括:第一信号路径和第二信号路径;所述第一信号路径设置于所述第一阵列区的第三端;所述第一信号路径耦接所述反熔丝阵列,所述第一信号路径还分别耦接所述第一阵列区中的所述第一锁存区和所述第二锁

存区;所述第二信号路径设置于所述第二阵列区的第三端;所述第二信号路径耦接所述反熔丝阵列,所述第二信号路径还分别耦接所述第二阵列区中的所述第一锁存区和所述第二锁存区。8.根据权利要求6所述的存储器,其特征在于,所述反熔丝阵列的数量为两个,包括:第一反熔丝阵列和第二反熔丝阵列;所述信号路径的数量为四条,包括:第一信号路径、第二信号路径、第三信号路径和第四信号路径;所述第一信号路径设置于所述第一阵列区的第三端;所述第一信号路径耦接所述第一反熔丝阵列,所述第一信号路径还分别耦接所述第一阵列区中的所述第一锁存区和所述第二锁存区;所述第二信号路径设置于所述第二阵列区的第三端;所述第二信号路径耦接所述第一反熔丝阵列,所述第二信号路径还分别耦接所述第二阵列区中的所述第一锁存区和所述第二锁存区;所述第三信号路径设置于所述第一阵列区的第四端;所述第三信号路径耦接所述第二反熔丝阵列,所述第三信号路径还分别耦接所述第一阵列区中的所述第一锁存区和所述第二锁存区;所述第四信号路径设置于所述第二阵列区的第四端;所述第四信号路径耦接所述第二反熔丝阵列,所述第四信号路径还分别耦接所述第二阵列区中的所述第一锁存区和所述第二锁存区。9.根据权利要求3所述的存储器,其特征在于,所述阵列区的数量为一个;至少一个所述反熔丝阵列设置于靠近所述阵列区的第一端的一侧。10.根据权利要求9所述的存储器,其特征在于,所述反熔丝阵列的数量为一个;所述信号路径的数量为一条;所述信号路径设置于所述阵列区的第三端;所述信号路径耦接所述反熔丝阵列,所述信号路径还分别耦接所述阵列区中的所述第一锁存区和所述第二锁存区。11.根据权利要求9所述的存储器,其特征在于,所述反熔丝阵列的数量为两个,包括:第一反熔丝阵列和第二反熔丝阵列;所述信号路径的数量为两条,包括:第一信号路径和第二信号路径;所述第一信号路径设置于所述阵列区的第三端;所述第一信号路径耦接所述第一反熔丝阵列,所述第一信号路径还分别耦接所述阵列区中的所述第一锁存区和所述第二锁存区;所述第二信号路径设置于所述阵列区的第四端;所述第二信号路径耦接所述第二反熔丝阵列,所述第二信号路径还分别耦接所述阵列区中的所述第一锁存区和所述第二锁存区。12.根据权利要求4所述的存储器,其特征在于,所述反熔丝阵列发送的所述熔丝数据包括:2

i

个熔丝子数据;所述串行器包括:2

i

条子数据传输路径;2

i

条所述子数据传输路径,一一对应接收2

i

个所述熔丝子数据,以及,一一对应接收2

i

个子数据控制信号;每条所述子数据传输路径,用于响应于其对应接收的所述子数据控制信号,将其对应接收的所述熔丝子数据传输到所述串行器的输出端,以将所述反熔丝阵列

发送的所述熔丝数据转化为串行状态。13.根据权利要求12所述的存储器,其特征在于,所述串行器还包括:i个d锁存器和2

i

个与门单元;其中,第1个所述d锁存器的时钟输入端接收串行时钟信号;每个所述d锁存器的反相输出端电连接其数据输入端;每个所述d锁存器的同相输出端电连接下一个所述d锁存器的时钟输入端;每个所述与门单元的i个输入端,对应耦接i个d锁存器的同相输出端和反相输出端中的i个输出端;每两个所述与门单元之间至少有一个输入端连接至对应的所述d锁存器的不同输出端;2

i

个所述与门单元一一对应输出2

i

个所述子数据控制信号。14.根据权利要求12所述的存储器,其特征在于,所述串行器还包括:2

i

个子数据锁存器;2

i

个所述子数据锁存器的输出端一一对应耦接2

i

条所述子数据传输路径的输入端;2

i

个所述子数据锁存器,用于一一对应接收2

i

个所述熔丝子数据,将2

i

个所述熔丝子数据锁存并传输到2

i

条所述子数据传输路径。15.根据权利要求1至14任一项所述的存储器,其特征在于,所述存储器为动态随机存取存储器dram。

技术总结

本公开实施例公开了一种存储器,存储器包括至少一个阵列区;阵列区包括:存储体区、第一锁存区和第二锁存区;其中,第一锁存区耦接于存储体区的第一端,第二锁存区耦接于存储体区的第二端;存储体区的第一端和第二端为沿第一方向相对的两端;第一锁存区和第二锁存区,用于将熔丝数据锁存并传输到存储体区。本公开能够节省布线设置,减小熔丝数据在传输过程中的延迟和损耗,节约功耗。节约功耗。节约功耗。

技术研发人员:季汝敏

受保护的技术使用者:睿力集成电路有限公司

技术研发日:2022.08.17

技术公布日:2022/9/13

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。