技术特征:

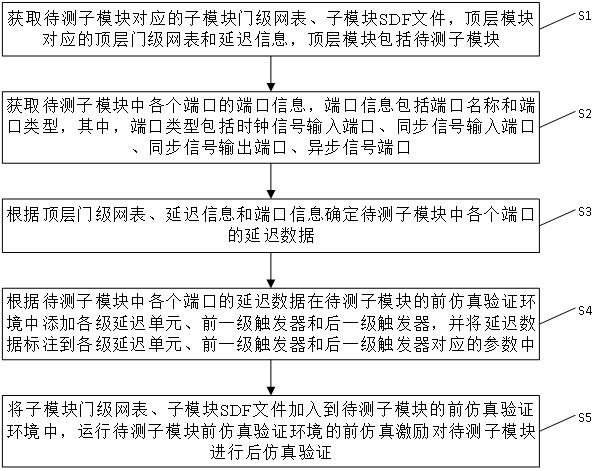

1.一种数字芯片的子模块后仿真方法,其特征在于,包括:获取待测子模块对应的子模块门级网表、子模块sdf文件,顶层模块对应的顶层门级网表和延迟信息,所述顶层模块包括待测子模块;获取待测子模块中各个端口的端口信息,所述端口信息包括端口名称和端口类型,其中,所述端口类型包括时钟信号输入端口、同步信号输入端口、同步信号输出端口、异步信号端口;根据所述顶层门级网表、延迟信息和端口信息确定待测子模块中各个端口的延迟数据,其中,时钟信号输入端口的延迟数据包括从时钟源到待测子模块的时钟信号输入端口路径上的各级延迟,同步信号输入端口的延迟数据包括前一级触发器延迟和从前一级触发器到待测子模块的同步信号输入端口路径上的各级延迟,同步信号输出端口的延迟数据包括同步信号输出端口到后一级触发器路径上的各级延迟和后一级触发器延迟,异步信号端口的延迟数据为无延迟;其中,各级延迟包括路径上每一级的单元延迟和走线延迟,前一级触发器延迟包括从时钟源到前一级触发器时钟端的延迟和从前一级触发器时钟端到前一级触发器输出端的延迟,后一级触发器延迟包括从时钟源到后一级触发器时钟端的延迟、后一级触发器的建立时间和保持时间;根据待测子模块中各个端口的延迟数据在待测子模块的前仿真验证环境中添加各级延迟单元、前一级触发器和后一级触发器,并将延迟数据标注到各级延迟单元、前一级触发器和后一级触发器对应的参数中;将子模块门级网表、子模块sdf文件加入到待测子模块的前仿真验证环境中,运行待测子模块前仿真验证环境的前仿真激励对待测子模块进行后仿真验证。2.根据权利要求1所述的数字芯片的子模块后仿真方法,其特征在于,当顶层模块中的所有子模块的输出级为寄存器输出时,在待测子模块前仿真验证环境中,将待测子模块对应的前一级触发器和前仿真验证环境中的驱动触发器作为同一个行为级单元,将前一级触发器对应的延迟标注到前仿真验证环境中的驱动触发器的输出端上。3.根据权利要求1所述的数字芯片的子模块后仿真方法,其特征在于,当同步信号输出端口对应多个后一级触发器时,同步信号输出端口的延迟数据包括输出端口到每一个后一级触发器路径上的各级延迟和每一个后一级触发器的延迟。4.根据权利要求3所述的数字芯片的子模块后仿真方法,其特征在于,运行待测子模块前仿真验证环境的前仿真激励对待测子模块进行后仿真验证的步骤之前,还包括:选取多个后一级触发器中的任意一个后一级触发器作为同步信号输出端口的采样触发器,剩余的后一级触发器作为检查触发器,采样触发器连接前仿真验证环境中的接口采样单元,每一个检查触发器分别连接一个第一检查器,所述第一检查器用于比对采样触发器和检查触发器的输出结果。5.根据权利要求1所述的数字芯片的子模块后仿真方法,其特征在于,后一级触发器包括建立时间触发器和保持时间触发器,并在数据路径和时钟路径上添加建立时间和保持时间,并将建立时间触发器和保持时间触发器中的其中一个触发器作为输出触发器,另一个触发器连接第二检查器,所述第二检查器用于检查建立时间和保持时间的时序。6.根据权利要求5所述的数字芯片的子模块后仿真方法,其特征在于,运行待测子模块前仿真验证环境的前仿真激励对待测子模块进行后仿真验证的步骤中,包括:

若延迟时间大于1个时钟周期减去后一级触发器建立时间并且延迟时间小于1个时钟周期加上后一级触发器保持时间, 则前仿真验证环境的功能检查器和后一级触发器中的第二检查器均报错,后仿真验证不通过;若延迟时间大于或者等于1个时钟周期加上后一级触发器保持时间,则前仿真验证环境的功能检查器报错,后一级触发器中的第二检查器不报错,后仿真验证不通过。7.根据权利要求6所述的数字芯片的子模块后仿真方法,其特征在于,运行待测子模块前仿真验证环境的前仿真激励对待测子模块进行后仿真验证的步骤中,还包括:若后一级触发器的数据信号发生建立时间违例,则数据变化滞后1个时钟周期被采样到;若后一级触发器的时钟信号发生保持时间违例,则数据变化超前1个时钟周期被采样到。8.一种数字芯片的子模块后仿真系统,其特征在于,包括:第一获取模块,用于获取待测子模块对应的子模块门级网表、子模块sdf文件,顶层模块对应的顶层门级网表和延迟信息,所述顶层模块包括待测子模块;第二获取模块,用于获取待测子模块中各个端口的端口信息,所述端口信息包括端口名称和端口类型,其中,所述端口类型包括时钟信号输入端口、同步信号输入端口、同步信号输出端口、异步信号端口;第一处理模块,用于根据所述顶层门级网表、延迟信息和端口信息确定待测子模块中各个端口的延迟数据,其中,时钟信号输入端口的延迟数据包括从时钟源到待测子模块的时钟信号输入端口路径上的各级延迟,同步信号输入端口的延迟数据包括前一级触发器延迟和从前一级触发器到待测子模块的同步信号输入端口路径上的各级延迟,同步信号输出端口的延迟数据包括同步信号输出端口到后一级触发器路径上的各级延迟和后一级触发器延迟,异步信号端口的延迟数据为无延迟;其中,各级延迟包括路径上每一级的单元延迟和走线延迟,前一级触发器延迟包括从时钟源到前一级触发器时钟端的延迟和从前一级触发器时钟端到前一级触发器输出端的延迟,后一级触发器延迟包括从时钟源到后一级触发器时钟端的延迟、后一级触发器的建立时间和保持时间;第二处理模块,用于根据待测子模块中各个端口的延迟数据在待测子模块的前仿真验证环境中添加各级延迟单元、前一级触发器和后一级触发器,并将延迟数据标注到各级延迟单元、前一级触发器和后一级触发器对应的参数中;第三处理模块,用于将子模块门级网表、子模块sdf文件加入到待测子模块的前仿真验证环境中,运行待测子模块前仿真验证环境的前仿真激励对待测子模块进行后仿真验证。9.一种计算机设备,其特征在于,包括:至少一个处理器,以及与所述至少一个处理器通信连接的存储器,其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器执行权利要求1-7中任一所述的数字芯片的子模块后仿真方法。10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机指令,所述计算机指令用于使所述计算机执行权利要求1-7中任一所述的数字芯片的子模块后仿真方法。

技术总结

本发明公开了一种数字芯片的子模块后仿真方法和系统,其中,方法包括获取待测子模块的子模块门级网表、子模块SDF文件、各个端口的端口信息,顶层模块的顶层门级网表和延迟信息;根据顶层门级网表、延迟信息和端口信息确定延迟数据;根据延迟数据在前仿真验证环境中添加各级延迟单元、前一级触发器和后一级触发器,将延迟数据标注到对应参数;将子模块门级网表、子模块SDF文件加入到前仿真验证环境中,运行前仿真激励进行后仿真验证。该方法在前仿真环境中标注与待测子模块端口相连接的前、后级模块的接口延迟和路径延迟,采用前仿真激励进行后仿真验证,使得待测子模块在后仿真时能够模拟接口延迟时序,待测子模块后仿验证更加全面。全面。全面。

技术研发人员:马飞 孙雷

受保护的技术使用者:北京数字光芯集成电路设计有限公司

技术研发日:2022.09.20

技术公布日:2022/10/25

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。