技术特征:

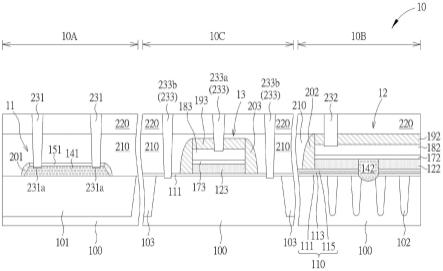

1.一种半导体存储器件,其特征在于包括:衬底,包括有源区以及多个绝缘区;电阻结构,设置在所述绝缘区上,所述电阻结构还包括:第一半导体层;第一盖层,设置在所述第一半导体层上;以及第一间隙壁,设置在所述第一半导体层与所述第一盖层的侧壁;位线结构,设置在所述衬底上并横跨所述有源区以及所述绝缘区,所述位线结构还包括:第二半导体层;第一导电层,设置在所述第二半导体层上;第二盖层,设置在所述第一导电层上;以及第二间隙壁,直接物理接触所述第二半导体层、所述第一导电层、所述第二盖层与所述第二间隙壁的侧壁;以及位线触点,设置在所述衬底内并部分伸入所述第二半导体层,其中,所述位线触点与所述第一半导体层包括彼此相同的半导体材质。2.依据权利要求1所述的半导体存储器件,其特征在于,所述电阻结构还包括第三半导体层,所述第一半导体层与所述第三半导体层分别包括不同的半导体材质,所述第三半导体层与所述第二半导体层包括彼此相同的半导体材质。3.依据权利要求2所述的半导体存储器件,其特征在于,所述第一半导体层镶嵌地设置在所述第三半导体层内并部分伸入所述衬底。4.依据权利要求3所述的半导体存储器件,其特征在于,还包括:多个插塞,分别电连接所述第一半导体层。5.依据权利要求3所述的半导体存储器件,其特征在于,还包括:多个插塞,分别电连接所述第三半导体层。6.依据权利要求3所述的半导体存储器件,其特征在于,所述第一半导体层包括相互分隔的多个部分。7.依据权利要求2所述的半导体存储器件,其特征在于,所述第三半导体层设置在所述第一半导体层上。8.依据权利要求7所述的半导体存储器件,其特征在于,还包括:多个插塞,分别电连接所述第一半导体层与所述第三半导体层。9.依据权利要求1所述的半导体存储器件,其特征在于,所述电阻结构还包括:第二导电层以及第三盖层,依序设置在所述第一盖层上,所述第三盖层与所述第二盖层包括相同的材质;以及多个插塞,设置在所述衬底上,所述插塞之一直接物理接触所述电阻结构的所述第一半导体层,所述插塞之另一直接物理接触所述位线结构的所述第一导电层。10.依据权利要求1所述的半导体存储器件,其特征在于,还包括:层间电介质层,设置在所述衬底上,所述层间电介质层的顶面齐平于所述第二盖层的顶面,并且完全覆盖所述电阻结构。11.依据权利要求1所述的半导体存储器件,其特征在于,所述第一间隙壁的顶面低于

所述第二间隙壁的顶面,所述第一盖层与所述第二盖层包括不同的材质。12.依据权利要求1所述的半导体存储器件,其特征在于,还包括:多个插塞,设置在所述衬底上,所述插塞之一直接物理接触所述电阻结构的所述第一半导体层,所述插塞之另一直接物理接触所述位线结构的所述第一导电层。13.一种半导体存储器件的制作方法,其特征在于包括:提供衬底,所述衬底包括有源区以及多个绝缘区;在所述绝缘区上形成电阻结构,所述电阻结构还包括:第一半导体层;第一盖层,形成在所述第一半导体层上;以及第一间隙壁,设置在所述第一半导体层与所述第一盖层的侧壁上;以及在所述衬底上形成位线结构并横跨所述有源区以及所述绝缘区,所述位线结构还包括:第二半导体层;第一导电层,形成在所述第二半导体层上;第二盖层,形成在所述第一导电层上;第二间隙壁,形成在所述第二半导体层、所述第一导电层与所述第二盖层的侧壁上;以及在所述衬底内形成位线触点,并部分伸入所述第二半导体层,其中,所述位线触点与所述第一半导体层包括彼此相同的半导体材质。14.依据权利要求13所述的半导体存储器件的制作方法,其特征在于,还包括:在所述衬底上依序形成半导体材料层、导体材料层、以及第一覆盖材料层,同时覆盖所述有源区以及所述绝缘区;在所述导体材料层形成前,在所述半导体材料层内形成触点开口,部分暴露出所述衬底;形成所述导体材料层,填满所述触点开口;以及在形成所述第一半导体层时,一并移除位在所述触点开口外的所述导体材料层,形成所述位线触点。15.依据权利要求14所述的半导体存储器件的制作方法,其特征在于,还包括:通过第一掩模层进行图案化制作工艺,图案化所述第一覆盖材料层以及所述导体材料层,形成所述第一盖层以及所述第一半导体层;移除所述第一掩模层;以及形成多个插塞,分别电连接所述第一半导体层与所述第一导电层。16.依据权利要求14所述的半导体存储器件的制作方法,其特征在于,还包括:在所述触点开口形成时,在所述半导体材料层内一并形成至少一开口,部分暴露出所述绝缘区;形成所述导体材料层,填满所述开口;以及在形成所述位线触点时,一并移除位在所述开口外的所述导体材料层,以在所述半导体材料层内形成所述第一半导体层,所述位线触点与所述第一半导体层包括相同的半导体材质。

17.依据权利要求16所述的半导体存储器件的制作方法,其特征在于,还包括:通过第一掩模层进行图案化制作工艺,图案化所述第一覆盖材料层以及所述半导体材料层,形成所述第一盖层以及第三半导体层,所述第一半导体层镶嵌地设置在所述第三半导体层内;移除所述第一掩模层;以及形成多个插塞,分别电连接所述第一半导体层或所述第三半导体层。18.依据权利要求14所述的半导体存储器件的制作方法,其特征在于,还包括:在衬底上依序形成导电材料层以及第二覆盖材料层;在所述衬底上形成第二掩模层;通过所述第二掩模层进行另一图案化制作工艺,图案化所述第二覆盖材料层与所述导电材料层,形成所述第二盖层与所述第一导电层;以及移除所述第二掩模层。19.依据权利要求18所述的半导体存储器件的制作方法,其特征在于,还包括:在所述衬底上形成多个插塞,所述插塞之一直接物理接触所述电阻结构的所述第一半导体层,所述插塞之另一直接物理接触所述位线结构的所述第一导电层。20.依据权利要求13所述的半导体存储器件的制作方法,其特征在于,还包括:在所述衬底上形成层间电介质层,所述层间电介质层的顶面齐平于所述第二盖层的顶面;以及进行沉积以及回蚀刻制作工艺,在所述衬底上同时形成所述第一间隙壁以及所述第二间隙壁。

技术总结

本发明公开了一种半导体存储器件及其制作方法,包括衬底,电阻结构,位线结构,与位线触点。衬底包括有源区与多个绝缘区。电阻结构设置在绝缘区上,并包括第一半导体层,第一盖层,与第一间隙壁。位线结构设置在衬底上、横跨有源区与绝缘区,并包括第二半导体层,第一导电层,第二盖层,与第二间隙壁。位线触点设置在衬底内并部分伸入第二半导体层,其中,位线触点与第一半导体层包括彼此相同的半导体材质。由此,可在简化制作工艺的前提下形成兼具结构可靠度与稳定表面电阻值的电阻器。可靠度与稳定表面电阻值的电阻器。可靠度与稳定表面电阻值的电阻器。

技术研发人员:永井享浩

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:2022.09.01

技术公布日:2022/11/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。