技术特征:

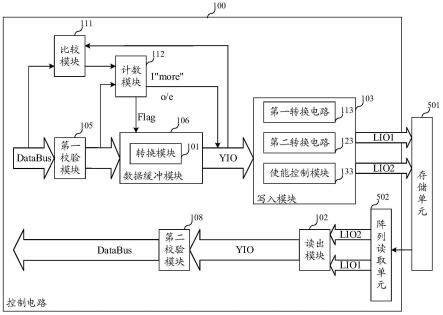

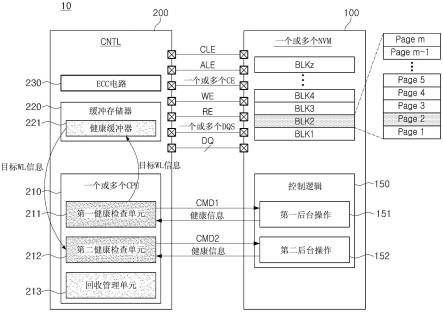

1.一种控制电路,用于向存储单元写入数据和读出数据,其特征在于,包括:外部数据线,用于接收原始数据和原始ecc校验码;第一校验模块,连接外部数据线,用于在数据传输发生错误,根据所述原始ecc校验码进行检错和/或纠错,并输出纠正后的数据和纠正后的ecc校验码,其中,若数据传输未发生错误,则所述纠正后的数据与所述原始数据一致,所述纠正后的ecc校验码与所述原始ecc校验码一致;比较模块,与外部数据线、全局数据线连接,用于逐位检测所述外部数据线当前传输的数据与所述全局数据线当前传输的数据是否相同,并输出每一位的检测结果;计数模块,与所述比较模块、所述第一校验模块连接,并接收切换控制信号,在所述切换控制信号为第一状态,用于对所述比较模块的输出结果进行统计,输出表征所述原始数据、所述原始ecc校验码与所述全局数据线当前传输的数据的差异位数是否超过第一预设值的第一控制信号;在所述切换控制信号为第二状态,用于对所述第一校验模块输出的所述纠正后的数据和所述纠正后的ecc校验码中高电平数据进行统计,输出表征所述高电平数据所占位数是否超过第二预设值的第二控制信号,并输出表征所述高电平数据数量为奇数或偶数的奇偶码;所述第二控制信号和所述奇偶码作为标记位数据存入所述存储单元中,以在读出数据的过程中,将所述第二控制信号和所述奇偶码读出;其中,所述第一控制信号用于在写操作中控制待写入的数据是否需要翻转、所述第二控制信号用于在读操作中控制待读出的数据是否需要翻转,所述奇偶码用于在读操作中对待读出的数据进行检错和/或纠错。2.根据权利要求1所述的控制电路,其特征在于,还包括:数据缓冲模块,与所述第一校验模块和所述计数模块连接,用于根据所述第一控制信号,将所述纠正后的数据和所述纠正后的ecc校验码传输至所述全局数据线或将所述纠正后的数据和所述纠正后的ecc校验码进行翻转后传输至所述全局数据线。3.根据权利要求2所述的控制电路,其特征在于,还包括:写入模块,连接在本地数据线和所述全局数据线之间,控制所述全局数据线中的数据传输至所述本地数据线,且基于第三控制信号,判断所述全局数据线中的数据传输至所述本地数据线的过程中是否进行数据翻转,其中,所述第三控制信号用于表征所述第一控制信号的值和所述第二控制信号的值是否相同。4.根据权利要求1所述的控制电路,其特征在于,还包括:阵列区读取单元,用于在读操作中将所述存储单元中的所述纠正后的数据、所述纠正后的ecc校验码、所述第二控制信号和所述奇偶码读出至本地数据线上,或在读操作中将所述存储单元中的所述纠正后的数据的相反值、所述纠正后的ecc校验码的相反值、所述第二控制信号和所述奇偶码读出至本地数据线。5.根据权利要求1所述的控制电路,其特征在于,还包括:第二校验模块,用于根据所述纠正后的ecc校验码和所述奇偶码判断所述纠正后的数据在存储期间是否发生错误,和/或对发生错误的所述纠正后的数据再次纠错;读出模块,用于根据读出的所述第二控制信号,控制本地数据线上的数据向后传输时是否需要翻转;若所述高电平数据所占位数超过所述第二预设值,则所述读出模块被配置为将本地数据线上的数据的相反值最终传输至所述第二校验模块;若所述高电平数据所占

位数不超过所述第二预设值,则所述读出模块被配置为将本地数据线上的数据最终传输至所述第二校验模块。6.根据权利要求2所述的控制电路,其特征在于,所述数据缓冲模块包括:转换模块,用于根据第一控制信号,控制所述纠正后的数据和纠正后的ecc校验码传输至所述全局数据线时是否需要翻转;若所述差异位数超过所述第一预设值,则所述转换模块被配置为将所述纠正后的数据和纠正后的ecc校验码翻转后传输至所述全局数据线;若所述差异位数不超过所述第一预设值,则所述转换模块被配置为将所述纠正后的数据和纠正后的ecc校验码传输至所述全局数据线。7.根据权利要求1所述的控制电路,其特征在于,所述逐位检测所述外部数据线当前传输的数据与所述全局数据线当前传输的数据是否相同,并输出每一位的检测结果,包括:若当前位所述外部数据线传输的数据与当前位所述全局数据线传输的数据不同,则生成第一子控制信号,若当前位所述外部数据线传输的数据与当前位所述全局数据线传输的数据相同,则生成第二子控制信号。8.根据权利要求7所述的控制电路,其特征在于,在所述切换控制信号为第一状态时,所述计数模块用于获取所述第一子控制信号和所述第二子控制信号,若所述第一子控制信号个数超过所述第一预设值,则生成所述第一控制信号,所述第一预设值为所述第一子控制信号的数量与所述第二子控制信号的数量和的预设百分比。9.根据权利要求8所述的控制电路,其特征在于,所述预设百分比为50%。10.根据权利要求1所述的控制电路,其特征在于,所述第二预设值为所述纠正后的数据和所述纠正后的ecc校验码的位数和的50%。11.根据权利要求3所述的控制电路,其特征在于,所述写入模块包括;使能控制模块,用于接收所述第一控制信号和所述第二控制信号,并输出用于表征所述第一控制信号和所述第二控制信号是否相同的第三控制信号。12.根据权利要求11所述的控制电路,其特征在于,所述使能控制模块还用于接收写使能信号,若所述写使能信号为有效电平,则输出用于表征所述第一控制信号和所述第二控制信号是否相同的所述第三控制信号。13.根据权利要求11所述的控制电路,其特征在于,本地数据线包括互为差分数据传输线的第一本地数据线和第二本地数据线;所述全局数据线中的数据传输至所述本地数据线的过程中进行数据翻转,包括:所述写入模块被配置为将所述全局数据线中的数据翻转后传输至所述第一本地数据线,和/或所述写入模块被配置为将所述全局数据线中的数据传输至所述第二本地数据线。14.根据权利要求13所述的控制电路,其特征在于,所述写入模块,还包括:包括第一mos管、第二mos管和第三mos管的第一转换电路;所述第一mos管的栅极接收所述第三控制信号,源极连接所述全局数据线,漏极连接所述第一本地数据线;所述第二mos管的栅极连接所述全局数据线,漏极连接所述第二本地数据线,源极连接所述第三mos管的漏极;所述第三mos管的栅极接收第三控制信号,源极接地。15.根据权利要求13所述的控制电路,其特征在于,所述写入模块,还包括:

包括第四mos管、第五mos管和第六mos管的第二转换电路;所述第四mos管的栅极接收第四控制信号,源极连接所述全局数据线,漏极连接所述第二本地数据线,所述第三控制信号和所述第四控制信号互为反相信号;所述第五mos管的栅极连接所述全局数据线,漏极连接所述第一本地数据线,源极连接所述第六mos管的漏极;所述第六mos管的栅极接收所述第四控制信号,源极接地。16.根据权利要求5所述的控制电路,其特征在于,所述读出模块连接在所述本地数据线与所述全局数据线之间,用于根据第二控制信号,控制所述本地数据线和所述全局数据线之间的数据传输,若所述高电平数据所占位数超过所述第二预设值,则所述读出模块被配置为将所述本地数据线中的数据的相反值传输至所述全局数据线;若所述高电平数据所占位数不超过所述第二预设值,则所述读出模块被配置为将所述本地数据线中的数据传输至所述全局数据线。17.根据权利要求5所述的控制电路,其特征在于,所述读出模块连接所述全局数据线与所述第二校验模块,用于根据第二控制信号,控制所述全局数据线和所述第二校验模块之间的数据传输,所述高电平数据所占位数超过所述第二预设值,所述读出模块被配置为将所述全局数据线中的数据翻转后传输至所述第二校验模块;所述高电平数据所占位数不超过所述第二预设值,所述读出模块被配置为将所述全局数据线中的数据传输至所述第二校验模块。18.根据权利要求6所述的控制电路,其特征在于,所述转换模块包括:第一传输元件,一端通过反相器连接所述第一校验模块,另一端连接所述全局数据线;第二传输元件,一端连接所述第一校验模块,另一端连接所述全局数据线;所述第一传输元件和所述第二传输元件还用于接收所述第一控制信号,用于根据所述第一控制信号选择导通所述第一传输元件或所述第二传输元件。19.一种存储器,其特征在于,包括上述权利要求1~18任一项所述的控制电路,还包括:存储单元,连接本地数据线,所述本地数据线用于向所述存储单元写入数据和读出数据。

技术总结

本申请实施例提供一种控制电路和存储器,控制电路包括:外部数据线,用于接收原始数据和原始ECC校验码;第一校验模块,用于在数据传输发生错误,根据原始ECC校验码进行检错和/或纠错,并输出纠正后的数据和纠正后的ECC校验码;比较模块,用于逐位检测外部数据线的数据与全局数据线的数据是否相同,并输出检测结果;计数模块,接收切换控制信号,在切换控制信号为第一状态,用于对比较模块的输出结果进行统计,输出第一控制信号;在切换控制信号为第二状态,用于对第一校验模块输出的纠正后的数据和纠正后的ECC校验码中高电平数据进行统计,输出第二控制信号和奇偶码;本申请实施例旨在降低数据传输线路的低功耗和提高数据存储的可靠性等。储的可靠性等。储的可靠性等。

技术研发人员:何军 应战

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.06.01

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。