技术特征:

1.一种摄像元件,具备:半导体基板,设置有电荷积蓄区域;第1光电转换部,包括第1对置电极、第1像素电极、以及位于所述第1对置电极与所述第1像素电极之间的第1光电转换层;以及第2光电转换部,包括第2对置电极、第2像素电极、以及位于所述第2对置电极与所述第2像素电极之间的第2光电转换层,该第2光电转换部位于所述第1光电转换部与所述半导体基板之间,所述电荷积蓄区域与所述第1像素电极及所述第2像素电极电连接。2.如权利要求1所述的摄像元件,所述摄像元件具备特定插塞,所述特定插塞将所述第1像素电极、所述第2像素电极及所述电荷积蓄区域电连接。3.如权利要求2所述的摄像元件,所述特定插塞包括第1部分及第2部分,在所述特定插塞中,所述第1部分从所述第2像素电极朝向所述第1像素电极延伸,在所述特定插塞中,所述第2部分从所述第2像素电极朝向所述电荷积蓄区域延伸,在平面图中,所述第1部分中的靠所述第2像素电极侧的端部与所述第2部分中的靠所述第2像素电极侧的端部相互相离。4.如权利要求2或者3所述的摄像元件,所述特定插塞与所述第2对置电极被电分离。5.如权利要求2至4中任一项所述的摄像元件,在所述第2光电转换层的与厚度方向垂直的截面中,所述特定插塞比所述第2光电转换层的外轮廓位于外侧。6.如权利要求2至5中任一项所述的摄像元件,所述特定插塞包括第1部分,所述第1部分从所述第1像素电极延伸到所述第2像素电极,存在多个具备所述电荷积蓄区域、所述特定插塞、所述第1光电转换部和所述第2光电转换部的像素,所述多个像素包括第1像素及第2像素,在平面图中,所述第1像素及所述第2像素在第1方向上相邻,所述第1像素的所述第1部分在第2方向上的位置与所述第2像素的所述第1部分在所述第2方向上的位置相同。7.如权利要求2至5中任一项所述的摄像元件,所述特定插塞包括第1部分,所述第1部分从所述第1像素电极延伸到所述第2像素电极,存在多个具备所述电荷积蓄区域、所述特定插塞、所述第1光电转换部和所述第2光电转换部的像素,所述多个像素包括第1像素及第2像素,在平面图中,

所述第1像素及所述第2像素在第1方向上相邻,所述第1像素的所述第1部分在第2方向上的位置与所述第2像素的所述第1部分在所述第2方向上的位置不同。8.如权利要求2至7中任一项所述的摄像元件,所述特定插塞包括第1部分及第2部分,所述第1部分从所述第1像素电极延伸到所述第2像素电极,在所述特定插塞中,所述第2部分从所述第2像素电极朝向所述电荷积蓄区域延伸,所述第1部分的截面积在包括所述第1部分的靠所述第2像素电极侧的端部的区域中随着从所述第1像素电极接近所述第2像素电极而连续地变小,所述第2部分中的靠所述第2像素电极侧的端部的截面积比所述第1部分中的靠所述第2像素电极侧的端部的截面积大。9.如权利要求8所述的摄像元件,所述第1部分的截面积从靠所述第1像素电极侧的端部直到靠所述第2像素电极侧的端部随着从所述第1像素电极接近所述第2像素电极而连续地变小。10.如权利要求8或者9所述的摄像元件,所述第2部分的靠所述第2像素电极侧的端部的截面积相对于所述第1部分的靠所述第2像素电极侧的端部的截面积的比率比1大且比1.2小。11.如权利要求2至10中任一项所述的摄像元件,在将所述特定插塞中的从所述第1像素电极到所述第2像素电极的部分的长度定义为第1长度,且将所述特定插塞中的从所述第2像素电极到所述半导体基板的部分的长度定义为第2长度时,所述第1长度比所述第2长度长。12.如权利要求2至10中任一项所述的摄像元件,在将所述特定插塞中的从所述第1像素电极到所述第2像素电极的部分的长度定义为第1长度,且将所述特定插塞中的从所述第2像素电极到所述半导体基板的部分的长度定义为第2长度时,所述第1长度比所述第2长度短。13.如权利要求2至12中任一项所述的摄像元件,在将所述特定插塞中的从所述第1像素电极到所述第2像素电极的部分的长度定义为第1长度,将所述特定插塞中的从所述第2像素电极到所述半导体基板的部分的长度定义为第2长度,且将所述特定插塞中的在所述半导体基板的内部延伸的部分的长度定义为第3长度时,所述第3长度比所述第1长度或者所述第2长度长。14.如权利要求13所述的摄像元件,所述第3长度比所述第1长度与所述第2长度的合计长。

15.如权利要求1至14中任一项所述的摄像元件,所述摄像元件是背面照射型。16.如权利要求1至15中任一项所述的摄像元件,所述第1光电转换层通过光电转换来生成第1电荷,所述第2光电转换层通过光电转换来生成第2电荷,所述第1像素电极包括使所述第1电荷积蓄至所述第1光电转换层的第1积蓄电极、以及第1读出电极,所述第2像素电极包括使所述第2电荷积蓄至所述第2光电转换层的第2积蓄电极、以及第2读出电极,所述电荷积蓄区域与所述第1读出电极及所述第2读出电极电连接。17.如权利要求1至16中任一项所述的摄像元件,所述第1光电转换层对第1波段的光进行光电转换,所述第2光电转换层对第2波段的光进行光电转换。18.一种摄像装置,具备:如权利要求1至17中任一项所述的摄像元件;以及电压供给电路,对所述第1对置电极及所述第2对置电极的电压进行调整。19.如权利要求18所述的摄像装置,所述电压供给电路具有与所述第1对置电极及所述第2对置电极连接的可变电压源。20.如权利要求18所述的摄像装置,所述电压供给电路具有:第1可变电压源,与所述第2对置电极连接;以及第2可变电压源,与所述第1对置电极连接。21.如权利要求18至20中任一项所述的摄像装置,所述电压供给电路通过对所述第1对置电极及所述第2对置电极的电压进行调整从而实现:许可所述第1光电转换层中的光电转换而且禁止所述第2光电转换层中的光电转换的第1状态;以及禁止所述第1光电转换层中的光电转换而且许可所述第2光电转换层中的光电转换的第2状态。22.如权利要求21所述的摄像装置,存在多个具备所述电荷积蓄区域、所述第1光电转换部和所述第2光电转换部的像素,所述多个像素包括第1像素及第2像素,在第1时刻,在所述第1像素中实现所述第1状态,在所述第2像素中实现所述第2状态。23.如权利要求22所述的摄像装置,在第2时刻,在所述第1像素中实现所述第2状态,在所述第2像素中实现所述第1状态。

24.如权利要求1至17中任一项所述的摄像元件,还具备:第3光电转换部,包括第3对置电极、第3像素电极、以及位于所述第3对置电极与所述第3像素电极之间的第3光电转换层,该第3光电转换部位于所述第2光电转换部与所述半导体基板之间,所述第1光电转换层对第1波段的光进行光电转换,所述第2光电转换层对第2波段的光进行光电转换,所述第3光电转换层对第3波段的光进行光电转换,存在多个具备所述电荷积蓄区域、所述第1光电转换部、所述第2光电转换部和所述第3光电转换部的像素,所述多个像素包括第1像素、第2像素、第3像素及第4像素,所述第1像素、所述第2像素、所述第3像素及所述第4像素构成像素层,在平面图中,所述第1像素及所述第2像素在第1方向上相邻,所述第3像素及所述第4像素在所述第1方向上相邻,所述第1像素及所述第3像素在第2方向上相邻,所述第2像素及所述第4像素在所述第2方向上相邻。25.一种摄像装置,具备:如权利要求24所述的摄像元件;以及电压供给电路,由所述电压供给电路使所述第1像素、所述第2像素、所述第3像素及所述第4像素各自中的所述第1对置电极、所述第2对置电极及所述第3对置电极的电压变化,从而执行如下层旋转:关于在第1期间中所述第1像素所呈现的对于光的灵敏度,使得在接续于所述第1期间的第2期间中所述第2像素呈现该灵敏度,在接续于所述第2期间的第3期间中所述第4像素呈现该灵敏度,在接续于所述第3期间的第4期间中所述第3像素呈现该灵敏度,关于在所述第1期间中所述第2像素所呈现的对于光的灵敏度,使得在所述第2期间中所述第4像素呈现该灵敏度,在所述第3期间中所述第3像素呈现该灵敏度,在所述第4期间中所述第1像素呈现该灵敏度,关于在所述第1期间中所述第4像素所呈现的对于光的灵敏度,使得在所述第2期间中所述第3像素呈现该灵敏度,在所述第3期间中所述第1像素呈现该灵敏度,在所述第4期间中所述第2像素呈现该灵敏度,关于在所述第1期间中所述第3像素所呈现的对于光的灵敏度,使得在所述第2期间中所述第1像素呈现该灵敏度,在所述第3期间中所述第2像素呈现该灵敏度,在所述第4期间中所述第4像素呈现该灵敏度。26.一种摄像系统,具备:如权利要求24所述的摄像元件或者如权利要求25所述的摄像装置;以及信号处理装置,存在多个所述像素层,在所述多个像素层各自中,所述第1像素具有灵敏度的光的波段、所述第2像素具有灵

敏度的光的波段、所述第3像素具有灵敏度的光的波段及所述第4像素具有灵敏度的光的波段中的至少1个在生成某帧时与生成别的帧时不同,所述信号处理装置生成将所述某帧与所述别的帧合成的合成帧,在所述合成帧的某区域中,出现基于所述某帧的像,在所述合成帧的别的区域中,出现基于所述别的帧的像。

技术总结

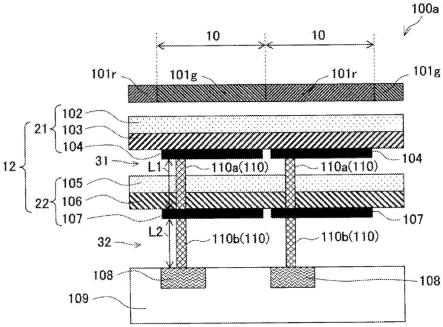

摄像元件(100a)具备半导体基板(109)、第1光电转换部(21)和第2光电转换部(22)。在半导体基板(109)设置有电荷积蓄区域(108)。第2光电转换部(22)位于第1光电转换部(21)与半导体基板(109)之间。第1光电转换部(21)包括第1对置电极(102)、第1像素电极(104)和第1光电转换层(103)。第1光电转换层(103)位于第1对置电极(102)与第1像素电极(104)之间。第2光电转换部(22)包括第2对置电极(105)、第2像素电极(107)和第2光电转换层(106)。第2光电转换层(106)位于第2对置电极(105)与第2像素电极(107)之间。电荷积蓄区域(108)与第1像素电极(104)及第2像素电极(107)电连接。像素电极(107)电连接。像素电极(107)电连接。

技术研发人员:西谷贵幸 太田宗吾 三宅康夫 佐藤好弘 西村佳寿子 小林努

受保护的技术使用者:松下知识产权经营株式会社

技术研发日:2021.05.21

技术公布日:2023/1/31

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。