一种微机电系统封装结构及其制备方法

- 国知局

- 2024-07-27 12:37:20

1.本发明属于微机电系统封装技术领域,更具体地,涉及一种微机电系统封装结构及其制备方法。背景技术:2.在经过了半个多世纪的发展之后,微机电系统(micro‑electro‑mechanical system,mems)的市场不断增长,前景令人鼓舞。封装是微机电系统工程化的关键步骤,是保证其高可靠性的重要条件。封装既能保护微机电系统芯片,又可以实现芯片与外界环境的电气连接,但封装mems的工艺一直存在各种各样的难题。3.对于大部分mems来说,由于其结构精细、容易破损断裂,通常会采用单个芯片进行键合封装。然而,这种单个芯片封装方法导致整个芯片的费用昂贵,限制了芯片的多样化,在良率和产能方面也很难突破。技术实现要素:4.针对现有技术的缺陷,本发明的目的在于提供一种微机电系统封装结构,通过在硅基底背面设置一定厚度的金属层用以固定mems器件薄弱结构,可实现晶圆片封装键合后再划片,旨在解决现有技术中采用先划片再键合工艺导致mems器件芯片成本高、产能低的问题。5.为实现上述目的,本发明提供了一种微机电系统封装结构,其包括硅基底、在所述硅基底上图案化制备得到的mems器件结构,以及用于对所述mems器件结构进行键合封装的盖板;6.所述硅基底背面还依次设置有第二金属层和第一金属层,所述第一金属层和第二金属层的总厚度不低于5μm;所述第一金属层和第二金属层采用的金属种类相同或不同;所述第一金属层和第二金属层用于保护所述mems器件结构在键合封装时不受破坏,同时用于释放刻蚀过程中产生的热量。7.优选地,所述第一金属层的厚度大于所述第二金属层的厚度。8.优选地,所述第一金属层的厚度为5μm‑10μm,所述第二金属层的厚度为200nm‑800nm。9.优选地,所述第一金属层采用的材料为铝、铬、铜、金中的一种或多种,所述第二金属层采用的材料为铝、铬、铜、金中的一种或多种。10.优选地,所述盖板为硅基板。11.按照本发明的另一个方面,提供了一种微机电系统封装结构的制备方法,包括如下步骤:12.在硅基底正面图案化制备mems器件结构;13.在硅基底背面形成第二金属层;14.在第二金属层背面形成第一金属层;15.在硅基底正面刻蚀该mems器件结构;16.将硅基底和盖板键合封装,再划片;17.去除硅基底背面的第一金属层和第二金属层。18.优选地,通过溅射法、热蒸发法或电子束蒸发法形成第二金属层。19.优选地,通过电镀工艺形成第一金属层。20.优选地,通过深等离子体刻蚀工艺刻蚀mems器件结构。21.优选地,采用激光划片机进行划片。22.总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:23.(1)本发明通过在硅基底背面设置一定厚度的金属层,可以固定刻蚀后硅基底正面的mems器件结构,同时由于金属具有良好的导热性,可以释放刻蚀过程中产生的热量,进一步保护mems器件结构不会因为温度过高而受损。24.(2)本发明通过先在硅基底背面沉积金属层后再进行刻蚀,然后依次进行整片封装键合和划片的工艺,针对mems器件复杂结构可实现晶圆级封装,该封装方法不仅可以提高封装效率,也可以降低购买封装模具的成本。25.(3)本发明采用硅基板替代普通玻璃板作为封装盖板,可以采用激光划片机进行划片,利用高能激光束照射待切割处,使被照射区域局部熔化、气化,从而达到划片的目的,这种划片方式由于是非接触式的,对内部器件本身无机械冲压力,进一步保护了器件的精细结构。附图说明26.图1是本发明实施例提供的一种微机电系统封装结构的示意图,其中:1‑第一金属层,2‑第二金属层,3‑硅基底,4‑mems器件结构,41‑mems器件中的薄弱结构,5‑盖板。27.图2是本发明对比例提供的一种加速度计封装结构的示意图,其中:2’‑铝层,3’‑硅基片,4’‑加速度计器件结构,41’‑加速度计器件中的薄弱结构,5’‑玻璃盖板,6’‑硅基托片,7’‑光刻胶。具体实施方式28.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。29.本发明提供的一种mems器件封装结构,结合图1所示,其包括硅基底3、mems器件结构4和盖板5,所述mems器件结构4由在所述硅基底3上图案化制备得到,所述盖板5用于对所述mems器件结构4进行键合封装。所述mems器件结构4可以为mems加速度计的内部器件结构、微振子的内部器件结构、mems压力传感器的内部器件结构、mems陀螺仪的内部器件结构等。由于mems器件中的薄弱结构41很细,例如mems加速度计中的弹簧,在划片过程中可能因轻微的碰撞而出现断裂,就会使弹簧上的走线断开,实现不了信号的检测。本发明通过在所述硅基底背面设置一定厚度的金属层,用于释放刻蚀过程中产生的热量以及固定刻蚀后的mems器件中的薄弱结构41。具体地,所述硅基底3背面依次设置有第二金属层2和第一金属层1,所述第一金属层1和第二金属层2的总厚度不低于5μm,所述第一金属层1和第二金属层2采用的金属种类可以相同,也可以不同。30.一些实施例中,所述第一金属层1、第二金属层2均采用导热性能好、耐高温、硬度大的金属材料,优选铝、铬、铜、金中的一种或多种。所述第一金属层1的厚度大于所述第二金属层2的厚度,进一步优选地,所述第一金属层1的厚度为5μm‑10μm,所述第二金属层2的厚度为200nm‑800nm。31.一些实施例中,所述盖板5为硅基板,使得微机电系统封装结构制备过程中可以采用激光划片机进行划片。32.本发明还提供了一种mems器件封装结构的制备方法,包括如下步骤:33.在硅基底3正面图案化制备mems器件结构4;34.在硅基底3背面形成第二金属层2;35.在第二金属层2背面形成第一金属层1;36.在硅基底3正面刻蚀该mems器件结构4;37.将硅基底3和盖板5键合封装,再划片;38.去除硅基底背面的第一金属层1和第二金属层2。39.一些实施例中,通过溅射法、热蒸发法或电子束蒸发法形成第二金属层2,所述第二金属层2采用的材料为铝、铬、铜、金中的一种或多种,第二金属层2的厚度为200nm‑800nm。40.一些实施例中,通过电镀工艺形成第一金属层1,所述第一金属层1采用的材料为铝、铬、铜、金中的一种或多种,第一金属层1的厚度为5μm‑10μm。电镀工艺采用自组装设备,通过固定电压的方式,调整电镀时间达到控制膜厚的效果。41.一些实施例中,采用匀胶、光刻、显影、镀膜、剥离等工艺在硅基底3上制备相应图案。42.一些实施例中,采用匀胶、光刻、显影、电镀等工艺在盖板5上制备相应图案,盖板5上承载有封装焊料,以使硅基底3与盖板5进行键合封装。43.本发明所述硅基底3或盖板5表面图案制备中,匀胶为常规的旋涂方式,一般pr胶厚度为5μm‑9μm;光刻设备主要采用ma6和直写式曝光机。44.一些实施例中,采用深等离子体刻蚀工艺刻蚀mems器件结构,精准控制结构尺寸,刻蚀精度高。45.一些实施例中,采用激光划片机进行划片,通过高温融化待切割处,这种设备振动较小,更加保护mems器件精细结构不受损坏。46.一些实施例中,通过湿法刻蚀工艺去除第二金属层2和第一金属层1。湿法刻蚀选择性好、重复性好、生产效率高、成本低。47.以下结合具体实施例,对上述技术方案详细说明。48.实施例49.本实施例以封装mems加速度计为例,提供一种加速度计封装结构,依次堆叠的第一金属铝层、第二金属铝层、硅基底、加速度计器件结构和硅基盖板,所述第一金属铝层、第二金属铝层、硅基底和硅基盖板的厚度分别为5μm、400nm、500μm、500μm。50.上述加速度计封装结构的具体制备流程如下:51.s1、在硅基底正面图案化并制备加速度计器件结构,具体包括如下步骤:52.s1.1、起始硅基底厚度:500μm,其表面热氧化层(不导电衬底)厚度:300nm;53.s1.2、对硅基底进行有机洗及氧等离子体清洗;54.s1.3、采用英国oxford公司生产的plasmapro 80pecvd等离子体增强化学气相沉积系统,沉积200nm厚度的二氧化硅薄膜,沉积步骤的工艺参数为:温度为300℃,沉积速率为50nm/min,沉积时间为4min;55.s1.4、采用电子束蒸发在二氧化硅表面镀铬100nm,镀膜速率56.s1.5、采用匀胶机匀胶8μm,采用ma6进行光刻;57.s1.6、刻蚀铬和二氧化硅,该二氧化硅和铬作为欧姆层;58.s1.7、在所述欧姆层上沉积双金属复合层,步骤如下:采用电子束蒸发在欧姆层表面依次镀铬20nm,速率镀金200nm,镀铬可以用来增加金和二氧化硅之间的粘附性;59.s1.8、采用数控匀胶旋涂仪在双金属复合层涂覆pi胶,厚度为10μm;60.s1.9、梯度升温进行烘烤处理;61.s1.10、在pi胶上再重复沉积双金属复合层。62.s2、在有热氧化层的硅基底背面制作沉积第二金属铝层,具体包括如下步骤:63.s2.1、对硅基底背面进行有机洗及氧等离子体清洗;64.s2.2、采用电子束蒸发沉积第二金属铝层400nm,镀膜速率65.s3、在第二金属铝层背面制作第一金属铝层,具体包括如下步骤:66.s3.1、使用绝缘胶带将硅基底正面加速度计金属结构均覆盖;67.s3.2、采用电镀方式镀第一金属铝层:设置电源0.2781ma,恒压为5v进行电镀,电镀厚度为5μm;68.s3.3、采用去离子水清洗并烘干。69.s4、采用stps设备对加速度计器件结构进行深硅刻蚀,器件结构中弹簧振子对应的区域刻穿,使得弹簧能够自由振动。70.s5、浸泡丙酮≥12h,剥离内部结构表面光刻胶。71.s6、硅基盖板厚度:500μm,在硅基盖板正面制作柱子,其背面制备识别mark。72.s7、采用真空键合机将硅基底和硅基盖板键合封装。73.s8、采用激光划片机对上述晶圆片进行切割成单个芯片。74.s9、采用湿法刻蚀工艺去除芯片背面第一金属铝层。75.s10、将上述芯片浸泡显影液去除背面第二金属铝层。76.对比例77.本对比例以封装mems加速度计为例,提供一种加速度计封装结构,如图2所示,包括依次堆叠的硅基托片6’、光刻胶7’、铝层2’、硅基片3’、加速度计器件结构4’和玻璃盖板5’。所述硅基托片6’、光刻胶7’、铝层2’、硅基片3’和玻璃盖板5’的厚度分别为500μm、4μm、400nm、500μm、500μm。78.上述加速度计封装结构的具体制备流程如下:79.s1、提供硅基片3’厚度:500μm,其表面热氧化层(不导电衬底)厚度:300nm;同本发明实施例,在硅基片3’正面图案化并制备加速度计器件结构4’。80.s2、同本发明实施例,在硅基片3’背面制作沉积铝层2’。81.s3、提供硅基托片6’厚度:500μm,其表面热氧化层(不导电衬底)厚度:200nm。82.s4、采用匀胶机在硅基托片6’表面涂覆光刻胶7’4μm,预烘烤120℃/5min。83.s5、铝层2’和光刻胶7’贴合后,置于stps设备中抽真空处理使其紧密贴合。84.s6、采用stps设备对加速度计器件结构4’进行深硅刻蚀。85.s7、浸泡丙酮24h,剥离硅基托片6’。86.s8、浸泡显影液去除铝层2’,形成单个芯片。87.s9、提供玻璃盖板5’厚度:500μm,在玻璃盖板5’正面制作柱子。88.s10、采用划片机将玻璃盖板5’进行划片处理。89.s11、采用倒装贴合设备将划片后的玻璃盖板5’和单个芯片键合。90.本发明为了降低微机电系统封装结构制备成本、提高封装效率和产能,采用晶圆封装再划片切割成单个芯片的工艺。但是,结合图1和图2所示,用对比例中现有的封装结构,由于硅基片3’背面铝层2’太薄,在丙酮去胶过程中,该铝层很容易起泡变形,减小了其和硅基底之间的附着力,使得该铝层容易脱落,形成单个芯片,无法实现晶圆级封装;同时,薄铝层脱落后,加速度计器件中的薄弱结构41’底部没有固定,仅靠上部与其他结构连接,在键合、划片过程中很容易移动或受到外力作用而断裂。因此,本发明实施例在硅基底3背面设置了一定厚度的金属层,由于刻蚀时会将硅基底刻穿,硅基底背面较厚的金属层可以很好地固定mems器件结构(包括器件中的薄弱结构41),且浸泡丙酮时不会影响到金属层与硅基底连接的界面,这样就能够实现先键合封装再划片切割;同时,金属层具有良好的导热性,可以释放刻蚀过程中产生的热量,很好地保护mems内部器件结构。91.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122761.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

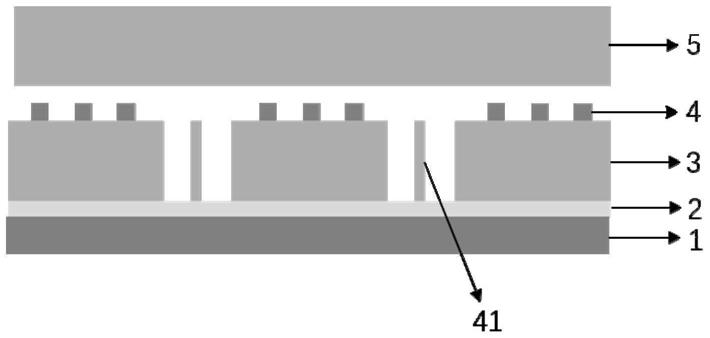

返回列表