MEMS器件及其制造方法与流程

- 国知局

- 2024-07-27 12:57:07

本发明涉及半导体,特别涉及一种mems器件及其制造方法。

背景技术:

1、在常规的惯性器件中,z轴检测单元在上下活动的过程中,极限条件下会存在与限位结构和防粘连结构接触的问题。

2、如图1所示,惯性器件包括相键合的第一衬底11和第二衬底12,第一衬底11包括半导体基底111、与半导体基底111电连接的导电结构112、可动质量块113和防粘连结构114,防粘连结构114位于可动质量块113的底面,第二衬底12中形成有限位结构121;其中,可动质量块113和防粘连结构114为一体结构,第二衬底12和限位结构121为一体结构,且材质均为半导体材料。当对惯性器件通电测试时,可动质量块113会上下活动,极限条件下会导致可动质量块113与限位结构121之间、防粘连结构114与导电结构112之间接触,从而导致测试电荷被导出,进而导致测试失效,且影响器件的可靠性。

3、因此,如何避免测试失效,且提高器件的可靠性是目前亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种mems器件及其制造方法,能够避免测试失效,且提高器件的可靠性。

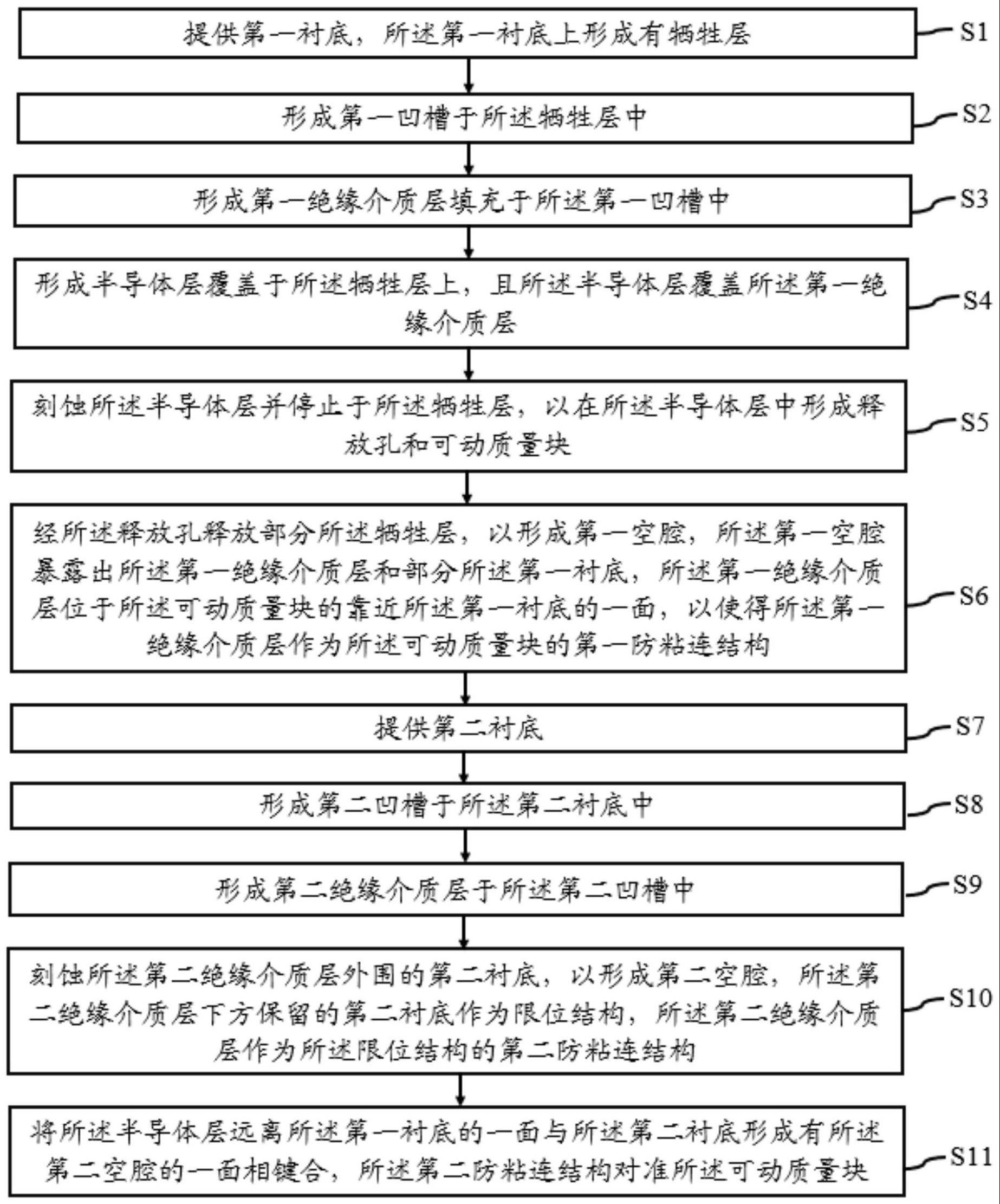

2、为实现上述目的,本发明提供了一种mems器件的制造方法,包括:

3、提供第一衬底,所述第一衬底上形成有牺牲层;

4、形成第一凹槽于所述牺牲层中;

5、形成第一绝缘介质层填充于所述第一凹槽中;

6、形成半导体层覆盖于所述牺牲层上,且所述半导体层覆盖所述第一绝缘介质层;

7、刻蚀所述半导体层并停止于所述牺牲层,以在所述半导体层中形成释放孔和可动质量块;

8、经所述释放孔释放部分所述牺牲层,以形成第一空腔,所述第一空腔暴露出所述第一绝缘介质层和部分所述第一衬底,所述第一绝缘介质层位于所述可动质量块的靠近所述第一衬底的一面,以使得所述第一绝缘介质层作为所述可动质量块的第一防粘连结构;

9、提供第二衬底;

10、形成第二凹槽于所述第二衬底中;

11、形成第二绝缘介质层于所述第二凹槽中;

12、刻蚀所述第二绝缘介质层外围的第二衬底,以形成第二空腔,所述第二绝缘介质层下方保留的第二衬底作为限位结构,所述第二绝缘介质层作为所述限位结构的第二防粘连结构;

13、将所述半导体层远离所述第一衬底的一面与所述第二衬底形成有所述第二空腔的一面相键合,所述第二防粘连结构对准所述可动质量块。

14、可选地,所述第一衬底包括半导体基底和覆盖于所述半导体基底上的第三绝缘介质层,所述第三绝缘介质层中形成有与所述半导体基底连接的导电结构;所述第一空腔暴露出所述第三绝缘介质层和所述导电结构,暴露出的所述导电结构与所述第一防粘连结构对准。

15、可选地,所述第一绝缘介质层的顶面与所述第一凹槽外围的牺牲层的顶面之间的高度差小于1500埃。

16、可选地,所述第二绝缘介质层的顶面低于所述第二凹槽外围的第二衬底的顶面。

17、可选地,在刻蚀所述第二绝缘介质层外围的第二衬底之后,所述mems器件的制造方法还包括:

18、形成气体吸收层于所述第二空腔的底壁上。

19、可选地,在形成所述半导体层覆盖于所述牺牲层上之后且在刻蚀所述半导体层并停止于所述牺牲层之前,所述mems器件的制造方法还包括:

20、形成第一键合环于所述半导体层上;

21、在形成所述第二绝缘介质层于所述第二凹槽中之后且在刻蚀所述第二绝缘介质层外围的第二衬底之前,所述mems器件的制造方法还包括:

22、形成第二键合环于所述第二衬底上;

23、所述将所述半导体层远离所述第一衬底的一面与所述第二衬底形成有所述第二空腔的一面相键合包括:将所述半导体层远离所述第一衬底的一面与所述第二衬底形成有所述第二空腔的一面通过所述第一键合环和所述第二键合环相键合。

24、可选地,在将所述半导体层远离所述第一衬底的一面与所述第二衬底形成有所述第二空腔的一面相键合之前,所述mems器件的制造方法还包括:

25、形成挡墙主体于所述第二衬底的靠近所述第二键合环的表面上。

26、可选地,在形成所述挡墙主体于所述第二衬底的靠近所述第二键合环的表面上之后,所述mems器件的制造方法还包括:

27、形成挡墙保护层于所述挡墙主体的表面。

28、可选地,所述挡墙主体与所述第二绝缘介质层同时形成,所述挡墙保护层与所述第二键合环同时形成。

29、本发明还提供一种mems器件,包括:

30、第一衬底,所述第一衬底上形成有牺牲层和半导体层,所述半导体层覆盖所述牺牲层,所述牺牲层中形成有第一空腔,所述半导体层中形成有释放孔和可动质量块,所述释放孔与所述第一空腔连通,所述可动质量块的靠近所述第一衬底的一面形成有第一绝缘介质层,所述第一空腔暴露出所述第一绝缘介质层和部分所述第一衬底,所述第一绝缘介质层作为所述可动质量块的第一防粘连结构;

31、第二衬底,键合于所述半导体层上,所述第二衬底靠近所述半导体层的一面形成有第二空腔,所述第二空腔与所述释放孔连通,所述第二空腔中形成有限位结构,所述限位结构与所述第二衬底为一体结构且向所述半导体层方向延伸,所述限位结构靠近所述半导体层的一端形成有第二绝缘介质层,所述第二绝缘介质层作为所述限位结构的第二防粘连结构,所述第二防粘连结构对准所述可动质量块。

32、可选地,所述第一衬底包括半导体基底和覆盖于所述半导体基底上的第三绝缘介质层,所述第三绝缘介质层中形成有与所述半导体基底连接的导电结构;所述第一空腔暴露出所述第三绝缘介质层和所述导电结构,暴露出的所述导电结构与所述第一防粘连结构对准。

33、可选地,所述第一绝缘介质层远离所述第一衬底的一面与所述牺牲层远离所述第一衬底的一面之间的高度差小于1500埃。

34、可选地,所述第二绝缘介质层靠近所述半导体层的一面高于所述第二空腔外围的第二衬底靠近所述半导体层的一面。

35、可选地,所述mems器件还包括:

36、气体吸收层,形成于所述第二空腔的底壁上。

37、可选地,所述mems器件还包括:

38、第一键合环,形成于所述半导体层远离所述第一衬底的一面上;

39、第二键合环,形成于所述第二衬底靠近所述半导体层的一面上,所述半导体层远离所述第一衬底的一面与所述第二衬底靠近所述半导体层的一面通过所述第一键合环和所述第二键合环相键合。

40、可选地,所述mems器件还包括:

41、挡墙主体,形成于所述第二衬底的靠近所述第二键合环的表面上。

42、可选地,所述mems器件还包括:

43、挡墙保护层,形成于所述挡墙主体的表面。

44、可选地,所述挡墙主体与所述第二绝缘介质层的材质相同,所述挡墙保护层与所述第二键合环的材质相同。

45、与现有技术相比,本发明的技术方案具有以下有益效果:

46、1、本发明的mems器件的制造方法,通过提供第一衬底,所述第一衬底上形成有牺牲层;形成第一凹槽于所述牺牲层中;形成第一绝缘介质层填充于所述第一凹槽中;形成半导体层覆盖于所述牺牲层上,且所述半导体层覆盖所述第一绝缘介质层;刻蚀所述半导体层并停止于所述牺牲层,以在所述半导体层中形成释放孔和可动质量块;经所述释放孔释放部分所述牺牲层,以形成第一空腔,所述第一空腔暴露出所述第一绝缘介质层和部分所述第一衬底,所述第一绝缘介质层位于所述可动质量块的靠近所述第一衬底的一面,以使得所述第一绝缘介质层作为所述可动质量块的第一防粘连结构;提供第二衬底;形成第二凹槽于所述第二衬底中;形成第二绝缘介质层于所述第二凹槽中;刻蚀所述第二绝缘介质层外围的第二衬底,以形成第二空腔,所述第二绝缘介质层下方保留的第二衬底作为限位结构,所述第二绝缘介质层作为所述限位结构的第二防粘连结构;将所述半导体层远离所述第一衬底的一面与所述第二衬底形成有所述第二空腔的一面相键合,所述第二防粘连结构对准所述可动质量块,使得在避免所述可动质量块与其上下的结构粘连的同时,还能使得所述可动质量块与其上下的结构之间绝缘,进而避免测试电荷被导出,从而避免导致测试失效,提高了器件的可靠性。

47、2、本发明的mems器件,由于包括:第一衬底,所述第一衬底上形成有牺牲层和半导体层,所述半导体层覆盖所述牺牲层,所述牺牲层中形成有第一空腔,所述半导体层中形成有释放孔和可动质量块,所述释放孔与所述第一空腔连通,所述可动质量块的靠近所述第一衬底的一面形成有第一绝缘介质层,所述第一空腔暴露出所述第一绝缘介质层和部分所述第一衬底,所述第一绝缘介质层作为所述可动质量块的第一防粘连结构;第二衬底,键合于所述半导体层上,所述第二衬底靠近所述半导体层的一面形成有第二空腔,所述第二空腔与所述释放孔连通,所述第二空腔中形成有限位结构,所述限位结构与所述第二衬底为一体结构且向所述半导体层方向延伸,所述限位结构靠近所述半导体层的一端形成有第二绝缘介质层,所述第二绝缘介质层作为所述限位结构的第二防粘连结构,所述第二防粘连结构对准所述可动质量块,使得在避免所述可动质量块与其上下的结构粘连的同时,还能使得所述可动质量块与其上下的结构之间绝缘,进而避免测试电荷被导出,从而避免导致测试失效,提高了器件的可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240726/124323.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表