图像传感器像素阵列及图像传感器的制作方法

- 国知局

- 2024-07-31 18:57:29

本发明涉及图像传感器,特别涉及一种图像传感器及图像传感器。

背景技术:

1、互补金属氧化物半导体(cmos)图像传感器是使用互补金属氧化物半导体的固态感测装置。与电荷耦合器件(ccd)图像传感器相比,cmos图像传感器具有更低的制造成本和更低的功耗。因此,cmos图像传感器用于包括诸如智能电话和数码相机为例的便携式装置的各种电子装置。

2、在cmos图像传感器中,为了使每一个像素能接收更多的从镜头出射的光线避免浪费,提高对光线的利用率并提高图像质量,每个像素的最上面设置一个微透镜来汇聚光线,这些微透镜称为ocl(on chip lens,芯片内透镜)。

3、而利用cmos图像传感器上的微透镜阵列收集光线,通过分析不同像素位置接收到的光的相位差异来实现自动对焦的技术称为mlpd(microlens phase detection,微透镜相位检测),mlpd是一种相位检测自动对焦技术,能够更快地实现对焦,并且在低光条件下也可以提供更好的性能。

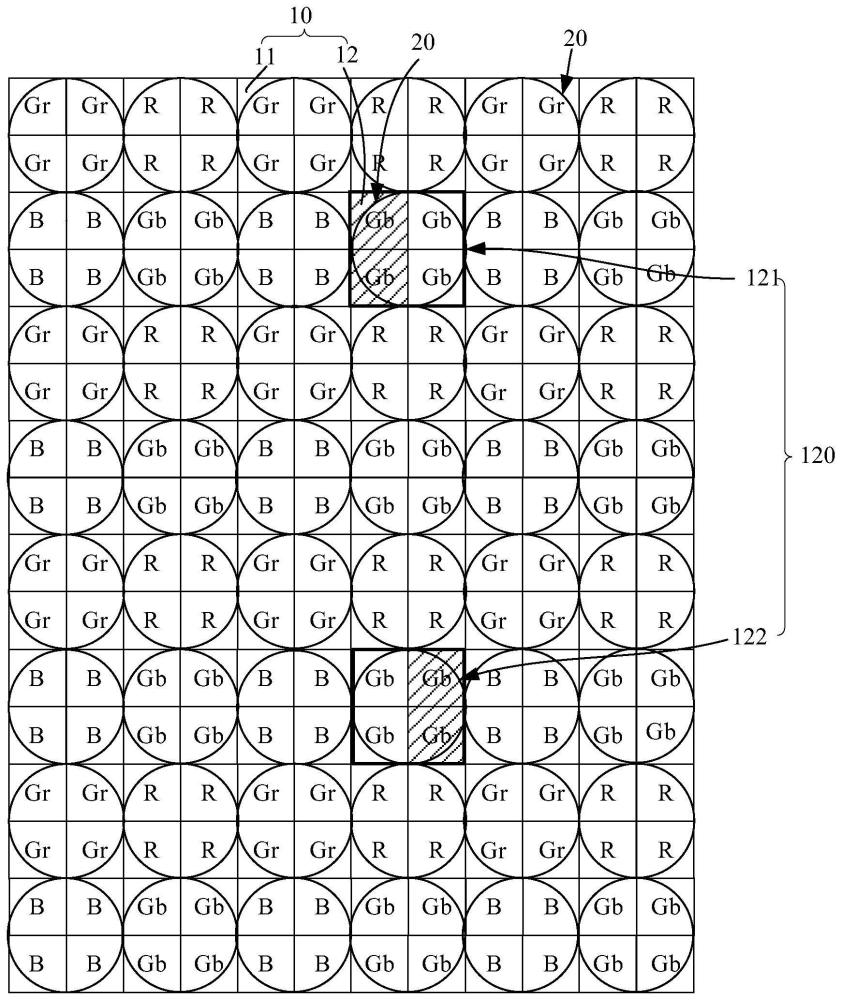

4、对于大多数小尺寸像素的cmos图像传感器而言,目前市场上的产品通常使用2×2mlpd和1×1ocl的像素阵列,如图1所示。请参考图1所示,像素阵列包括沿行方向和列方向规则排列的多个像素单元10,所述像素单元10上设置有微透镜20,其中所述像素单元10包括用于收集图像信息的图像像素单元11与用于收集相位信息以用来聚焦的相位像素单元12,每个所述图像像素单元11上均设置一个微透镜20,四个相邻所述相位像素单元12(即2×2)共用一个微透镜20。因此,该像素阵列表示为2×2mlpd(此处,mlpd表示用于做相位对焦用的微透镜)和1×1ocl(此处ocl表示正常的用于图像显示的微透镜)。

5、关于1×1ocl,尽管非mlpd区域(未设置mlpd的区域,例如图1中的除去区域30之外的区域)的图像比全尺寸模式下的2×2ocl更好,但是对于小像素,它仍然需要qsc(quadsensitivity correction,四重灵敏度校正)和线性补偿。此外,对于1×1ocl也存在一些缺点,例如:1)mlpd区域(图1中的区域30)处的图像由于丢失的4个像素值而更差,需要pdc(pdpixel correction,pd像素校正)来补偿丢失的像素以及周围的像素;2)在4c binning(装仓)模式下,灵敏度和量子效率都较小,snr10(信噪比)差约7%;3)需要同时使用pdc与pdf(pd pixel fix,pd像素修复),并且会导致芯片尺寸变大。

6、图2是2×2mlpd与2×2ocl的像素阵列示意图。请参考图2所示,2×2个图像像素单元11上共用一个微透镜20,2×2个相位像素单元12共用一个微透镜20。2×2mlpd与2×2ocl的像素阵列在mlpd区域(即图2中的区域30)具有与2×2mlpd和1×1ocl像素阵列相似的性能,其存在的缺点也类似。

技术实现思路

1、本发明的目的在于提供一种图像传感器像素阵列及图像传感器,使得相位像素单元所在区域没有丢失的像素,使得图像传感器的图像质量更好,并且不需要pdc。

2、为解决上述技术问题,根据本发明的第一个方面,提供了一种图像传感器像素阵列,包括:

3、沿行方向和列方向规则排列的多个像素单元,所述像素单元包括图像像素单元与相位像素单元,所述图像像素单元用于收集图像信息,所述相位像素单元用于收集相位信息以用来聚焦;

4、微透镜,设置于所述像素单元上,多个所述图像像素单元共用一个所述微透镜,多个所述相位像素单元共用一个所述微透镜,共用所述微透镜的像素单元的数量相同;共用一个所述微透镜的多个所述相位像素单元构成第一相位像素单元组或第二相位像素单元组,所述第一相位像素单元组与所述第二相位像素单元组位于不同行且同一列中,且所述第一相位像素单元组与所述第二相位像素单元组构成相位像素单元对以获得相位差异。

5、可选的,2×2个所述图像像素单元共用一个所述微透镜,2×2个所述相位像素单元共用一个所述微透镜。

6、可选的,采用所述第一相位像素单元组中的第一列或第二列的两个所述相位像素单元获得相位,采用所述第二相位像素单元组中的第二列或第一列的两个所述相位像素单元获得相位。

7、可选的,在所述像素单元与所述微透镜之间还设置有滤色器,2×2个像素单元共用一种颜色的滤色器,同时共用一个所述微透镜。

8、可选的,共用一个所述微透镜的2×2个像素单元合并以一个像素的模式读出时,所述第一相位像素单元组中的第一列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号不同,所述第二相位像素单元组中的第二列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号不同。

9、可选的,每个所述像素单元均以一个像素的模式读出时,所述第一相位像素单元组中的第一列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号相同,所述第二相位像素单元组中的第二列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号相同。

10、可选的,列方向上,多个所述相位像素单元对间隔设置,行方向上,多个相位像素单元组间隔设置。

11、可选的,所述像素阵列包括沿行方向和列方向重复排列的多个重复单元,所述重复单元内,设置有所述相位像素单元组的相邻列上,所述相位像素单元组位于不同行。

12、可选的,所述像素阵列包括沿行方向和列方向重复排列的多个重复单元,所述重复单元内,设置有所述相位像素单元对的相邻行上,所述相位像素单元对位于不同列。

13、为解决上述技术问题,根据本发明的第二个方面,还提供了一种图像传感器,包括如上所述的图像传感器像素阵列。

14、综上所述,在本发明提供的图像传感器像素阵列及图像传感器中,多个所述图像像素单元共用一个所述微透镜,多个所述相位像素单元共用一个所述微透镜,共用所述微透镜的像素单元的数量相同;共用一个所述微透镜的多个所述相位像素单元构成第一相位像素单元组或第二相位像素单元组,所述第一相位像素单元组与所述第二相位像素单元组位于不同行且同一列中,且所述第一相位像素单元组与所述第二相位像素单元组构成相位像素单元对以获得相位差异。本发明中共用同一微透镜的相位像素单元与共用同一微透镜的图像像素单元的数量相同,从而所有的像素单元可以使用相同的微透镜,相位像素单元所在区域没有丢失的像素值,从而使得图像传感器的图像质量更好,同时也不需要pdc。另外,第一相位像素单元组与第二相位像素单元组设置在不同行中,可以在没有额外读出定时的情况下读出,无需额外的读出时间。

15、另外,在4c binning模式下,只需要pdf,从而使得芯片的尺寸更小。

技术特征:1.一种图像传感器像素阵列,其特征在于,包括:

2.根据权利要求1所述的图像传感器像素阵列,其特征在于,2×2个所述图像像素单元共用一个所述微透镜,2×2个所述相位像素单元共用一个所述微透镜。

3.根据权利要求2所述的图像传感器像素阵列,其特征在于,采用所述第一相位像素单元组中的第一列或第二列的两个所述相位像素单元获得相位,采用所述第二相位像素单元组中的第二列或第一列的两个所述相位像素单元获得相位。

4.根据权利要求3所述的图像传感器像素阵列,其特征在于,在所述像素单元与所述微透镜之间还设置有滤色器,2×2个像素单元共用一种颜色的滤色器,同时共用一个所述微透镜。

5.根据权利要求4所述的图像传感器像素阵列,其特征在于,共用一个所述微透镜的2×2个像素单元合并以一个像素的模式读出时,所述第一相位像素单元组中的第一列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号不同,所述第二相位像素单元组中的第二列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号不同。

6.根据权利要求4所述的图像传感器像素阵列,其特征在于,每个所述像素单元均以一个像素的模式读出时,所述第一相位像素单元组中的第一列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号相同,所述第二相位像素单元组中的第二列的两个所述相位像素单元的tx控制信号与同一行中其余的所述图像像素单元的tx控制信号相同。

7.根据权利要求1所述的图像传感器像素阵列,其特征在于,列方向上,多个所述相位像素单元对间隔设置,行方向上,多个相位像素单元组间隔设置。

8.根据权利要求7所述的图像传感器像素阵列,其特征在于,所述像素阵列包括沿行方向和列方向重复排列的多个重复单元,所述重复单元内,设置有所述相位像素单元组的相邻列上,所述相位像素单元组位于不同行。

9.根据权利要求7所述的图像传感器像素阵列,其特征在于,所述像素阵列包括沿行方向和列方向重复排列的多个重复单元,所述重复单元内,设置有所述相位像素单元对的相邻行上,所述相位像素单元对位于不同列。

10.一种图像传感器,其特征在于,包括如权利要求1~9中任一项所述的图像传感器像素阵列。

技术总结本发明提供一种图像传感器像素阵列及图像传感器,所述像素阵列包括:沿行方向和列方向规则排列的多个像素单元,像素单元包括图像像素单元与相位像素单元;微透镜,设置于像素单元上,多个图像像素单元共用一个微透镜,多个相位像素单元共用一个微透镜,共用微透镜的像素单元的数量相同;共用一个微透镜的多个相位像素单元构成第一相位像素单元组或第二相位像素单元组,第一相位像素单元组与第二相位像素单元组位于不同行且同一列中,构成相位像素单元对以获得相位差异。本发明中可以使用相同的微透镜,相位像素单元所在区域没有丢失的像素值,从而使得图像传感器的图像质量更好,同时也不需要PDC。另外,相位像素单元无需额外的读出时间。技术研发人员:吴锴元受保护的技术使用者:北京弘图半导体有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181113.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。