一种基于自激活阻变器件的物理不可克隆函数的实现方法与流程

- 国知局

- 2024-07-31 19:27:29

本发明属于半导体(semiconductor)和cmos混合集成电路,具体涉及一种具有高安全性和高可靠性的基于自激活忆阻器的物理不可克隆函数的实现方法。

背景技术:

1、信息技术的不断进步推动了物联网等领域的快速发展,促进了智能设备规模的空前扩张,同时也使得硬件安全问题日益严重。传统的硬件安全保护系统主要基于互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)技术实现,因此面积较大,且对工艺、电源和温度等参数变化的敏感性较高。这些问题限制了传统硬件安全系统的进一步发展。

2、过渡金属氧化物型忆阻器结构简单,面积较小,耐久性强,能耗较低,同时制备工艺与cmos兼容,因此得到了众多关注。由于制备工艺的偏差和导电细丝型的阻变机理,过渡金属氧化物型忆阻器在开关时间和操作电压等方面存在不可避免的本征波动。这些波动可作为理想的随机源,基于十字交叉阵列结构,用于硬件安全系统的实现。与传统的硬件安全系统相比,忆阻器阵列型安全系统在面积和功耗等方面优势明显,并且通过增大阵列规模,可有效提升系统的抗攻击能力。

3、然而,随着阵列规模增大,1r型忆阻器阵列会不可避免地出现串扰和泄漏电流问题,使得忆阻器型物理不可克隆函数的可靠性严重下降。为提升可靠性,研究者们提出了以“选择管+忆阻器”为基本结构的新型阵列。其中以mos管作为选择单元的1t1r结构阵列,通过在栅极施加电压即可实现忆阻器件的选通,有效抑制阵列的串扰和泄漏电流问题,提升物理不可克隆函数的可靠性。然而,随着cmos器件尺寸微缩能力逐渐到达极限,1t1r型忆阻器阵列集成潜力逐渐降低,应用于安全系统时,难以满足更高的安全需求。因此,亟需新的同时提升忆阻器型物理不可克隆函数安全性和可靠性的新方案。

技术实现思路

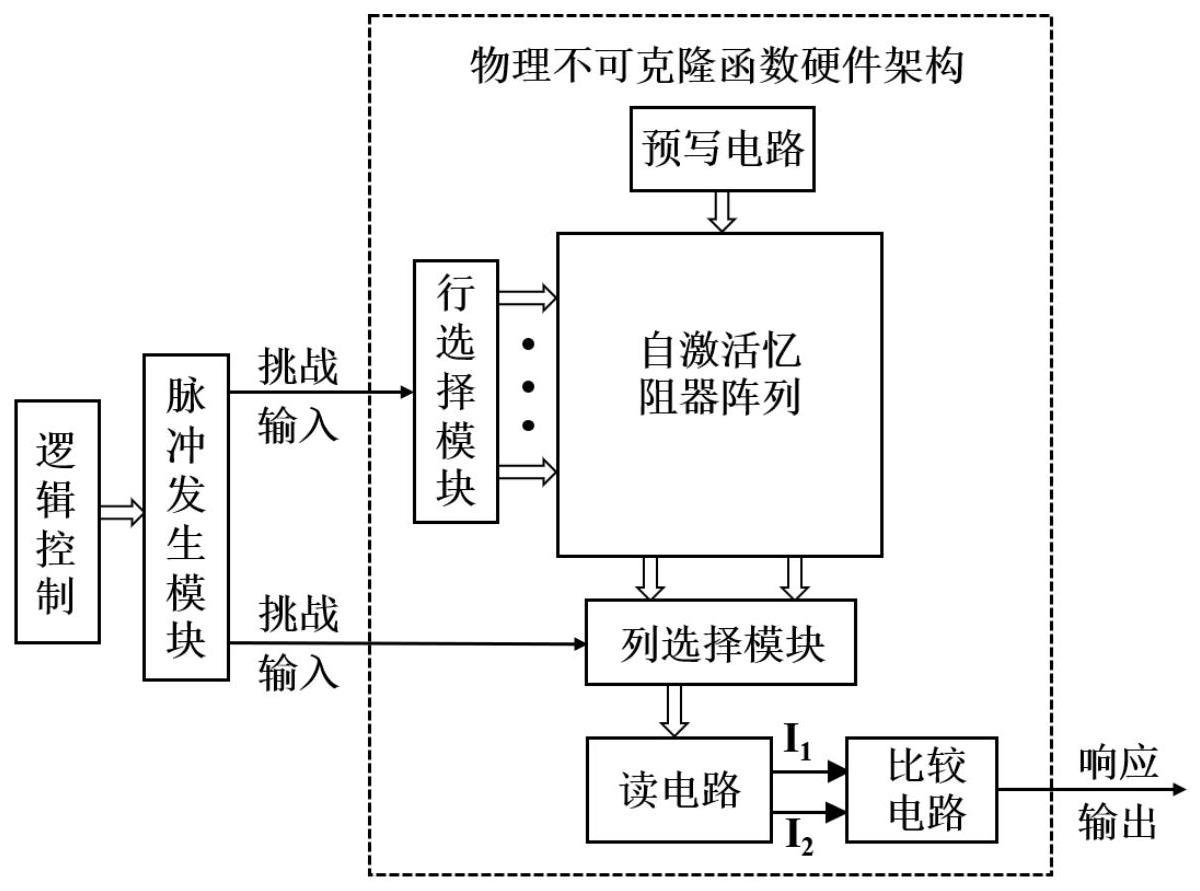

1、为了有效实现忆阻器型物理不可克隆函数的安全性和可靠性的协同优化,本发明提出了一种基于自激活忆阻器的新型物理不可克隆函数实现方法。

2、本发明提供的技术方案如下:

3、一种基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,采用1r结构的忆阻器阵列,该阵列的字线和位线互相垂直交叉,交叉点处为自激活忆阻器,所述自激活忆阻器包括顶电极、介质层和底电极,其中介质层由具有选择特性的阻变材料和具有存储特性的阻变材料上下叠加构成,具体步骤如下:

4、1)在忆阻器阵列中选择要写入的自激活忆阻器,施加脉冲信号,使该自激活忆阻器的介质层中的选择特性的材料层处于低阻态,进而改变介质层中存储特性材料层的阻值;

5、2)统计忆阻器阵列中自激活忆阻器的存储特性材料阻值的分布,设定参考阻值为阻值分布中的中间值,当存储特性材料的阻值大于该参考阻值时,将自激活忆阻器的存储特性材料层置为高阻态;当存储特性材料的阻值小于该参考阻值时,将自激活忆阻器的存储特性材料层为低阻态。设定的参考阻值使得忆阻器阵列中自激活忆阻器的存储特性材料处于高阻态和低阻态各占50%;

6、3)当忆阻器阵列有m条字线,n条位线时,物理不可克隆函数的挑战为m+n位,其中前m位用于字线的选择,有m/2位为1,m/2位为0,后n位用于位线的选择,前n/2位有1位为1,后n/2位有1位为1;

7、4)对于任意的挑战,使用m/2个周期完成全部响应的产生,共产生m/2个响应位,每个周期中,选择前m位挑战中的1个“1”挑战,用于对应行的选通;同时根据后n位中的2个“1”挑战,选通对应的两列;

8、5)分别读出选通的自激活忆阻器的电流,其中第m行第n1列的自激活忆阻器的电流i1和第m行第n2列的自激活忆阻器的电流i2,比较i1和i2的大小,当i1=i2时,输出响应为1;当i1≠i2时,输出响应为0,以此类推,得到全部的m/2位响应值,实现物理不可克隆函数。

9、优选的,所述自激活忆阻器的结构是金属-绝缘体-绝缘体-金属电容结构,或金属-半导体-半导体-金属电容结构等。

10、优选的,所述自激活忆阻器电极为金属材料,通过半导体工艺实现;所述电极可采用多种金属材料,如pt、al、au、w、cu和tin等。

11、优选的,所述选择特性介质层采用具有优良阈值转换特性的过渡金属氧化物,如vox、nbox等;所述存储特性介质层采用具有优良非易失阻变特性的过渡金属氧化物,如taox、hfox、alox等。

12、本发明采用自激活忆阻器件同时具有优异的存储特性和选择特性,因此只有在达到阈值电压时,才可以对器件进行写入、擦除和读取的操作。基于该器件的阵列无需集成晶体管即可抑制串扰和泄漏电流问题,可靠性高,集成潜力大,因此可有效提升物理不可克隆函数的安全性和可靠性。

技术特征:1.一种基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,采用1r结构的忆阻器阵列,该阵列的字线和位线互相垂直交叉,交叉点处为自激活忆阻器,所述自激活忆阻器包括顶电极、介质层和底电极,其中介质层由具有选择特性的阻变材料和具有存储特性的阻变材料上下叠加构成,具体步骤如下:

2.如权利要求1所述的基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,设定的参考阻值使得忆阻器阵列中自激活忆阻器的存储特性材料处于高阻态和低阻态各占50%。

3.如权利要求1所述的基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,所述自激活忆阻器结构是金属-绝缘体-绝缘体-金属电容结构,或是金属-半导体-半导体-金属电容结构。

4.如权利要求1所述的基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,所述顶电极或底电极采用pt、al、au、w、cu或tin材料。

5.如权利要求1所述的基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,所述具有选择特性的阻变材料为vox或nbox。

6.如权利要求1所述的基于自激活忆阻器的物理不可克隆函数实现方法,其特征在于,所述具有存储特性的阻变材料为taox、hfox或alox。

技术总结本发明公开一种基于自激活阻变器件的物理不可克隆函数的实现方法,属于半导体(semiconductor)和CMOS混合集成电路技术领域。本发明利用自激活忆阻器件同时具有优异的存储特性和选择特性,只有在达到阈值电压时,才对器件进行写入、擦除和读取的操作。本发明无需集成晶体管即可抑制串扰和泄漏电流问题,可靠性高,集成潜力大,因此可有效提升物理不可克隆函数的安全性和可靠性。技术研发人员:蔡一茂,吴林东,王宗巍,王源,黄如受保护的技术使用者:北方集成电路技术创新中心(北京)有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182568.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表