一种DDR存储器信号完整性非接触式测试评估方法与流程

- 国知局

- 2024-07-31 20:00:09

本发明属于嵌入式计算,具体涉及一种ddr存储器信号完整性非接触式测试评估方法。

背景技术:

1、在嵌入式电子系统的微型化方面,微系统技术得到了越来越多的重视,而sip和soc是微系统实现的两种重要技术途径。伴随着微组装技术的发展,将不同类型的器件和电路芯片叠在一起,构建成更为复杂的、完整的系统,其集成方式更灵活,在研发周期、成本方面具有优势。

2、随着嵌入式产品向微纳尺寸发展,包括信号完整性在内的电磁可靠性等技术越来越被重视。但微系统芯片的信号完整性评估是一难点,由于裸芯进行了封装,示波器探针测量变得困难,对其信号完整性的评估缺少如示波器仪器测量“眼图”一样有效显性化的方式。

技术实现思路

1、有鉴于此,本发明提供一种ddr存储器信号完整性非接触式测试评估方法,解决基于zynq+ddr设计平台的微系统芯片信号完整性评估难题,在不用示波器等仪器,而用软件模拟眼图的方式评估设计的信号完整性。

2、本发明的技术方案是:

3、一种ddr存储器信号完整性非接触式测试评估方法,设置测试目标电路非接触式测试所述ddr存储器的信号完整性;所述测试目标电路至少包括:具有ddr3控制器的处理器芯片以及ddr3存储器;测试目标电路为sip微系统芯片或嵌入式电路;处理器芯片的zynq控制ddr3进行读写方存,ddr3的时钟频率范围为800mhz─1600mhz、容量1gb─8gb。

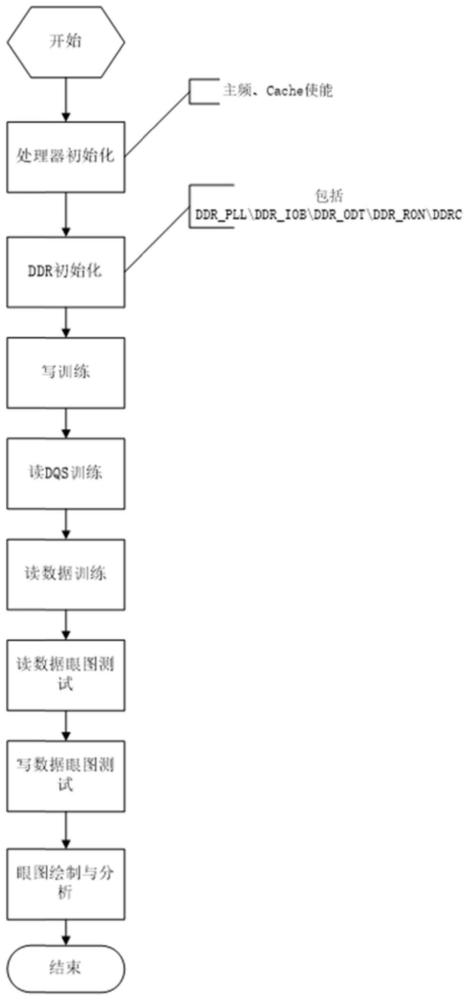

4、在所述测试目标电路中设置第一测试软件控制调整所述ddr3控制器,对ddr3存储器进行软件眼图测试前进行初始化和时序训练;

5、在所述测试目标电路中设置第二测试软件控制调整ddr3控制器,对ddr3存储器进行读数据眼图测试、写数据眼图测试。

6、进一步的,基于所述第一测试软件对所述ddr3存储器进行软件眼图测试前进行初始化和时序训练的方法包括以下步骤:

7、s101:初始化时钟寄存器ddr_pll。

8、s102:初始化阻抗调整寄存器ddr_iob\ddr_odt\ddr_ron。

9、s103:初始化控制寄存器ddrc。

10、s104:对ddr进行软复位。

11、s105:启动ddr读写时序训练;

12、其中:所述读写时序训练包括写训练、读dqs训练以及读数据训练。

13、进一步的,所述写训练具体为:调整dqs信号与时钟clk的相位关系,延迟dq信号以对齐和匹配电路板时延,ddr异步反馈clk,采样与dqs的上升沿,通过dq总线,控制器反复延迟dqs,直到检测到从0到1的过程。

14、进一步的,所述读dqs训练具体为:调整有效的读操作dqs窗口,利用该训练来识别读dqs的有效间隔并捕获数据,将有效的读取窗口与读取数据突发对齐,排除前置周期和任务物理线路延迟。

15、进一步的,所述读数据训练具体为:调整读dqs和读数据信号的对齐关系,给定已知的数据模式,ddr控制器调整内部dqs延迟,使dqs边缘出现在数据位图的中间。

16、进一步的,基于所述第二设计测试软件控制调整ddr3控制器,对ddr3存储器进行读数据眼图测试、写数据眼图测试时:

17、s201:读数据眼图测试中:

18、读数据眼图宽度基于向前和向后两个方向相对于读数据移动dqs位置测量,并找到内存测试成功的范围;dqs偏移以1/256时钟周期单位测量;

19、s201:写数据眼图测试中:

20、写入数据眼图宽度通过移动写入dqs位置相对于写入数据的位置,并找到内存测试成功的范围来测量;dqs偏移基于1/256时钟周期单位测量。

21、本发明具有的优点是:

22、以zynq和ddr存储器设计的硬件为平台,在arm端运行测试软件,基于ddr控制器配置微调dqs信号与clk、数据信号的位置关系,以软件方式测试模拟绘制眼图,以眼宽衡量其信号完整性。主要有以下特点:

23、(1)非接触式,无需示波器等高端仪器仪表设备辅助,仅以软件测试方式实现。

24、(2)最终的信号完整性评估以眼图的方式呈现,具有直观有效性。

25、(3)最终的评测指标为“眼宽”,信号完整性评价指标数据明确。

26、(4)基于arm+ddr的硬件设计架构,ddr存储器等大量使用,具有广泛的应用适用性。

技术特征:1.一种ddr存储器信号完整性非接触式测试评估方法,其特征在于,基于设置测试目标电路非接触式测试所述ddr存储器的信号完整性;所述测试目标电路至少包括:具有ddr3控制器的处理器芯片以及ddr3存储器;测试目标电路为sip微系统芯片或嵌入式电路;处理器芯片的zynq控制ddr3进行读写方存,ddr3的时钟频率范围为800mhz─1600mhz、容量1gb─8gb;

2.根据权利要求1所述的ddr存储器信号完整性非接触式测试评估方法,其特征在于,基于所述第一测试软件对所述ddr3存储器进行软件眼图测试前进行初始化和时序训练的方法包括以下步骤:

3.根据权利要求2所述的ddr存储器信号完整性非接触式测试评估方法,其特征在于,所述写训练具体为:调整dqs信号与时钟clk的相位关系,延迟dq信号以对齐和匹配电路板时延,ddr异步反馈clk,采样与dqs的上升沿,通过dq总线,控制器反复延迟dqs,直到检测到从0到1的过程。

4.根据权利要求3所述的ddr存储器信号完整性非接触式测试评估方法,其特征在于,所述读dqs训练具体为:调整有效的读操作dqs窗口,利用该训练来识别读dqs的有效间隔并捕获数据,将有效的读取窗口与读取数据突发对齐,排除前置周期和任务物理线路延迟。

5.根据权利要求4所述的ddr存储器信号完整性非接触式测试评估方法,其特征在于,所述读数据训练具体为:调整读dqs和读数据信号的对齐关系,给定已知的数据模式,ddr控制器调整内部dqs延迟,使dqs边缘出现在数据位图的中间。

6.根据权利要求5所述的ddr存储器信号完整性非接触式测试评估方法,其特征在于,基于第二设计测试软件控制调整ddr3控制器,对ddr3存储器进行读数据眼图测试、写数据眼图测试时:

技术总结本发明属于嵌入式计算技术领域,具体涉及一种DDR存储器信号完整性非接触式测试评估方法,基于设置测试目标电路非接触式测试DDR存储器的信号完整性;测试目标电路至少包括:具有DDR3控制器的处理器芯片以及DDR3存储器;测试目标电路为SIP微系统芯片或嵌入式电路;处理器芯片的Zynq控制DDR3进行读写方存,DDR3的时钟频率范围为800MHz─1600MHz、容量1Gb─8Gb;本发明能够解决基于Zynq+DDR设计平台的微系统芯片信号完整性评估难题,无需示波器等仪器,用软件模拟眼图的方式评估设计的信号完整性。技术研发人员:吕浩,赵谦,李晓蕊,刘小剑,楚要钦,李健一受保护的技术使用者:中国航空工业集团公司西安航空计算技术研究所技术研发日:技术公布日:2024/6/5本文地址:https://www.jishuxx.com/zhuanli/20240731/184967.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表