一种集成电路熔丝修调阵列测试装置及测试方法与流程

- 国知局

- 2024-08-19 14:23:07

本发明涉及集成电路测试,更具体地,涉及一种集成电路熔丝修调阵列测试装置及一种集成电路熔丝修调阵列测试方法。

背景技术:

1、当电源管理类集成电路芯片制造出来时,芯片设计公司给芯片测试公司提供芯片手册,针对芯片多类参数进行修调,修调的手段是通过烧断目标熔丝实现的。

2、根据设计公司的芯片手册,熔丝位较多(目前单芯片最多已达到30段),而且是以开发多site并行测试居多。熔丝位较多、多site同测等因素给pcb设计增加了难度,但熔丝修调部分的电路都是大同小异,目前一般采用的两种方式,用测试系统电源在熔丝pad上直接加一定电压来烧断熔丝,或者通过先对电容充电再利用电容放电的方式来达到烧断熔丝的效果。因此,通过归纳熔丝修调的原理与外围设计了熔丝修调阵列。

3、传统的熔丝修调技术,根据具体的芯片规范,设计专有的dut板、探针卡等硬件,熔丝修调模块设计在dut板上。该做法的弊端是,每款芯片都需要设计专有的dut板、探针卡等,导致pcb绘制繁琐,容易出错。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一,提供一种集成电路熔丝修调阵列测试装置及方法,以解决相关技术中存在的pcb绘制复杂、难度大、容易出错等问题。

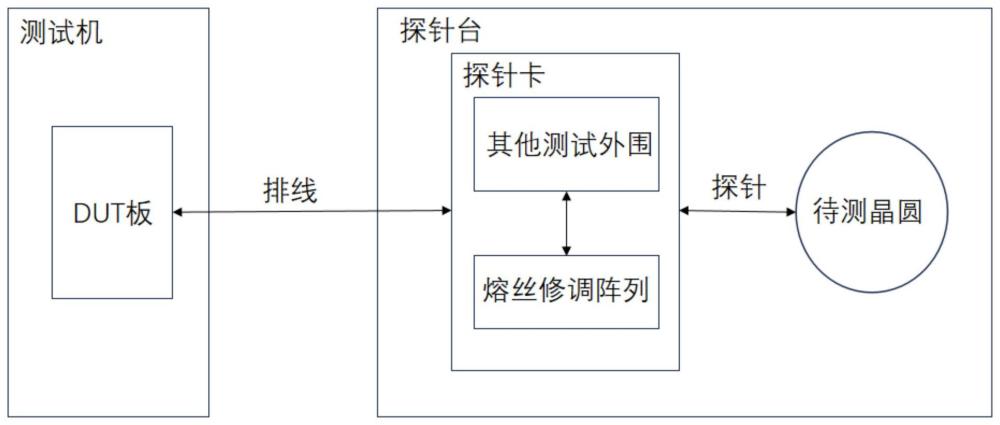

2、作为本发明的第一个方面,提供一种集成电路熔丝修调阵列测试装置,所述集成电路熔丝修调阵列测试装置包括测试机和探针台,所述测试机上设置有dut板,所述探针台上设置有探针卡和待测晶圆,所述dut板通过排线与所述探针卡连接,所述探针卡通过探针与所述待测晶圆连接,所述探针卡包括熔丝修调阵列;

3、其中,所述测试机根据所述待测晶圆的修调要求将对应的测试资源引出至所述dut板上,所述dut板将所述对应的测试资源引出至所述探针卡上,使得所述熔丝修调阵列能够根据所述对应的测试资源对所述待测晶圆内的多颗芯片同时进行修调测试。

4、进一步地,所述熔丝修调阵列包括继电器和多个第一开关ksite1-ksiten,每个所述第一开关通过多个第二开关k1-kn与所述待测晶圆内的一颗芯片连接,所述测试机控制所述继电器,使得所述继电器能够控制多个所述第一开关选择所述待测晶圆内的一颗芯片进行修调测试或者多颗芯片同时进行修调测试;

5、其中,每个所述第一开关分别连接多个第二开关k1-kn,每个所述第二开关分别连接一段熔丝,每个所述第一开关所连接的多段熔丝通过探针连接到一颗芯片的熔丝pad上,在所述熔丝修调阵列对所述待测晶圆内的每颗芯片进行修调测试时,所述继电器控制每个所述第一开关所连接的多个第二开关k1-kn,以选择烧断该第一开关所连接的一段熔丝或者多段熔丝,进而实现对该第一开关所连接芯片的修调测试。

6、进一步地,所述熔丝修调阵列通过电源烧断熔丝、电容烧断熔丝或mos管烧断熔丝的方式对所述待测晶圆内的芯片进行修调测试。

7、进一步地,所述dut板通过接插件插在所述测试机上,以引出所述测试机的测试资源,所述测试资源用于加压、加流和测试反馈;所述熔丝修调阵列通过接插件插在所述探针卡上;所述排线分别通过接插件连接所述dut板和所述探针卡,使得所述dut板上的测试资源与所述探针卡上的熔丝修调阵列连接。

8、进一步地,所述dut板和所述熔丝修调阵列是通用的,所述探针卡根据所述待测晶圆的芯片具体信息进行定制化设计。

9、进一步地,所述待测晶圆内的芯片类型为电源管理类模拟集成电路芯片,所述测试机根据芯片规范文件,通过烧断熔丝的方式对芯片的多种参数进行修调测试。

10、进一步地,所述探针卡还包括其他测试外围电路,所述其他测试外围电路用于对所述待测晶圆内芯片的其他参数进行测试。

11、作为本发明的另一个方面,提供一种集成电路熔丝修调阵列测试方法,通过前文所述的集成电路熔丝修调阵列测试装置实现测试,所述集成电路熔丝修调阵列测试方法包括:

12、通过测试机根据待测晶圆的修调要求将对应的测试资源引出至dut板上;

13、通过dut板将所述对应的测试资源引出至探针卡上;

14、在需要对所述待测晶圆进行测试时,直接调用所述熔丝修调阵列上的测试资源,烧断所述熔丝修调阵列上的目标段熔丝,以实现对所述待测晶圆内的多颗芯片同时进行修调测试。

15、本发明提供的集成电路熔丝修调阵列测试装置具有以下优点:通过测试机电源直接供烧熔丝的方式,将熔丝修调部分的电路固化,设计成通用的熔丝修调阵列,与此同时,设计芯片测试的通用dut板;并根据芯片规范手册设计专用探针卡,实现单芯片多段熔丝修调测试,测试site数达到多site同时修调测试。减小了pcb板的设计难度,提高了工作效率,降低了公司的运营成本。

技术特征:1.一种集成电路熔丝修调阵列测试装置,其特征在于,所述集成电路熔丝修调阵列测试装置包括测试机和探针台,所述测试机上设置有dut板,所述探针台上设置有探针卡和待测晶圆,所述dut板通过排线与所述探针卡连接,所述探针卡通过探针与所述待测晶圆连接,所述探针卡包括熔丝修调阵列;

2.根据权利要求1所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述熔丝修调阵列包括继电器和多个第一开关ksite1-ksiten,每个所述第一开关通过多个第二开关k1-kn与所述待测晶圆内的一颗芯片连接,所述测试机控制所述继电器,使得所述继电器能够控制多个所述第一开关选择所述待测晶圆内的一颗芯片进行修调测试或者多颗芯片同时进行修调测试;

3.根据权利要求2所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述熔丝修调阵列通过电源烧断熔丝、电容烧断熔丝或mos管烧断熔丝的方式对所述待测晶圆内的芯片进行修调测试。

4.根据权利要求1所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述dut板通过接插件插在所述测试机上,以引出所述测试机的测试资源,所述测试资源用于加压、加流和测试反馈;所述熔丝修调阵列通过接插件插在所述探针卡上;所述排线分别通过接插件连接所述dut板和所述探针卡,使得所述dut板上的测试资源与所述探针卡上的熔丝修调阵列连接。

5.根据权利要求1所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述dut板和所述熔丝修调阵列是通用的,所述探针卡根据所述待测晶圆的芯片具体信息进行定制化设计。

6.根据权利要求1所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述待测晶圆内的芯片类型为电源管理类模拟集成电路芯片,所述测试机根据芯片规范文件,通过烧断熔丝的方式对芯片的多种参数进行修调测试。

7.根据权利要求1所述的一种集成电路熔丝修调阵列测试装置,其特征在于,所述探针卡还包括其他测试外围电路,所述其他测试外围电路用于对所述待测晶圆内芯片的其他参数进行测试。

8.一种集成电路熔丝修调阵列测试方法,通过权利要求1至7中任意一项所述的集成电路熔丝修调阵列测试装置实现测试,其特征在于,所述集成电路熔丝修调阵列测试方法包括:

技术总结本发明涉及集成电路测试技术领域,具体公开了一种集成电路熔丝修调阵列测试装置及测试方法,该测试装置包括测试机和探针台,测试机上设置有DUT板,探针台上设置有探针卡和待测晶圆,DUT板通过排线与探针卡连接,探针卡通过探针与待测晶圆连接,探针卡包括熔丝修调阵列;其中,测试机根据待测晶圆的修调要求将对应的测试资源引出至DUT板上,DUT板将对应的测试资源引出至探针卡上,使得熔丝修调阵列能够根据对应的测试资源对待测晶圆内的多颗芯片同时进行修调测试。本发明提供的集成电路熔丝修调阵列测试装置,能够减小PCB板的设计难度,提高了工作效率,降低了公司的运营成本。技术研发人员:唐彩彬,孙恺凡,张凯虹受保护的技术使用者:无锡中微腾芯电子有限公司技术研发日:技术公布日:2024/8/16本文地址:https://www.jishuxx.com/zhuanli/20240819/274999.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。