一种氮化镓闪存制备方法和读写方法与流程

- 国知局

- 2024-08-30 14:32:04

本发明属于半导体领域,尤其涉及一种氮化镓闪存制备方法和读写方法。

背景技术:

1、半导体器件材料已经由最初的ge、si基材料扩展至化合物宽禁带半导体,例如常见的氮化镓(gan)、碳化硅(sic)等,因其优越的材料性能,已成为功率应用领域的新兴材料。在电力电子、射频、光电子等泛模拟应用方面因其高频、高压、高温等优异特性,已经逐渐渗透到适配器、工业电源、车载电源等领域。在器件功能方面,目前氮化镓基发光二极管、氮化镓基高电子迁移率晶体管等,这些器件在工作原理和器件性能方面均有类似的传统半导体器件相对应,如目前广泛应用于微波射频、电力电子行业的高电子迁移率晶体管hemt器件就具有类似于硅基金属氧化物半导体场效应晶体管mosfet的工作方式和性能;hemt器件中,在漏极、漏极之间形成导电沟道,在导电沟道中间的某个位置设置栅极,通过改变栅极电压来影响导电沟道的开通与关断等状态,实现可控的电路通断,这一原理以各种形式广泛存在与各类模拟、数字、混合集成电路中,尤其是诸如互补型金属氧化物半导体器件中,而氮化镓基器件与传统器件仍存在一些机理和器件结构方面的差异,这些差异决定着两者在使用中需要关注不同的要点。

2、其中,如在硅基mosfet和氮化镓基hemt方面,两者的沟道形成和控制机理存在着相当的差异,以n型导电增强型器件为例:mosfet采用在低掺杂p型衬底之上通过掺杂高n型漏极、漏极作为电极,栅极位于漏极、漏极之间,同时制备衬底电极,栅极正压时建立导电沟道;hemt则采用在algan/gan界面形成的二维电子气(2deg)作为导电沟道。二维电子气具有高载流子浓度,高载流子迁移率等特性,加之氮化镓本身具有宽禁带材料的特性,使得氮化镓基hemt器件在处理高速信号以及应对高温、高辐射工作环境方面具备更好的性能和鲁棒性。

3、然而,硅基半导体经过多年发展其成熟度提高的同时也逐渐逼近材料极限,所制备的器件通常所需的工作温度要低于175℃,在宇宙空间、特殊工厂等高辐射环境下寿命与鲁棒性将显著下降。存储器根据所需场景通常和不同的器件结构集成,随着外围cmos器件的微缩,器件形成后的工艺步骤也全部需要低温工艺流程,制程兼容性方面对于通常在cmos器件形成后构建的dram单元工艺来说是一个巨大的挑战。此外,用于硅基传统制程的介电层材料sio2介电常数为3.9,远低于氮化镓的介电常数8.9,其电气性能也处于劣势。且传统mom、mim电容大小不可控,缺乏灵活性。

4、闪存即快闪存储器,是一种电子式可清除程序化只读存储器的形式,允许在操作中被多次擦或写的存储器。这种科技主要用于一般性数据存储,以及在计算机与其他数字产品间交换传输数据,如储存卡与u盘。闪存是一种特殊的、以宏块抹写的eprom。

5、经过多年的发展,已形成成熟的dram、sram、flash等多种形态的产品。其中nand-flash存储具有容量较大,改写速度快等优点,适用于大量数据的存储,因而在业界得到了越来越广泛的应用。作为非易失性存储器,flash存储器在栅区对比传统cmos工艺器件会增加一个浮栅结构,用来存储电荷进而体现“0”或“1”的存储。然而,氮化镓等新型半导体材料虽然具备较好的载流子输运特性,目前尚无成熟的氮化镓材料的闪存方案。

6、基于以上,本技术提供了解决以上技术问题的技术方案。

技术实现思路

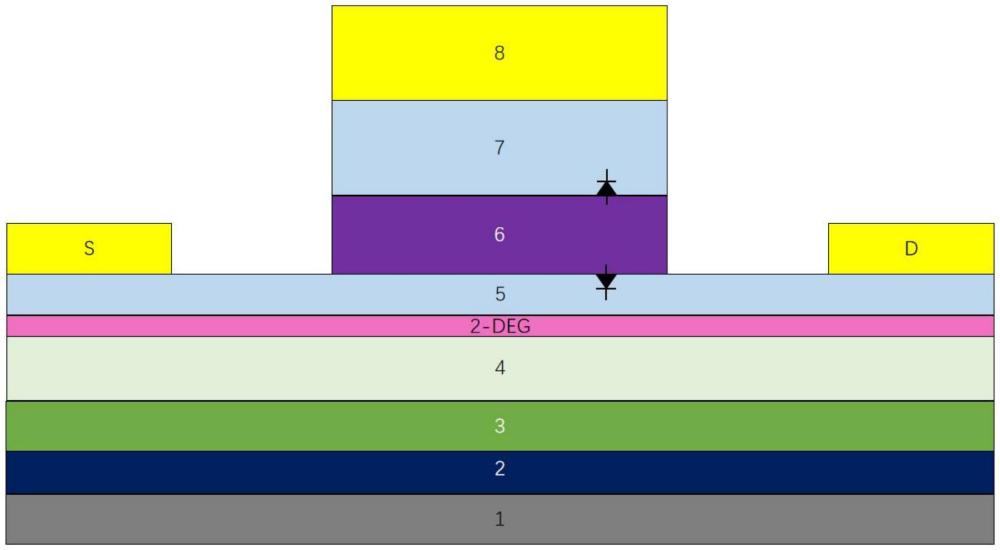

1、针对现有技术中氮化镓半导体材料闪存还存在技术空白的场景,本发明提供了一种氮化镓闪存制备方法,用于制作一种氮化镓闪存,所述制备方法包括以下步骤:

2、步骤s1、形成一衬底,在所述衬底上依次形成缓冲层、沟道层和势垒层;

3、步骤s2、在所述势垒层上侧形成一npn浮栅结构;

4、步骤s3、在所述npn浮栅结构上侧形成电极结构;

5、其中,所述npn浮栅结构由上至下包括控制栅电极、第一氮化镓层、浮栅层、势垒层。

6、在本发明的一个具体实施方式中,所述缓冲层和所述势垒层之间还包括第二氮化镓层,所述第一氮化镓层与第二氮化镓层材质相同,采用本征氮化镓材料或本征氮化铝镓。

7、在本发明的一个具体实施方式中,所述浮栅层为掺杂了掺杂离子的gan或algan结构,并与第一氮化镓层、所述势垒层共同形成背靠背二极管结构。

8、在本发明的一个具体实施方式中,所述掺杂离子为镁离子,并通过退火工艺激活所述镁离子,形成npn浮栅结构。

9、在本发明的一个具体实施方式中,当负电荷数量大于第二阈值δx后,所述npn浮栅结构通过电势变化控制所述沟道层的导通特性:当所述npn浮栅结构中不存在电荷,在所述控制栅电极上施加第一阈值的正电压,所述沟道层开启至第一状态;当所述npn浮栅结构中累计负电荷大于第二阈值,在所述控制栅电极上施加第三阈值的正电压使所述沟道层开启至第一状态,其中,x1<x3,x1表示第一阈值,x3表示第三阈值,第三阈值与第一阈值的差值取决于所述npn浮栅结构中累计的负电荷量,x1+δx=x3。

10、在本发明的一个具体实施方式中,所述电极结构包括漏极和源极,所述控制栅电极通过刻蚀或沉积工艺制备,源极、漏极通过沉积工艺制备为接触电极。

11、在本发明的一个具体实施方式中,所述缓冲层中还包括应力缓冲结构,所述应力缓冲结构包括交替变化或梯度变化的al组分。

12、本发明还提供一种氮化镓闪存读写方法,用于读写根据任一项前述的氮化镓闪存制备方法制成的氮化镓闪存,向所述氮化镓闪存写入数据包括:向所述控制栅电极施加高于氮化镓闪存的阈值的电压使沟道层开启,向所述电极结构施加电压,使沟道层载流子处于热载流子状态,隧穿过势垒层进入所述npn浮栅结构,并被所述npn浮栅结构捕获。

13、在本发明的一个具体实施方式中,从所述氮化镓闪存中读取数据包括:向所述控制栅施加等于氮化镓闪存的阈值的电压使得沟道层开启,在所述电极结构施加低电压并测量沟道层电流,如果电流达到第四阈值则所述npn浮栅结构上没有负电荷,所述氮化镓闪存开启正常,实现第一读取操作;若电流未达到第四阈值则所述npn浮栅结构上存在负电荷,使所述氮化镓闪存开启所需的阈值变高,实现第二读取操作;通过第一读取操作与第二读取操作而得的字符存储在所述氮化镓闪存中。

14、在本发明的一个具体实施方式中,使所述氮化镓闪存擦除数据包括:向所述控制栅电极通入第一负偏压,向电极结构通入第二负偏压,使所述npn浮栅结构上的负电载流子隧穿至源极,所述npn浮栅结构恢复到未充电状态,擦除所述氮化镓闪存中的数据。

15、本发明能够带来以下至少一种有益效果:本发明提出了一种氮化镓闪存的制备方法和读写方法,依次形成衬底、缓冲层和由第一氮化镓层、浮栅层和第二氮化镓层组成的npn浮栅结构,再在所述势垒层上侧形成电极结构,上述制备方案与现有成熟的cmos制造工艺或氮化镓基半导体器件制造工艺相互兼容,制备出的氮化镓闪存具备高载流子浓度、高载流子迁移率、耐高温、抗辐射等优异特性,相较于现有的硅基半导体闪存提升了极端环境如高温、高辐射场景下的鲁棒性;此外,浮栅层在衬底外延出外延层时一并形成,无需额外的光刻工艺,显著提升了工艺效率、降低了制备的成本。

本文地址:https://www.jishuxx.com/zhuanli/20240830/282537.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表