基于ScAlN_GaN的P沟道异质结场效应晶体管及其制备方法

- 国知局

- 2024-09-05 14:55:45

本发明属于半导体器件,更具体地说,涉及一种基于scaln_gan的p沟道异质结场效应晶体管及其制备方法。

背景技术:

1、新一代半导体材料氮化镓(gan)具有宽禁带(3.4ev)、高击穿电压(3.1mv/cm)、高电子迁移率(~1500cm2/v·s)等优良特性,scaln是一种超宽带隙的过渡金属氮化物,具有相当增强的极化特性,由于极化效应,gan/scaln/gan结构在无需故意掺杂的情况下便可以同时形成高浓度的二维电子气(2deg)和二维空穴气(2dhg)。利用2deg和2dhg可以分别构成n沟道异质结场效应晶体管(hfet)和p沟道hfet。

2、近年来,人们对互补异质结构fet(hfet)技术的兴趣日益增长,n沟道hfet已经受到广泛研究,并且继续表现出突出的性能,同时在不断改进。但是分立的n沟道hfet器件不能与硅基电路很好的融合,如果将n沟道hfet与p沟道hfet相结合,可以构建高密度低功耗互补逻辑电路、驱动电路、控制电路等等,这样就可以更好地发挥它的潜力。但是,由于gan材料的空穴迁移率很低(室温下仅有5-52cm2/v·s),p沟道hfet的性能与n沟道hfet相比差距巨大,同时也已经证明p沟道hfet的应用要困难得多,但在一些新的应用中它仍具有很大的前景,如宽带放大器的有源负载、数字到模拟转换器等。

3、如何提升gan基p沟道hfet的性能,一直是本领域技术人员亟待解决的问题之一。

4、因此,亟需一种新的基于scaln_gan的p沟道异质结场效应晶体管及其制备方法。

技术实现思路

1、本发明提出了一种基于scaln_gan的p沟道异质结场效应晶体管及其制备方法。scaln可以与gan晶格匹配,避免了aln/gan中固有的临界厚度限制。同时,本发明使用的是sc0.18al0.82n,与gan没有晶格失配,提高了空穴迁移率,从而增大了开态电流。

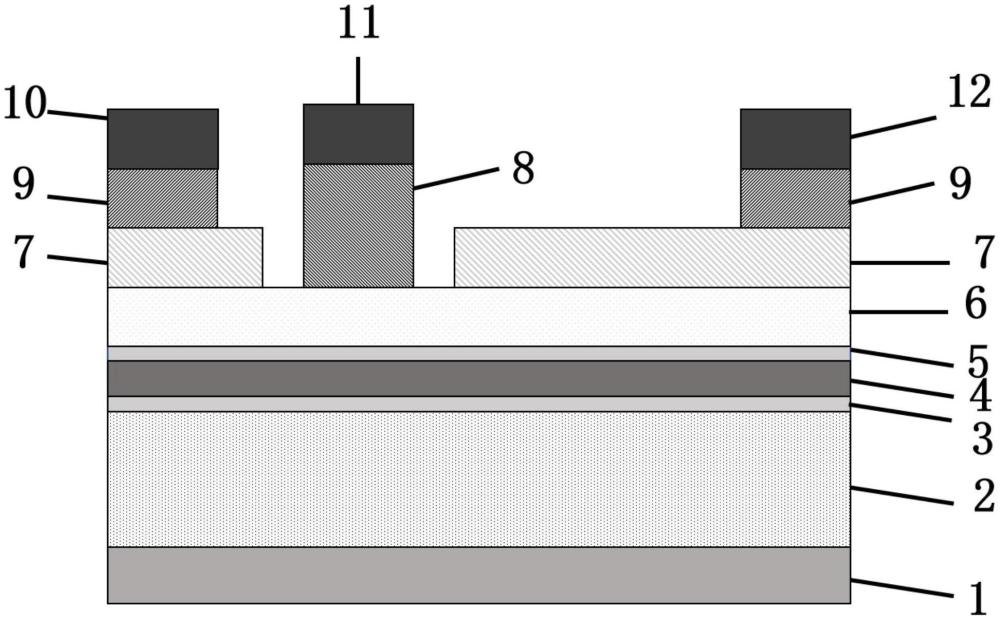

2、为了解决上述技术问题至少之一,根据本发明的一方面,提供了一种基于scaln_1.一种基于scaln_gan的p沟道异质结场效应晶体管,包括依次设置的衬底、gan缓冲层、aln插入层、scaln势垒层、gan通道层、p型轻掺杂gan盖帽层、n型重掺杂gan层和p型重掺杂gan盖帽层,所述n型重掺杂gan层位于p型轻掺杂gan盖帽层的一个凹栅中;所述p型重掺杂gan盖帽层上形成栅极,所述p型轻掺杂gan盖帽层一端形成源极,所述p型轻掺杂gan盖帽层另一端形成漏极。

3、进一步的,所述gan缓冲层的厚度为1-3μm,所述aln插入层1-3nm,所述scaln势垒层的厚度为10-30nm,所述gan通道层的厚度为20-50nm,所述p型轻掺杂gan盖帽层的厚度为20-40nm,所述n型重掺杂gan层的厚度为30-50nm、p型重掺杂gan盖帽层的厚度为20-30nm。

4、进一步的,所述scaln势垒层采用sc0.18al0.82n。

5、进一步的,所述凹栅宽度为3-5μm。

6、进一步的,所述衬底为硅片、蓝宝石和氮化镓中的一种或几种。

7、根据本发明的一方面,提供了一种基于scaln_gan的p沟道异质结场效应晶体管制备方法,包括如下步骤:

8、在衬底层上生长gan缓冲层;

9、在所述gan缓冲层上生长aln插入层;

10、在所述aln插入层上生长scaln势垒层;

11、在所述scaln势垒层上生长aln插入层;

12、在所述aln插入层上生长gan通道层;

13、在所述gan通道层上生长p型轻掺杂gan盖帽层;

14、在所述p型轻掺杂gan盖帽层进行选择性蚀刻,蚀刻出宽度约3-5μm的凹栅;

15、在所述凹栅中心生长宽度1-3μm的n型重掺杂gan层;

16、在所述n型重掺杂gan层上生长栅极;

17、在所述p型轻掺杂gan盖帽层上生长p型重掺杂gan盖帽层;

18、在所述外延结构上形成间距10-20μm的源极和漏极;

19、在所述外延结构上进行选择性蚀刻,将源极与漏极间的p型重掺杂gan盖帽层全部刻蚀掉。

20、根据本发明的另一方面,提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现本发明的基于scaln_gan的p沟道异质结场效应晶体管制备方法中的步骤。

21、根据本发明的又一方面,提供了一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现本发明的基于scaln_gan的p沟道异质结场效应晶体管制备方法中的步骤。

22、与现有的技术相比较,本发明的上述方法的有益效果为:本发明使用的是sc0.18al0.82n,与gan没有晶格失配,这样提高了空穴迁移率,从而增大了开态电流。

技术特征:1.一种基于scaln_gan的p沟道异质结场效应晶体管,其特征在于,包括依次设置的衬底、gan缓冲层、aln插入层、scaln势垒层、gan通道层、p型轻掺杂gan盖帽层、n型重掺杂gan层和p型重掺杂gan盖帽层,所述n型重掺杂gan层位于p型轻掺杂gan盖帽层的一个凹栅中;所述p型重掺杂gan盖帽层上形成栅极,所述p型轻掺杂gan盖帽层一端形成源极,所述p型轻掺杂gan盖帽层另一端形成漏极。

2.根据权利要求1所述的基于scaln_gan的p沟道异质结场效应晶体管,其特征在于,所述gan缓冲层的厚度为1-3μm,所述aln插入层1-3nm,所述scaln势垒层的厚度为10-30nm,所述gan通道层的厚度为20-50nm,所述p型轻掺杂gan盖帽层的厚度为20-40nm,所述n型重掺杂gan层的厚度为30-50nm、p型重掺杂gan盖帽层的厚度为20-30nm。

3.根据权利要求1所述的基于scaln_gan的p沟道异质结场效应晶体管,其特征在于:所述scaln势垒层采用sc0.18al0.82n。

4.根据权利要求1所述的基于scaln_gan的p沟道异质结场效应晶体管,其特征在于,所述凹栅宽度为3-5μm。

5.根据权利要求1所述的基于scaln_gan的p沟道异质结场效应晶体管,其特征在于,所述衬底为硅片、蓝宝石和氮化镓中的一种或几种。

6.一种基于scaln_gan的p沟道异质结场效应晶体管制备方法,其特征在于,包括如下步骤:

7.一种计算机可读存储介质,其上存储有计算机程序,其特征在于:该程序被处理器执行时实现如权利要求6中所述的基于scaln_gan的p沟道异质结场效应晶体管制备方法中的步骤。

8.一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求6中所述的基于scaln_gan的p沟道异质结场效应晶体管制备方法中的步骤。

技术总结本发明公开了一种基于ScAlN_GaN的P沟道异质结场效应晶体管及其制备方法。所述场效应晶体管,包括依次设置的衬底、GaN缓冲层、AlN插入层、ScAlN势垒层、GaN通道层、P型轻掺杂GaN盖帽层、N型重掺杂GaN层和P型重掺杂GaN盖帽层,所述N型重掺杂GaN层位于P型轻掺杂GaN盖帽层的一个凹栅中;所述P型重掺杂GaN盖帽层上形成栅极,所述P型轻掺杂GaN盖帽层一端形成源极,所述P型轻掺杂GaN盖帽层另一端形成漏极。本发明使用的是Sc0.18Al0.82N,与GaN没有晶格失配,提高了空穴迁移率,从而增大了开态电流。技术研发人员:汪金,黄淞,宋欢,刘思楚,薛俊俊,智婷受保护的技术使用者:南京邮电大学技术研发日:技术公布日:2024/9/2本文地址:https://www.jishuxx.com/zhuanli/20240905/288886.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。