基于简易混沌系统的可重构逻辑计算电路

- 国知局

- 2024-09-11 14:15:50

本发明涉及,特别是涉及一种基于简易混沌系统的可重构逻辑计算电路。

背景技术:

1、动态可重构作为解决目前主流计算机芯片因单一固定配置而导致其缺乏可控性、灵活性以及可变性的方案,动态可重构提供了一种电路执行各种类别数字计算的方式。目前已知的可重构芯片fpga需要通过重新布线来实现不同数字功能,但是布线花费的时间限制了fpga芯片的应用场景。

2、此外,研究人员利用电路的非线性动力学和内在复杂性来增强可重构性和计算的灵活性,理论和模拟研究以及离散电路实验均已证明,非线性动力学能够实现可重构计算。混沌计算就是使用固定电路,利用电路内部的动力学特性,在只改变系统参数情况下,使逻辑元件实时地在不同的逻辑门间进行转换,实现不同的逻辑计算功能。混沌是非线性确定性系统中的一种独特行为,表现为非周期性和不可预测性,混沌系统对初始状态的微小变化极为敏感。由于具有确定的非周期性和初始敏感性,其成为各类安全应用最佳候选者,包括伪随机数生成器prng,可重构,侧信道攻击缓解,以及具有物理不可克隆性的逻辑混淆等。

3、然而,随着机器学习的不断进步,由混沌构成的安全系统更容易受到潜在对手的攻击。例如,kia等人介绍了一个由晶体管构成的可重构系统,其实现了可重构逻辑计算的功能;shanta等人设计的由混沌系统为核心的具有物理不可克隆性的逻辑混淆系统;majumder等人设计的以混沌系统为核心的具有缓解侧信道攻击的电路系统。这些系统的核心都是混沌系统,但它们都存在一个明显的缺点,即混沌区域狭窄且不连续,狭窄的混沌区域影响系统的应用范围和场景。为了解决这一问题,研究者寻找宽混沌范围的混沌系统,因为宽混沌范围的混沌系统具有更宽的混沌空间,这可以一定程度上避免外部参数变化或参数值波动导致的混沌特性降低的现象,以及系统从混沌状态滑落到不期望的周期性(非混沌)状态,更宽的混沌空间也可以提高各类安全应用的安全性能。根据所涉及的状态变量的数量,混沌系统分为低维混沌系统和高维混沌系统。其中高维混沌系统有更加复杂的混沌特性和更加安全的混沌系列,但往往具有极高的计算成本;而低维混沌系统实现方式简单,生成混沌时间序列短,但是混沌范围狭窄,容易受到外界干扰而降低混沌特性。

4、现有技术缺点:高维混沌系统有更加复杂的混沌特性和更加安全的混沌系列,但往往具有极高的计算成本;而低维混沌系统实现方式简单,生成混沌时间序列短,但是混沌范围狭窄,容易受到外界干扰而降低混沌特性。

技术实现思路

1、本发明提供的一种基于简易混沌系统的可重构逻辑计算电路,结构简单,混沌性能更优异。

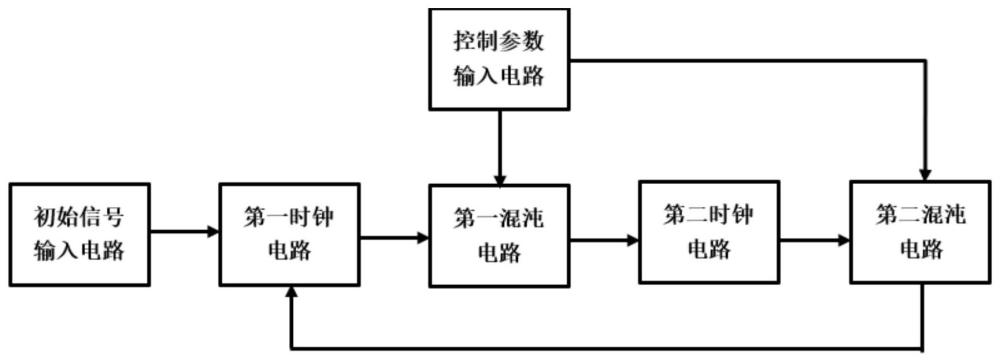

2、为达到上述目的,本发明提供的一种基于简易混沌系统的可重构逻辑计算电路,其关键是:设置有初始信号输入电路、控制参数输入电路、第一混沌电路和第二混沌电路;

3、所述初始信号输入电路生成初始信号,并将所述初始信号发送给第一混沌电路;所述控制参数输入电路生成分岔控制参数vc,并将所述分岔控制参数vc发送给第一混沌电路和第二混沌电路;所述第一混沌电路接收所述初始信号和分岔控制参数vc,并输出第一混沌信号给第二混沌电路;所述第二混沌电路接收所述第一混沌信号和分岔控制参数vc,并输出第二混沌信号给第一混沌电路。

4、通过上述设计,所述初始信号输入电路用于生成初始信号,同时生成初始控制参数实现对初始信号的调整控制;所述控制参数输入电路生成分岔控制参数vc,并将其输入到中,保证第一混沌电路和第二混沌电路的输入与输出之间具有丰富的混沌动力学行为;所述第一混沌电路用于通过分岔控制参数vc将初始信号或第二混沌信号进行一维混沌映射,生成第一混沌信号;所述第二混沌电路用于通过分岔控制参数vc将第一混沌信号进行一维混沌映射,生成第二混沌信号。所述第一混沌电路和第二混沌电路形成循环输出的非线性混沌电路。

5、所述第一混沌电路和第二混沌电路的一维混沌映射公式如下:

6、

7、其中,xn+1表示第一混沌电路或第二混沌电路的输出信号,c表示第一输入电压,c取值为0v或1v;vc表示控制参数,xn表示第一混沌电路或第二混沌电路的输入信号,vbais表示第二输入电压。

8、作为优选:所述第一混沌电路设置有第一乘法器a1、第二乘法器a2、第三乘法器a3、第一运算放大器u1、第二运算放大器u2、第三运算放大器u3、电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r9、电阻r10、电阻r11、电阻r12、电阻r13和电阻r14;

9、所述第一乘法器a1的两个输入端与所述初始信号输入电路和第二混沌电路的输出端相通,所述第一乘法器a1的输出端接第二乘法器a2的第一输入端;

10、所述第二运算放大器u2的正向输入端经电阻r9后与所述初始信号输入电路和第二混沌电路的输出端相通,第二运算放大器u2的正向输入端还经电阻r10与所述控制参数输入电路的输出端连接,所述第二运算放大器u2的负向输入端串电阻r8后接地,所述第二运算放大器u2的输出端接第三乘法器a3的第一输入端,该第二运算放大器u2的输出端还串电阻r7后接负向输入端;

11、所述第三乘法器a3的第二输入端接第一输入电压c,第三乘法器a3的输出端串电阻r14后接第三运算放大器u3的正向输入端;所述第三运算放大器u3的正向输入端还串电阻r13后接第二输入电压vbais,所述第三运算放大器u3的负向输入端串电阻r12后接地,所述第三运算放大器u3的输出端接所述第二乘法器a2的第二输入端,该第三运算放大器u3的输出端还串电阻r11后接负向输入端,该第三运算放大器u3的输出端还串电阻r4后接第一运算放大器u1的正向输入端;

12、所述第二乘法器a2的输出端串电阻r3后接第一运算放大器u1的负向输入端,所述第一运算放大器u1的正向输入端串电阻r6后接地,第一运算放大器u1的输出端串电阻r5后接负向输入端,第一运算放大器u1的输出端与所述第二混沌电路的输入端相通。

13、作为优选:所述第二混沌电路设置有第四乘法器a4、第五乘法器a5、第六乘法器a6、第五运算放大器u5、第六运算放大器u6、第七运算放大器u7、电阻r2、电阻r15、电阻r16、电阻r17、电阻r18、电阻r19、电阻r20、电阻r21、电阻r22、电阻r23、电阻r24和电阻r25;

14、所述第四乘法器a4的两个输入端接第一混沌电路的输出端,第四乘法器a4的输出端接第五乘法器a5的第一输入端;

15、所述第六运算放大器u6的正向输入端经电阻r20接第一混沌电路的输出端,所述第六运算放大器u6的正向输入端还经电阻r21与所述控制参数输入电路的输出端连接,所述第六运算放大器u6的负向输入端串电阻r19后接地,所述第六运算放大器u6的输出端接第六乘法器a6的第一输入端,该第六运算放大器u6的输出端还串电阻r18后接负向输入端;

16、所述第六乘法器a6的第二输入端接第一输入电压c,第六乘法器a6的输出端串电阻r25后接第七运算放大器u7的正向输入端;所述第七运算放大器u7的正向输入端还串电阻r24后接第二输入电压vbais,该第七运算放大器u7的负向输入端串电阻r23后接地,所述第七运算放大器u7的输出端接所述第五乘法器a5的第二输入端,第七运算放大器u7的输出端还串电阻r22后接负向输入端,第七运算放大器u7的输出端还串电阻r15后接第五运算放大器u5的正向输入端;

17、所述第五乘法器a5的输出端串电阻r2后接第五运算放大器u5的负向输入端,所述第五运算放大器u5的正向输入端串电阻r17后接地,该第五运算放大器u5的输出端串电阻r16后接负向输入端,该第五运算放大器u5的输出端还与所述第一混沌电路的输入端相通。

18、作为优选:所述初始信号输入电路设置有第四运算放大器u4、电阻r32、电阻r33、电阻r34、电阻r35、电阻r45、滑变电阻r36、滑变电阻r37、滑变电阻r38、滑变电阻r44、双向开关s4、双向开关s5、双向开关s6、双向开关s9和电源v2;

19、所述第四运算放大器u4的正向输入端依次经双向开关s5和滑变电阻r36后接电源v2的负极,电源v2的正极接地,该正向输入端还依次经双向开关s4、滑变电阻r37和电阻r32后接电源v2的负极,该正向输入端还依次经双向开关s6、滑变电阻r38、电阻r35和电阻r32后接电源v2的负极,该正向输入端还依次经双向开关s9、滑变电阻r44、电阻r45、电阻r35和电阻r32后接电源v2的负极,该正向输入端还依次经电阻r33、电阻r45、电阻r35和电阻r32后接电源v2的负极;

20、所述第四运算放大器u4的负向输入端依次经双向开关s5和滑变电阻r36后接电源v2的负极,该负向输入端还依次经双向开关s4、滑变电阻r37和电阻r32后接电源v2的负极,该负向输入端还依次经双向开关s6、滑变电阻r38、电阻r35和电阻r32后接电源v2的负极,该负向输入端还依次经双向开关s9、滑变电阻r44、电阻r45、电阻r35和电阻r32后接电源v2的负极;

21、所述第四运算放大器u4的输出端串电阻r34后接负向输入端,该输出端还与第一混沌电路的输入端相通。

22、作为优选:所述控制参数输入电路设置有第八运算放大器u8、电阻r1、电阻r39、电阻r40、电阻r43、滑变电阻r41、滑变电阻r42、双向开关s7、双向开关s8和电源v3;

23、所述第八运算放大器u8的正向输入端依次经双向开关s8和滑变电阻r41后接电源v3的负极,电源v3的正极接地,该正向输入端还依次经双向开关s7、滑变电阻r42和电阻r1后接电源v3的负极,该正向输入端还依次经电阻r43和电阻r1后接电源v3的负极;

24、所述第八运算放大器u8的负向输入端依次经双向开关s8和滑变电阻r41后接电源v3的负极,该负向输入端还依次经双向开关s7、滑变电阻r42和电阻r1后接电源v3的负极,该负向输入端还依次经电阻r39和电阻r1后接电源v3的负极;

25、所述第八运算放大器u8的输出端串电阻r40后接负向输入端,该输出端还分别与第一混沌电路和第二混沌电路连接。

26、作为优选:还设置有第一时钟电路和第二时钟电路,所述第一时钟电路的第一输入端接所述初始信号输入电路,第一时钟电路的第二输入端接所述第二混沌电路的输出端,第一时钟电路的输出端接第一混沌电路的输入端;所述第二时钟电路的输入端接第一混沌电路的输出端,第二时钟电路的输出端接第二混沌电路的输入端。

27、所述第一时钟电路用于对第一混沌电路的输入信号即初始信号或第二混沌信号进行初始化,并控制第一混沌电路的输入信号的导通与关闭;所述第二时钟电路用于对第二混沌电路的输入信号即第一混沌信号进行初始化,并控制第二混沌电路的输入的导通与关闭。

28、所述第一混沌电路和第二混沌电路结构一致,均为非线性电路,通过两个交替闭合的开关即第一时钟电路和第二时钟电路将两个相同的非线型电路连接,两个相同的非线性电路避免了交替闭合的开关而产生的竞争状态。同时,两个非线性电路共同作用可以使电路的迭代速度倍增。

29、非线性系统需要将初始状态转化为未来状态,故需要使用时钟电路对混沌电路的输入信号进行初始化。

30、作为优选:所述第一时钟电路设置有第九运算放大器u9、第十运算放大器u10、第十一运算放大器u11、第二时钟开关s2、第三时钟开关s3和电容c1;

31、所述第九运算放大器u9的正向输入端接所述初始信号输入电路,所述第九运算放大器u9的输出端接负向输入端,所述第九运算放大器u9的输出端还与第三时钟开关s3的一端连接,所述第三时钟开关s3的另一端接第十运算放大器u10的正向输入端,所述第十运算放大器u10的输出端接所述第一混沌电路,所述第十运算放大器u10的输出端还接负向输入端;

32、所述第十一运算放大器u11的正向输入端接所述第二混沌电路,所述第九运算放大器u9的输出端接负向输入端,所述第九运算放大器u9的输出端还与第二时钟开关s2的一端连接,所述第二时钟开关s2的另一端接第十运算放大器u10的正向输入端,所述第二时钟开关s2的另一端还串电容c1后接地。

33、当第一混沌电路的输入信号为初始信号时,第三时钟开关s3导通,第二时钟开关s2关闭;当第一混沌电路的输入信号为第二混沌信号时第二时钟开关s2导通,第三时钟开关s3关闭。

34、作为优选:所述第二时钟电路设置有第十二运算放大器u12、第十三运算放大器u13、第一时钟开关s1、电容c2;

35、所述第十二运算放大器u12的正向输入端接所述第一混沌电路,所述第十二运算放大器u12的输出端接负向输入端,所述第十二运算放大器u12的输出端还与第二时钟开关s2的一端连接,所述第二时钟开关s2的另一端接第十三运算放大器u13的正向输入端,所述第二时钟开关s2的另一端还串电容c2后接地,所述第十三运算放大器u13的输出端接所述第二混沌电路,所述第十三运算放大器u13的输出端还接负向输入端。

36、作为优选:还设置有第一示波器、第二示波器、第一辅助电路和第二辅助电路;所述第一混沌电路的输出端接第一示波器的第一输入端,该第一混沌电路的输出端还经第一辅助电路接第二示波器的第一输入端;所述第二混沌电路的输出端接第一示波器的第二输入端,该第二混沌电路的输出端还经第二辅助电路接第二示波器的第二输入端。

37、所述第一示波器用于显示记录第一混沌信号和第二混沌信号的模拟信号波形,所述第一示波器用于显示记录第一混沌信号和第二混沌信号的数字信号波形,以便观察输出信号的序列特征,评估混沌电路的混沌特性。

38、所述第一辅助电路和第二辅助电路用于分别对第一混沌信号和第二混沌信号进行模数转换。

39、作为优选:所述第一辅助电路和第二辅助电路结构一致,均设置有第十四运算放大器u14、电阻r26、电阻r27、二极管d1、二极管d2、电源v5、电源v6和电源v7;

40、所述第十四运算放大器u14的正向输入端经电阻r26接第一混沌电路或第二混沌电路,第十四运算放大器u14的负向输入端接电源v5的正极,电源v5的负极接地,第十四运算放大器u14的输出端接电阻r27的一端,电阻r27的另一端接所述第二示波器;

41、所述电阻r27的另一端还接二极管d1的正极,二极管d1的负极接电源v6的正极,电源v6的负极接地;所述电阻r27的另一端还接二极管d2的负极,二极管d2的正极接电源v7的正极,电源v7的负极接地。

42、本发明的有益效果是:具有更连续、更宽的混沌区域,在面对复杂的外部环境时,具有更好的稳定性、可拓展性和安全性;同时将控制和编程机制融入到基于简易混沌系统的可重构逻辑计算电路中,使电路具备一个纯数字的编程界面,通过向编码器电路添加额外的输入线,可以扩展该电路的数据输入功能;通过将混沌系统的其他参数进行改进扩展,可以实现更多控制输入的方式;电路输出端所采用的阈值技术可以根据不同的控制需求产生不同的控制信号,极大节约了控制成本。

本文地址:https://www.jishuxx.com/zhuanli/20240911/289874.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表