一种高低边集成功率开关的制作方法

- 国知局

- 2024-09-11 14:22:51

本发明属于功率半导体器件,特别涉及一种高低边集成功率开关。

背景技术:

1、传统的基于mos器件的电子电力电路,比如buck、boost及半桥等电路,它们均具备功率转换功能,使用集成电路完成功率转换功能通常需要控制电路、与输入电压电耦合的直流高侧器件、以及与地电耦合的直流低侧器件。例如在同步降压转换器(sync buckconverter)中,通过使高侧器件和低侧器件交替工作来进行功率转换从而降低电压,其中,由控制电路进行效率高且功耗低的开关和控制功能,因此高低侧器件可以被当作是一个功率开关。

2、控制电路通常包括逻辑电路、保护电路和驱动电路,那么控制电路和高低侧器件可以合称为智能功率开关。作为智能功率开关的输出级部分,即高低侧器件,往往需要用到两个串联配置的mos器件,其中一个mos的源极与另一个mos的漏极相连,如图1至图3中的虚线框所示。传统的解决方案是使用两个分立的mos器件和一个驱动芯片在pcb板上连接,然而,此种方案占用pcb板面积较大,布线长度较长,寄生电感、电容、电阻较大,从而影响信号传输延迟和增加电磁干扰,同时还存在多个封装焊接点可能带来的可靠性问题等。

3、为了解决传统方案的弊端,可以将两个串联的金属氧化物半导体场效应晶体管(metal-oxide-semiconductorfield-effect transistor,mosfet)芯片集成到单个封装中,从而减小面积、传输延迟等问题,但是两个mosfet芯片间仍然需要焊接线连接,会带来额外的寄生电感、电容、电阻,芯片的集成度比较低,另外,两个mosfet芯片分别通过外部控制电路对各自的栅极进行控制,使其交替开关,开启的时候器件温度会升高,关闭的时候器件温度会降低,两个mosfet芯片虽然集成到单个封装中,但仍然是相互独立的,那么温度传播可能不均匀,导致温度波动比较大,进而可能使焊接线脱落,从而引起可靠性问题。

技术实现思路

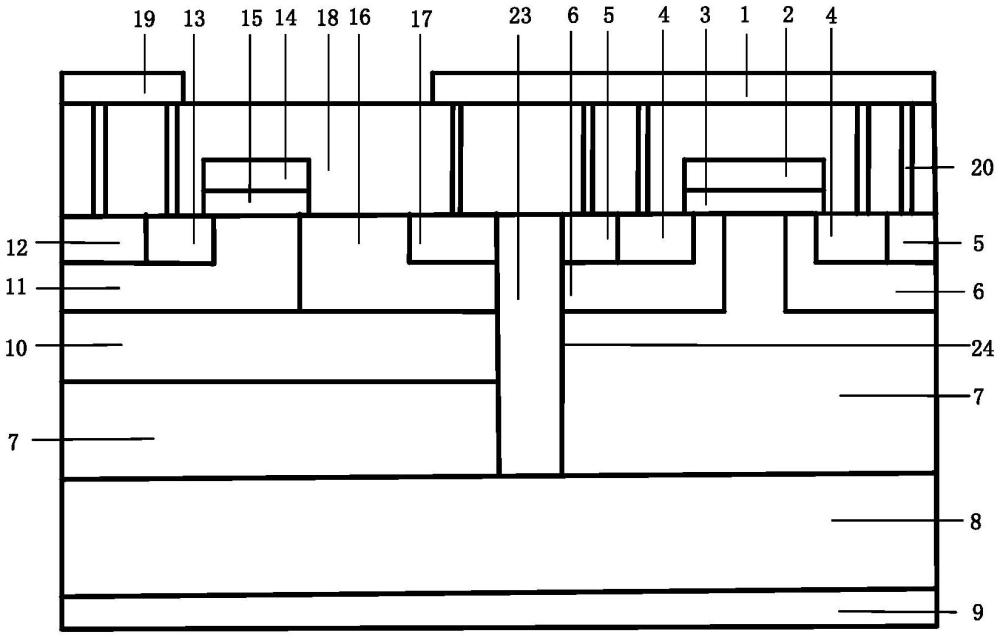

1、针对上述技术问题,本发明的目的之一在于提出一种高低边集成功率半导体器件,通过将两个mosfet集成到单一的硅片上,通过介质隔离区将两个mos器件隔离,从而抵挡器件之间的横向耐压,还通过金属走线使一个mos的源极和另一个mos的漏极相连接,金属走线提供低阻抗通道,从而形成一个高效紧凑的串联连接的单芯片解决方案,利于减小芯片占用pc b板的面积,实现高功率密度,降低温度波动,减小传输延迟,降低电磁干扰等。

2、本发明为了实现上述目的,采用如下技术方案:

3、一种高低边集成功率半导体器件,其元胞结构包括从下至上依次层叠设置的第一金属化漏极、第一n+漏区以及n-外延层;

4、n-外延层在沿其左右方向的中间位置设有第一沟槽,第一沟槽为纵向布置,且从n-外延层的上表面向下延伸到第一n+漏区的上表面;

5、第一沟槽内填充有介质材料,以形成介质隔离区;

6、第一沟槽的右侧设置有第一平面栅结构和第一p型基区;

7、第一p型基区有两个,且均包含在n-外延层的右侧区域中,两个第一p型基区分别位于n-外延层右侧区域中的顶部左侧以及右侧位置;

8、n-外延层右侧区域中的顶部中间位置位于两个第一p型基区之间;左侧的第一p型基区与第一沟槽的右侧面接触;

9、第一p型基区中包含第一p+低电阻率区和第一n+源区;

10、左侧的第一p型基区中,第一p+低电阻率区和第一n+源区侧面相互接触的位于左侧的第一p型基区的顶部左侧区域,且第一p+低电阻率区和第一n+源区为由左向右依次布置;左侧的第一p型基区的顶部右侧区域位于第一n+源区的右侧面与左侧的第一p型基区的右侧面之间;

11、右侧的第一p型基区中,第一p+低电阻率区和第一n+源区侧面相互接触的位于右侧的第一p型基区的顶部右侧区域,且第一p+低电阻率区和第一n+源区为由右向左依次布置;右侧的第一p型基区的顶部左侧区域位于第一n+源区的左侧面与右侧的第一p型基区的左侧面之间;

12、第一平面栅结构包含第一栅氧化层和第一栅电极,第一栅氧化层的底面与左侧的第一p型基区的顶部右侧区域、n-外延层的顶部中间位置、右侧的第一p型基区的顶部左侧区域、以及两个第一n+源区的顶面部分区域均接触;

13、第一栅电极位于第一栅氧化层的顶部表面;

14、第一沟槽的左侧设置有第二平面栅结构和p型阱区;

15、其中p型阱区位于n-外延层的左侧区域中,且p型阱区的右侧面与第一沟槽的左侧面接触;

16、p型阱区中包含第二p型基区和n-漂移区;

17、其中第二p型基区和n-漂移区分别位于p型阱区的顶部左侧区域以及顶部右侧区域,且第二p型基区的右侧面与n-漂移区的左侧面相互接触;

18、n-漂移区的右侧面与第一沟槽的左侧面相互接触;

19、第二p型基区中包含第二n+源区和第二p+低电阻率区;

20、第二n+源区和第二p+低电阻率区的侧面相互接触的位于第二p型基区的顶部左侧区域,第二p+低电阻率区位于第二n+源区的左侧;第二p型基区的顶部右侧区域位于第二n+源区的右侧面与第二p型基区的右侧面之间;

21、n-漂移区中包含第二n+漏区;

22、第二n+漏区位于n-漂移区的顶部右侧区域,n-漂移区的顶部左侧区域位于第二n+漏区的左侧面与n-漂移区的左侧面之间;

23、第二平面栅结构包含第二栅氧化层和第二栅电极;第二栅氧化层位于n-外延层左侧区域的上方;第二栅氧化层的底面与第二p型基区的顶部右侧区域、第二n+源区的顶面右侧部分区域以及n-漂移区的顶部左侧区域均接触;

24、第二栅电极位于第二栅氧化层的顶部表面;

25、在n-外延层的上方设有绝缘层,绝缘层内设有通孔;在绝缘层上方设有第一金属化源极和第二金属化漏极;

26、第一金属化源极位于第一p+低电阻率区、第一n+源区、第一平面栅结构和第二n+漏区的上方;第二金属化漏极位于第二n+源区和第二p+低电阻率区的上方;第一金属化源极通过通孔与第一p+低电阻率区、第一n+源区和第二n+漏区进行欧姆接触;第二金属化漏极通过通孔与第二n+源区和第二p+低电阻率区进行欧姆接触。

27、此外,在上述高低边集成功率半导体器件的基础上,本发明还提出了一种新的高低边集成功率半导体器件,在该高低边集成功率半导体器件中,将第一平面栅结构改为普通沟槽栅结构,其他结构与上述高低边集成功率半导体器件中的结构相同。

28、此外,在上述高低边集成功率半导体器件的基础上,本发明还提出了一种新的高低边集成功率半导体器件,在该高低边集成功率半导体器件中,进一步将普通沟槽栅结构改为屏蔽栅结构,其他结构与上述高低边集成功率半导体器件中的结构相同。

29、此外,在上述几种高低边集成功率半导体器件的基础上,还可以进一步将控制电路部分与高低边集成功率半导体器件集成在一起,组成智能功率开关。

30、具体而言,高低边集成功率开关,包括控制电路以及高低侧器件,高低侧器件和控制电路集成在同一衬底上并电连接;控制电路包括驱动电路,用于驱动高低侧器件。

31、其中,高低侧器件采用如上面所述的高低边集成功率半导体器件中的任意一种均可。

32、本发明通过将控制电路部分与高低边集成功率半导体器件集成在一起,组成智能功率开关的方式,极大减小了占用pcb板的面积,提高了集成度,降低了传输延迟和电磁干扰等。

33、本发明具有如下优点:

34、如上所述,本发明提供了一种高低边集成功率半导体器件,该高低边集成功率半导体器件采用单芯片集成方案,即在同一衬底上集成两个mos器件,通过介质隔离区将两个mos器件隔离,从而抵挡器件之间的横向耐压,另外本发明通过金属走线使一个mos的源极和另一个mos的漏极相连接,金属走线提供低阻抗通道,从而实现高效紧凑的串联连接,在上述高低边集成功率半导体器件的基础上,可进一步将控制电路和本发明所提高低边集成功率半导体器件集成在同一衬底上,形成高低边集成功率开关,即智能功率开关,减小了芯片占用pcb板的面积,实现了高功率密度,降低了温度波动,减小了传输延迟,降低了电磁干扰等。本发明所提单芯片集成方案,有助于实现高效的电流控制和开关管理,特别是在需要高电压和电流控制的应用场合,比如buck电路、boost电路以及半桥电路等等。

本文地址:https://www.jishuxx.com/zhuanli/20240911/290480.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表