一种新型的QFN封装结构的制作方法

- 国知局

- 2024-09-11 14:58:19

本发明属于半导体芯片封装,尤其涉及一种新型的qfn封装结构。

背景技术:

1、单管是指将功率开关器件,如绝缘栅双极晶体管,金属-氧化物半导体场效应晶体管,快速恢复二极管的单颗芯片封装成一个整体,通过组合,完成直流/交流的双方转换,利用电池或其他能量驱动电机运转。实现电流转换的模块;在单管的应用中,表贴器件以其简单的应用方式,大量在电源模块,光伏风电以及车载中应用目前的表贴器件由于其体积较大,散热不好以及回路电感较大等劣势,在一定程度上限制了表贴单管器件的使用;

2、在传统的单管表贴器件的封装中,信号pin(gate和source)以及功率source pin均位于塑封体外部,且一一分开,体积较大;芯片功率source极与功率source pin采用打线连接,回路电感大,通流低,且没有散热效果;芯片信号极(gate和source)与pin之间采用平行打线,驱动回路电感较大。

3、为了避免上述情况,因此,设计一种新型的qfn封装结构是有必要的。

技术实现思路

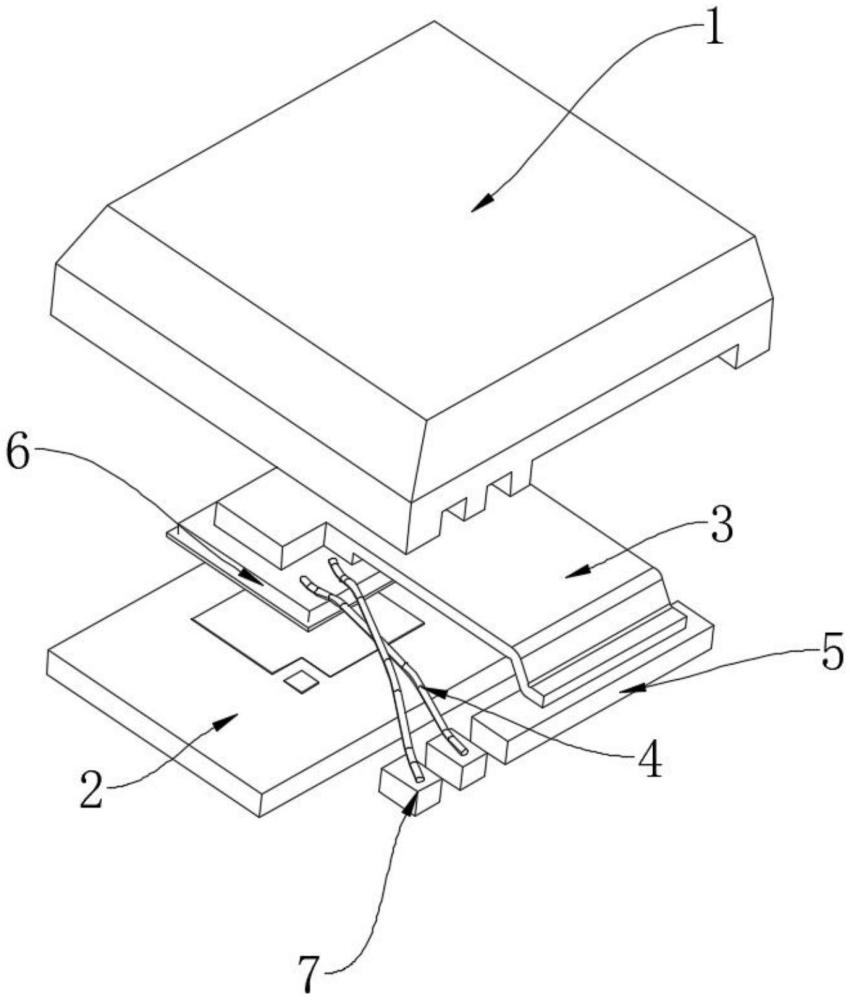

1、本发明提供一种新型的qfn封装结构,旨在解决在传统的单管表贴器件的封装中,信号pin(gate和source)以及功率source pin均位于塑封体外部,且一一分开,体积较大;芯片功率source极与功率source pin采用打线连接,回路电感大,通流低,且没有散热效果;芯片信号极(gate和source)与pin之间采用平行打线,驱动回路电感较大的问题。本发明是这样实现的,一种新型的qfn封装结构,包括上塑封体、功率source pin和下塑封垫:所述下塑封垫的内壁设置有芯片,所述芯片的source上连接有信号线,所述信号线的一端连接有信号pin;

2、其中,信号pin和功率source pin均位于上塑封体和下塑封垫内部;减小了整个单管的体积;其中sourcepin集成为一个整体,结构更为简单。

3、优选地,所述芯片可以有一颗或者几颗并联。

4、优选地,所述信号线的数量为多个,且多个信号线之间采用交叉打线方案;通过多个信号线之间采用交叉打线方案的设置,与传统的平行打线不同,采用交叉打线方案,减小驱动回路电感。

5、优选地,所述芯片的外壁焊接有铜夹,所述芯片和功率source pin之间通过铜夹连接;相比于打线方案,降低回路电感,同时增大通流能力;同时铜夹与芯片的整个sourcepad相连接,为芯片提供了顶部的散热通道,能够更好的散热。

6、优选地,所述上塑封体的长度和宽度为3mm-3.2mm,所述塑封体的高度为1mm-1.2mm。

7、优选地,所述上塑封体的底部开设有数个契合槽,且契合槽的内壁分别与下塑封垫、功率source pin和信号pin的外壁贴合连接。

8、与现有技术相比,本申请实施例主要有以下有益效果:1、通过信号pin和功率source pin均位于上塑封体和下塑封垫内部的设置;减小了整个单管的体积;其中sourcepin集成为一个整体,结构更为简单;

9、2、通过芯片和功率source pin之间通过铜夹连接;相比于打线方案,降低回路电感,同时增大通流能力;同时铜夹与芯片的整个source pad相连接,为芯片提供了顶部的散热通道,能够更好的散热;

10、3、通过多个信号线之间采用交叉打线方案的设置,与传统的平行打线不同,采用交叉打线方案,减小驱动回路电感。

技术特征:1.一种新型的qfn封装结构,其特征在于,包括上塑封体(1)、功率source pin(5)和下塑封垫(2):所述下塑封垫(2)的内壁设置有芯片(6),所述芯片(6)的source上连接有信号线(4),所述信号线(4)的一端连接有信号pin(7);

2.如权利要求1所述的一种新型的qfn封装结构,其特征在于,所述芯片(6)可以有一颗或者几颗并联。

3.如权利要求1所述的一种新型的qfn封装结构,其特征在于,所述信号线(4)的数量为多个,且多个信号线(4)之间采用交叉打线方案。

4.如权利要求1所述的一种新型的qfn封装结构,其特征在于,所述芯片(6)的外壁焊接有铜夹(3),所述芯片(6)和功率source pin(5)之间通过铜夹(3)连接。

5.如权利要求1所述的一种新型的qfn封装结构,其特征在于,所述上塑封体(1)的长度和宽度为3mm-3.2mm,所述塑封体的高度为1mm-1.2mm。

6.如权利要求1所述的一种新型的qfn封装结构,其特征在于,所述上塑封体(1)的底部开设有数个契合槽,且契合槽的内壁分别与下塑封垫(2)、功率source pin(5)和信号pin(7)的外壁贴合连接。

技术总结本发明适用于半导体芯片封装技术领域,提供了一种新型的QFN封装结构,包括上塑封体、功率source pin和下塑封垫:所述下塑封垫的内壁设置有芯片,所述芯片的source上连接有信号线,所述信号线的一端连接有信号pin;其中,信号pin和功率source pin均位于上塑封体和下塑封垫内部;减小了整个单管的体积;其中source pin集成为一个整体;所述芯片可以有一颗或者几颗并联;所述信号线的数量为多个,且多个信号线之间采用交叉打线方案;通过多个信号线之间采用交叉打线方案的设置,与传统的平行打线不同,采用交叉打线方案,减小驱动回路电感;通过信号pin和功率source pin均位于上塑封体和下塑封垫内部的设置;减小了整个单管的体积;其中source pin集成为一个整体,结构更为简单。技术研发人员:张振中,郝建勇,刘玮受保护的技术使用者:苏州中瑞宏芯半导体有限公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/292727.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表