一种面向超导量子器件的可扩展多芯粒集成封装架构及其制备方法

- 国知局

- 2024-09-14 14:26:50

本发明涉及一种面向超导量子器件的可扩展多芯粒集成封装架构及其制备方法,属于超导量子器件。

背景技术:

1、随着半导体工艺制程不断趋近技术极限,摩尔定律面向集成电路领域所预测的高发展速度将难以继续维持,因此各类新的计算范式逐渐成为信息产业进一步突破算力瓶颈的重要途径。

2、其中,量子计算机由于在特定的科学问题上相较于经典计算机表现出指数级优越性,现阶段广受关注。在用于实现量子计算的各类物理平台中(超导、光量子、离子阱等),超导量子比特因可扩展能力强、与半导体工艺兼容程度高、易于测控及耦合、相关元器件可平面化制备等优点,成为现阶段有望实现可扩展通用量子计算的主流技术方案之一。以ibm、google为代表的一系列著名信息科技公司在超导量子计算领域均进行了长期的战略部署及大量的资金投入,现阶段产业界已能够实现数百量级比特数目的超导量子处理器。

3、然而,要真正推动其商业化落地至少需要千级数量的量子比特,若进一步构建高容错、可扩展的大规模通用量子计算机,则更是需要百万量级的量子比特作为其硬件基础。其中,每个量子比特均需配置相应的测控线路以完成计算任务,同时还需要在稀释制冷机(利用超流4he稀释其同位素3he的吸热过程产生极低温环境)提供的极低温环境下工作,因此产生了复杂的封装及布线需求。

4、现阶段利用二维封装形式实现的平面型超导量子处理器已面临集成度瓶颈,因下述原因而难以进一步提升量子比特的数目:

5、(1)平面构型中各类结构均制备在同一块芯片上,而多层金属布线之间用于绝缘功能的非晶介质材料内部存在很多缺陷,其在极低温环境中会表现出二能级系统的特性,但具体的能级状态难以像量子比特一样被精确设计和控制,进而形成干扰并加速退相干现象的发生;

6、(2)周边焊盘排布形式造成芯片面积的快速扩大,稀释制冷机内部有限的测试空间无法支持大规模平面型量子处理器的制冷需求;

7、(3)二维封装结构中常用的引线键合技术可能产生极低温下机械应力、界面处阻抗失配、平行线间信号串扰等不利影响。

8、针对上述问题,目前产业界、学术界有部分科研人员开展了面向超导量子器件的三维封装结构的探索工作。但是现有技术能够支持的集成规模较小、成本较高、良率偏低、大规模扩展性未知,且缺乏整体架构层面的统一设计。

技术实现思路

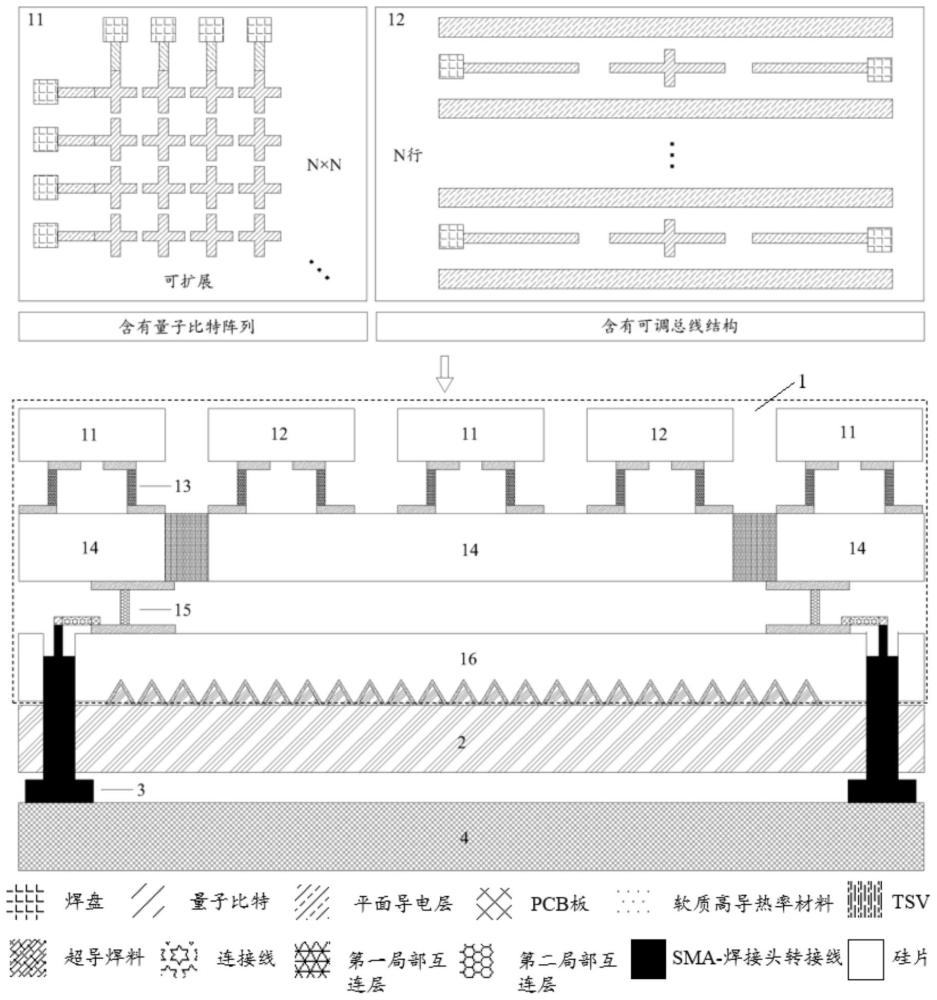

1、为解决上述技术问题,本发明的目的在于提供一种面向超导量子器件的可扩展多芯粒(chiplet)集成封装架构及其制备方法。本发明重点聚焦于芯粒划分策略[ⅰ型芯粒(含有量子比特阵列)、ⅱ型芯粒(含有可调总线结构)]、相适配的层内(硅通孔)、层间(倒装键合)互连技术及系统集成方案,以期实现超导量子比特数量及质量上的进一步提升,为大规模通用量子计算奠定硬件基础。

2、为了实现上述目的,本发明第一方面提供了一种面向超导量子器件的可扩展多芯粒(chiplet)集成封装架构,其中,所述集成封装架构包括:可扩展的超导多芯片模块(superconducting multi-chip module,s-mcm)、热沉块、sma-焊接头转接线以及pcb板;

3、所述可扩展的超导多芯片模块自上至下包括:若干ⅰ型芯粒和若干ⅱ型芯粒、第一局部互连层、tsv(硅通孔,through silicon via)转接板、第二局部互连层、超导封装基板;

4、所述ⅰ型芯粒和所述ⅱ型芯粒交叉排列并通过所述第一局部互连层键合在所述tsv转接板上;所述tsv转接板通过所述第二局部互连层键合在所述超导封装基板上;所述超导封装基板在其信号引出端焊盘附近设置有通孔,用于穿入所述sma-焊接头转接线;

5、所述热沉块设置有通孔,用于穿入所述sma-焊接头转接线;

6、所述超导封装基板安装在所述热沉块上;

7、所述sma-焊接头转接线用于传输测控信号,其从所述超导封装基板和所述热沉块的通孔中穿出;所述sma-焊接头转接线的焊接头焊接于所述超导封装基板顶部的信号引出端焊盘,所述sma-焊接头转接线的sma头公母匹配安装于所述pcb板上。

8、在上述的集成封装架构中,优选地,所述ⅰ型芯粒含有量子比特阵列,所述ⅱ型芯粒含有可调总线结构,所述可调总线结构包括两个λ/2共面波导谐振腔通过一个频率可调的量子比特相连的结构。所述ⅰ型芯粒中的量子比特阵列具有计算所需的耦合结构。所述ⅱ型芯粒起到连接、耦合两侧相邻的所述ⅰ型芯粒的作用。

9、在本发明的一些具体实施方式中,所述ⅰ型芯粒中的量子比特的类型可以包括磁通、电荷、相位、transmon等各类主流的量子比特类型,优选为transmon量子比特。所述ⅱ型芯粒中的量子比特可选择各类频率可调的量子比特,优选为transmon量子比特。

10、在本发明的一些具体实施方式中,所述ⅰ型芯粒中的量子比特阵列和所述ⅱ型芯粒中的可调总线结构是利用深紫外光(三层膜工艺)或电子束光刻(双角度蒸发工艺)套刻制备的。这两种光刻技术均为本领域常规技术,本发明不对其具体步骤进行特殊限定。

11、本领域技术人员能够理解的是,本发明中的所述ⅰ型芯粒和所述ⅱ型芯粒应包括常规超导量子计算芯片所必须包括的结构和单元。在本发明的一些具体实施方式中,所述ⅰ型芯粒和所述ⅱ型芯粒包括晶圆衬底、在晶圆衬底上形成的约瑟夫森结以及非量子比特的其他辅助结构,所述非量子比特的其他辅助结构包括位于芯粒周边(一般为倒装后的芯粒的下表面)的阵列焊盘、芯粒表面的金属互连线路、量子比特间必要的耦合结构等。阵列焊盘、金属互连线路、耦合结构均可以采用本领域常规的结构。本领域技术人员可以理解的是,金属互连线路起到平面内不同元器件之间的连接作用,主要用于平面内不同元器件之间的信号传输,不参与到层间垂直方向上的互连(倒装键合)中。

12、约瑟夫森结是量子比特的物理承载实体之一。约瑟夫森结是一种三层薄膜构成的结构,上下两层均为超导体层,其材料为可在低温超导的金属,如nb基材料或者al基材料,中间夹一层半导体层或绝缘体层,通常是超导金属的氧化物,例如三氧化二铝等。在本发明的一些具体实施方式中,约瑟夫森结中的超导体层的材料优选为al基材料。

13、在本发明的一些具体实施方式中,位于芯粒周边的阵列焊盘的数量可以为4n个,其中n表示芯粒上的单排量子比特的数量。焊盘材料可以选择tin基、al基、ti基、w基、alcu基、in基、nb基、ta基、nbn基和nbtin基等超导材料中的一种或几种。

14、在本发明的一些具体实施方式中,芯粒表面的金属互连线路及耦合结构的材料可以选择tin基、al基、ti基、w基、alcu基、in基、nb基、ta基、nbn基和nbtin基等超导材料中的一种或几种。

15、在本发明的一些具体实施方式中,芯粒的晶圆衬底包括蓝宝石衬底或表面形成有氧化硅或氮化硅作为绝缘层的硅衬底。优选地,芯粒的晶圆衬底为蓝宝石衬底。

16、在本发明中,tsv转接板主要承担两个功能:

17、(1)作为三维集成技术的必要结构,承担层内垂直方向上的信号传输功能;

18、(2)为顶层各芯粒上的量子比特与下层超导封装基板上的层间介质之间提供足够的空间隔离。因为金属层间用于实现电绝缘的非晶介质材料内部存在缺陷,这些缺陷在低温环境下会表现出二能级系统的性质,其所处的具体能级状态难以像量子比特一样被精确设计和控制,从而引发不可忽视的量子比特退相干效应。

19、在上述的集成封装架构中,优选地,所述tsv转接板是至少通过以下步骤制备得到的:

20、在硅晶圆衬底的一个表面生长二氧化硅层;

21、在硅晶圆衬底的另一个表面进行光刻以定义tsv图形;

22、然后对硅晶圆衬底进行drie刻蚀以形成tsv;

23、去除光刻胶和二氧化硅层;

24、然后在硅晶圆衬底的全表面生长二氧化硅作为绝缘层;

25、在所述绝缘层的全表面生长超导材料作为全局导电层;

26、在硅晶圆衬底的上、下表面的全局导电层上生长超导材料作为平面导电层,并通过光刻定义线路和焊盘图形,利用干法刻蚀去除非图形区域的全局导电层和平面导电层,并去除光刻胶,进而在硅晶圆衬底的两个表面均形成线路和焊盘结构,得到所述tsv转接板。

27、在本发明的一些具体实施方式中,在上述的tsv转接板制备步骤中,首先在硅晶圆衬底的一个表面生长二氧化硅层,能够防止drie刻蚀的过程中硅脂进入硅通孔造成污染并影响刻蚀进程。该二氧化硅层是通过薄膜生长工艺形成于硅晶圆衬底的一个表面的。该薄膜生长工艺可选择cvd、pvd、ald等兼容的生长技术中的一种或几种。这些薄膜生长技术均为本领域的常规技术,本发明不对其具体步骤进行特殊限定。

28、在本发明的一些具体实施方式中,在上述的tsv转接板制备步骤中,为了满足高集成密度、量子比特空间隔离和夹持工艺对高深宽比tsv的需求,应对硅晶圆衬底的直径、厚度进行合理设计。

29、在本发明的一些具体实施方式中,在上述的tsv转接板制备步骤中,所述全局导电层的超导材料包括tin基、al基、ti基、w基、alcu基、in基、nb基、ta基、nbn基和nbtin基等超导材料中的一种或几种。优选地,可以选择加偏压的直流磁控溅射技术在绝缘层上生长al以形成全局导电层;或者在绝缘层上覆盖熔融态in,并通过硅晶圆衬底两侧的压力差实现熔融态in在tsv内部的填充,进而形成全局导电层;或者通过薄膜生长工艺(优选ald)在绝缘层上生长tin以形成全局导电层。这些技术均为本领域常规技术,本发明不对其具体步骤进行特殊限定。更优选地,所述全局导电层为tin层,其是利用ald技术生长的。tin层更易保证tsv内部实现导电层的均匀、连续覆盖。

30、在本发明的一些具体实施方式中,在上述的tsv转接板制备步骤中,所述平面导电层的超导材料包括tin基、al基、ti基、w基、alcu基、in基、nb基、ta基、nbn基和nbtin基等超导材料中的一种或几种。

31、在本发明的一些具体实施方式中,在上述的tsv转接板制备步骤中,所述干法刻蚀包括反应离子刻蚀、等离子刻蚀、溅射与离子铣等各向异性强、选择性高的工艺。这些干法刻蚀工艺均为本领域的常规工艺,本发明不对其具体步骤进行特殊限定。优选地,所述干法刻蚀采用电感耦合等离子体刻蚀(icp)。

32、在上述的集成封装架构中,优选地,所述超导封装基板上键合有多个tsv转接板。本领域技术人员可以理解的是,多个tsv转接板上均键合有若干ⅰ型芯粒和若干ⅱ型芯粒。

33、在上述的集成封装架构中,优选地,所述超导封装基板的底部具有若干v型槽;所述热沉块的顶部具有若干倒v型凸起;所述可扩展的超导多芯片模块通过所述超导封装基板底部的若干v型槽和所述热沉块顶部的若干倒v型凸起安装嵌合在所述热沉块上。

34、在上述的集成封装架构中,优选地,所述超导封装基板是至少通过以下步骤制备得到的:

35、在硅晶圆衬底的一个表面生长二氧化硅层;

36、在所述二氧化硅层的表面进行光刻以定义v型槽图形;

37、利用干法刻蚀去除v型槽图形区域的二氧化硅层,得到掩蔽层;

38、再利用所述掩蔽层,采用湿法各向异性刻蚀对特定晶向的硅进行各向异性刻蚀,形成若干v型槽;

39、在硅晶圆衬底上与若干v型槽相对的表面形成焊盘,作为信号引出端焊盘;

40、在所述信号引出端焊盘的附近制备通孔,用于穿入sma-焊接头转接线;

41、在硅晶圆衬底与若干v型槽相对的表面形成辅助图形。

42、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,该二氧化硅层是通过薄膜生长工艺形成于硅晶圆衬底的一个表面的。该薄膜生长工艺可选择cvd、pvd、ald等兼容的生长技术中的一种或几种。

43、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,在所述二氧化硅层的表面进行光刻以定义v型槽图形时,正负胶、亮暗板的组合应保证v型槽区域裸露、不受光刻胶遮蔽。

44、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,所述干法刻蚀包括反应离子刻蚀、等离子刻蚀、溅射与离子铣等各向异性强、选择性高的工艺。

45、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,所述湿法各向异性刻蚀所采用的刻蚀液优选包括氢氧化钾(koh)和异丙醇(ch3)2choh的混合液。该混合液中氢氧化钾和异丙醇的浓度可以由本领域技术人员进行常规调节。利用氢氧化钾和异丙醇的混合液对(100)晶向的硅进行各向异性刻蚀,能够产生清晰的v型槽结构,v型槽的边缘为(111)晶面,与(100)晶面有54.7°夹角。

46、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,所述通孔是利用微机械加工或光刻+drie刻蚀的方式制备的。这些通孔制备技术均为本领域常规的技术,本发明不对其具体步骤进行特殊限定。

47、在本发明的一些具体实施方式中,在上述的超导封装基板制备步骤中,所述辅助图形是通过多步光刻及刻蚀形成的。优选地,所述辅助图形包括用于直流和高频信号传输的布线层、电源层、接地层、屏蔽层、电极、电容、传输线、谐振腔、层间绝缘介质等,其中具有信号传输功能的布线层、电极、电容、传输线、谐振腔等电学结构的材料包括tin基、al基、ti基、w基、alcu基、in基、nb基、ta基、nbn基和nbtin基等超导材料中的一种或几种,优选包括al基、nb基、ta基和tin基超导材料等中的一种或几种。

48、在上述的集成封装架构中,优选地,所述第一局部互连层和所述第二局部互连层包括in基凸点和pb-sn基凸点中的一种或几种。更优选地,所述第一局部互连层包括in基凸点;所述第二局部互连层包括pb-sn基凸点。进一步优选地,所述pb-sn基凸点为pb-sn共晶凸点。

49、在上述的集成封装架构中,优选地,所述第一局部互连层和所述第二局部互连层分别包括in基凸点键合互连层或pb-sn基凸点键合互连层,更优选分别包括in柱热压键合互连层或pb-sn共晶凸点回流焊互连层。进一步优选地,所述第一局部互连层为in基凸点键合互连层,优选为in柱热压键合互连层;所述第二局部互连层为pb-sn基凸点键合互连层,优选为pb-sn共晶凸点回流焊互连层。

50、在本发明的一些具体实施方式中,所述第一局部互连层为in基凸点键合互连层,优选为in柱热压键合互连层,其包括第一ubm结构、第一in基凸点、第二in基凸点、第二ubm结构;第一in基凸点通过第一ubm结构连接于ⅰ型芯粒和ii型芯粒的焊盘上,第二in基凸点通过第二ubm结构连接于tsv转接板顶部的焊盘上;第一in基凸点和第二in基凸点相连。

51、在本发明的一些具体实施方式中,所述第二局部互连层为in基凸点键合互连层,优选为in柱热压键合互连层,其包括第一ubm结构、第一in基凸点、第二in基凸点、第二ubm结构;第一in基凸点通过第一ubm结构连接于tsv转接板底部的焊盘上,第二in基凸点通过第二ubm结构连接于超导封装基板顶部的焊盘上;第一in基凸点和第二in基凸点相连。

52、在本发明的一些具体实施方式中,所述第一局部互连层为pb-sn基凸点键合互连层,优选为pb-sn共晶凸点回流焊互连层,其包括第一ubm结构、第一pb-sn基凸点、第二pb-sn基凸点、第二ubm结构;第一pb-sn基凸点通过第一ubm结构连接于ⅰ型芯粒和ii型芯粒的焊盘上,第二pb-sn基凸点通过第二ubm结构连接于tsv转接板顶部的焊盘上;第一pb-sn基凸点和第二pb-sn基凸点相连。

53、在本发明的一些具体实施方式中,所述第二局部互连层为pb-sn基凸点键合互连层,优选为pb-sn共晶凸点回流焊互连层,其包括第一ubm结构、第一pb-sn基凸点、第二pb-sn基凸点、第二ubm结构;第一pb-sn基凸点通过第一ubm结构连接于tsv转接板底部的焊盘上,第二pb-sn基凸点通过第二ubm结构连接于超导封装基板顶部的焊盘上;第一pb-sn基凸点和第二pb-sn基凸点相连。

54、在本发明的一些具体实施方式中,若制备局部互连层的工艺周期较长,则in基凸点键合互连层和/或pb-sn基凸点键合互连层可以分别进一步包括au层,au层设置于第一in基凸点和第二in基凸点之间,和/或设置于第一pb-sn基凸点和第二pb-sn基凸点之间,作为防氧化层。

55、在本发明的一些具体实施方式中,in基凸点键合互连层和/或pb-sn基凸点键合互连层分别包括扩散阻挡层,其被设置为ubm结构的其中一层,用于防止凸点和焊盘间发生化学反应形成非超导的金属间化合物材料;优选地,所述扩散阻挡层的材料包括tin和/或nbn等。

56、凸点与焊盘之间在键合过程中若可能发生化学反应形成非超导的金属间化合物(intermetallic compound,imc),则需要设置扩散阻挡层以防止非超导imc的大量生成。

57、举例而言,若ⅰ型芯粒和ii型芯粒的焊盘的材料为al,和/或tsv转接板顶部的焊盘为al,则in基凸点键合互连层进一步包括扩散阻挡层,以防止al、in形成大量非超导imc。若ⅰ型芯粒和ii型芯粒的焊盘的材料为nb,且tsv转接板顶部焊盘的材料为nb,则in基凸点键合互连层无需设置扩散阻挡层,因为其反应生成的imc nb3in为超导材料。

58、本领域技术人员可以理解的是,在集成封装架构中,在制备层间互连用的凸点时,需要在焊盘与凸点之间设置凸点下金属化层(under bump metallurgy,ubm)结构作为过渡层。ubm结构一般可以包括覆盖在焊盘上的粘接层、扩散阻挡层、润湿层等中一层或几层结构。本发明不对ubm结构进行具体限定,仅限定了其中的扩散阻挡层,其他层可以由本领域技术人员根据实际情况采用超导材料进行常规设置,也可以不设置其他层。

59、在本发明的一些具体实施方式中,在上述的第一局部互连层和第二局部互连层中,ubm结构(包括扩散阻挡层)、in基凸点、pb-sn基凸点、au层等均可以利用薄膜生长工艺制备。该薄膜生长工艺可选择cvd、pvd、ald、电镀、化学镀等兼容的生长技术中的一种或几种。例如,ubm结构中的tin扩散阻挡层可通过溅射或ald制得;in基凸点可通过热蒸发制得;pb-sn基凸点可通过电镀或化学镀制得。

60、本发明的集成封装架构中的倒装键合采用in凸点键合或pb-sn共晶凸点键合,in、pb-sn共晶均为超导材料,可以实现极低温环境下的无损互连。本发明优选在芯粒、tsv转接板之间使用in凸点热压键合互连,在tsv转接板、封装基板之间使用pb-sn共晶凸点回流焊互连,由于后者的工艺温度更高,可以保证取下、再键合顶部芯粒的过程中不影响下层凸点的可靠性,进而实现芯粒的可替换功能。

61、在上述的集成封装架构中,所述热沉块的材料可以选择各类高导热率材料,优选包括铜、钨铜和金刚石等中的一种或几种,更优选为铜。

62、在本发明的一些具体实施方式中,所述热沉块的倒v型凸起结构可以是通过机械加工的方式制备的。本领域技术人员可以理解的是,该倒v型凸起应与所述超导封装基板底部的v型槽相嵌合。

63、在上述的集成封装架构中,优选地,所述超导封装基板底部的若干v型槽与所述热沉块的若干倒v型凸起之间具有填充材料。所述填充材料可以为软质的高导热率材料,优选包括银、铟和导热胶等中的一种或几种。

64、在本发明的一些具体实施方式中,所述热沉块的通孔是通过机械加工的方式制备的。所述热沉块的通孔尺寸、位置应与所述超导封装基板的通孔尺寸、位置相对应。

65、在上述的集成封装架构中,所述sma-焊接头转接线用于实现直流和高频测控信号的高质量输入和/或输出。

66、在上述的集成封装架构中,优选地,所述sma-焊接头转接线的焊接头通过超导材料和连接线焊接于所述超导封装基板顶部的信号引出端焊盘。

67、在上述的集成封装架构中,优选地,用于焊接所述sma-焊接头转接线的焊接头和所述超导封装基板顶部的信号引出端焊盘的超导材料包括in和/或pb-sn等。

68、在上述的集成封装架构中,所述pcb板可以采用本领域常规的可实现所需测试功能的pcb板,本发明不对其具体结构和制备方法进行特殊限定。

69、在本发明的一些具体实施方式中,所述pcb板的顶部与超导封装基板和热沉块的通孔相对应的位置安装有sma母头,用于与sma-焊接头转接线的sma公头匹配连接。

70、本发明第二方面提供了一种上述的面向超导量子器件的可扩展多芯粒集成封装架构的制备方法,其包括以下步骤:

71、(1)将若干i型芯粒、若干ii型芯粒、tsv转接板、超导封装基板进行光刻以定义凸点图形,将若干i型芯粒和若干ii型芯粒以交叉排列的方式通过薄膜生长工艺制备的第一局部互连层倒装键合于tsv转接板上,得到芯粒-tsv转接板封装体;

72、(2)将超导封装基板安装在热沉块上;

73、(3)将sma-焊接头转接线的焊接头朝上、sma头朝下,从超导封装基板和热沉块的通孔中穿出;将sma-焊接头转接线的焊接头通过超导材料和连接线焊接在超导封装基板顶部的信号引出端焊盘上;

74、(4)将芯粒-tsv转接板封装体通过薄膜生长工艺制备的第二局部互连层倒装键合在超导封装基板上,得到可扩展的超导多芯片模块;

75、(5)将sma-焊接头转接线的sma头公母匹配安装于pcb板上,得到所述的面向超导量子器件的可扩展多芯粒集成封装架构。

76、在上述的制备方法中,优选地,在步骤(1)中,若干i型芯粒和若干ii型芯粒在放置于tsv转接板的对应焊接位置后,是通过一次倒装键合进而实现整体互连的。

77、在上述的制备方法中,优选地,步骤(2)具体包括:在超导封装基板底部的v型槽内部生长或涂覆软质的高导热率材料,随后将热沉块的倒v型凸起与超导封装基板的v型槽紧密嵌合,并双向加压,使得软质的高导热率材料形变并充分填充凸起-凹槽间的空隙。

78、在上述的制备方法中,优选地,在步骤(3)中,将sma-焊接头转接线的焊接头使用超导材料焊接在连接线的一侧端子上,并将连接线的另一侧端子使用超导材料焊接在超导封装基板顶部的信号引出端焊盘上。

79、在上述的制备方法中,优选地,在步骤(4)中,芯粒-tsv转接板封装体与超导封装基板是通过一次倒装键合进而实现整体互连的。

80、在上述的制备方法中,优选地,在步骤(4)中,将多个芯粒-tsv转接板封装体通过薄膜生长工艺制备的第二局部互连层倒装键合在超导封装基板上,得到可扩展的超导多芯片模块。

81、本发明第三方面提供了一种超导量子计算机,其至少包括上述的面向超导量子器件的可扩展多芯粒集成封装架构,以及稀释制冷机,所述可扩展多芯粒集成封装架构中的pcb板通过测试线路与所述稀释制冷机进行通信。

82、本领域技术人员可以理解的是,上述超导量子计算机还应包括其他必须的组件,例如显示控制系统、测量系统、低温电子元件等,本发明不对这些组件进行特殊限定。

83、本发明提出了一种新的超导量子器件的集成封装架构。鉴于集成电路封装行业的发展脉络,本发明利用芯粒设计方法学及三维集成技术,重点聚焦于芯粒划分策略[ⅰ型芯粒(含有量子比特阵列)、ⅱ型芯粒(含有可调总线结构)]、相适配的层内(硅通孔)、层间(倒装)互连技术及系统集成方案,研发了高集成度、可复用、可扩展能力强、设计周期短、良率高、兼容性强、电学及热学性能优良的超导量子器件模块化集成技术,用以解决现行量子封装技术的集成度瓶颈问题,以期实现超导量子比特数量及质量上的进一步提升,为大规模通用量子计算奠定硬件基础。

84、与传统二维量子封装技术及处于探索阶段的现行三维量子封装技术相比,本发明的技术方案至少具有以下有益技术效果:

85、(1)设计了完整的多芯粒集成封装架构,兼顾了超导量子处理器成本控制、退相干抑制、导电性能、热管理、面市周期、生产效率等多方面的综合需求。

86、(2)通过已知良好芯片(known-good-die,kgd)的筛选,可以保证系统集成阶段所用芯粒的高良率,进而解决超导量子处理器整体良率随着集成规模增大而迅速减小的问题。

87、(3)ⅰ型芯粒、ⅱ型芯粒均可通过快速局部加热进行单独替换,大幅优化了系统整体的利用效率和修复成本。可在芯粒、tsv转接板之间使用in凸点互连,在tsv转接板、封装基板之间使用pb-sn共晶凸点互连,由于后者的键合温度更高,可以保证取下、再键合顶部芯粒的过程中不影响下层凸点的可靠性,以实现失效点位的精确定位和低成本修复,进而实现芯粒的可替换功能。

88、(4)芯粒键合、芯粒-转接板封装体键合步骤均可在放置完成后通过一次键合工艺整体完成,缩短了工艺步骤,减少了反复升降温过程对约瑟夫森结的不利影响。

89、(5)超导封装基板允许搭载多个tsv转接板,不同转接板之间可以搭载不同类型(例如磁通、电荷、相位、transmon等)、不同数量的ⅰ型芯粒、ⅱ型芯粒,在保证良率的前提下大幅提升了系统的大规模可扩展性,同时有助于为不同类型量子比特性能的横向对比提供便捷的测试平台。

90、(6)s-mcm与测试pcb板之间的信号传输使用sma-焊接头转接线实现,有助于保证高频信号的传输质量、减小失真度;同时,sma公母头便于拆装,减少了测试样片拆装、更替过程中带来的机械失效风险。

91、(7)tsv转接板为顶层各芯粒上的量子比特与下层超导封装基板上的层间介质之间提供了足够的空间隔离,避免极低温下量子比特的相干性能受到介质材料中tls的干扰。

92、(8)超导封装基板的v型槽和高热导率的热沉块的倒v型凸起的紧密嵌合,有助于通过增大有效热界面面积来提升散热效率,可以缓解部分非超导区域在服役过程中的电阻发热积累对量子态产生的不利影响。

本文地址:https://www.jishuxx.com/zhuanli/20240914/294128.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表