基于激光解键合的MoS2/Si异质结光电探测器与MOSFET三维集成方法及结构

- 国知局

- 2024-09-14 14:58:36

本发明属于集成电路制造,具体涉及基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法及结构。

背景技术:

1、光电探测器(photodetector,pd)是一种将光信号转化为电信号的器件,被广泛应用于图像传感、光通信、环境检测、红外测量等领域。传统的光电探测器主要基于硅(si)、砷化镓(gaas)等无机半导体材料,随着技术的发展石墨烯(graphene)、过渡金属硫化物(transition metal dichalcogenides,tmdcs)、黑磷(black phosphorus)为代表的二维材料(2d materials,2dm)具有优良的光学、电学、热学性质,被认为具有潜力开发低成本高性能的光电探测器。

2、二硫化钼(mos2)具有直接禁带结构,在多层和单层结构下分别有1.8ev和1.3ev的禁带宽度,光吸收能力也比si和gaas更高,响应波长范围也更宽(350-950nm),从可见光达到了近红外。二维mos2与体si的异质结结构,由于其pn结产生的强电场在太阳能电池和光电探测器领域有广泛应用。采用mos2与硅基材料相结合的异质结构,对未来大规模硅基集成系统的实现有着重要的潜在应用价值。然而mos2/si光电器件与硅基mosfet等传统逻辑器件的三维集成工艺鲜有报道,并且仅有的研究也多是基于平面集成,一方面增大了系统集成的面积,另一方面光电辐照也会对暴露在同一平面的硅基mosfet等器件的带来性能上的影响。

3、三维集成(3d integration)是指将电路功能模块分布在不同的芯片上,再将这些芯片进行三维堆叠实现集成。通过硅通孔(through-silicon-via,tsv)实现不同芯片层的器件之间的电学连接。然而将传统硅基衬底直接进行三维堆叠,由于硅衬底厚度过厚,不利于系统集成,同时也不利于层间tsv通孔的形成。因此需要将堆叠层的硅衬底进行减薄处理。传统临时键合+硅片减薄+机械解键合等方式极易带来晶圆损伤和应力效应,影响晶圆上的器件结构和功能。

技术实现思路

1、本发明提出了mos2/si异质结光电探测器结构,利用激光解键合技术实现了光电探测器与mosfet的三维集成,优化了pd器件的带宽与工作效率,提高了整个电路的集成度及其性能指标。具体而言:

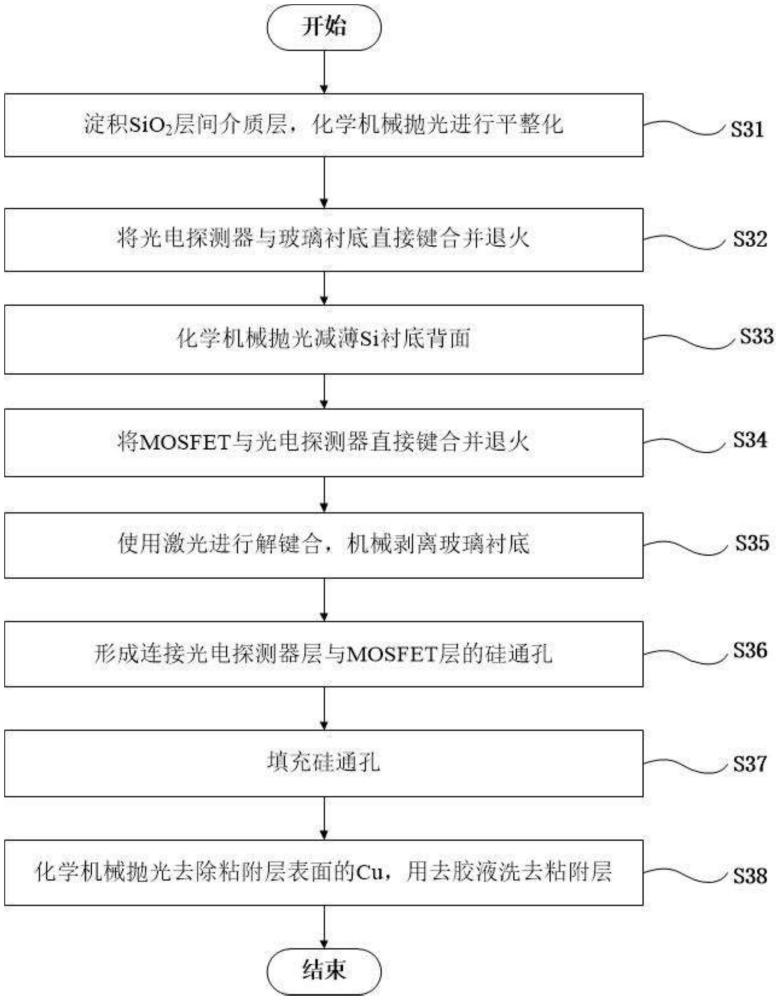

2、一种基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,包括以下步骤:在si衬底上形成mos2/si异质结光电探测器结构层;在soi晶圆上制作mosfet结构层;在mosfet结构层表面形成层间介质层;在光电探测器表面形成粘附层与激光反应层,与支撑衬底直接键合,退火形成稳定的键合对;减薄si衬底背面;将mosfet结构层与mos2/si异质结光电探测器结构层直接键合,退火形成稳定的键合对;使用激光进行解键合,激光与激光反应层烧蚀反应,机械剥离支撑衬底;形成连接光电探测器结构层与mosfet结构层的硅通孔;在硅通孔内填充cu,去除粘附层表面的cu,用去胶液洗去粘附层,完成mosfet结构层与mos2/si异质结光电探测器结构层的三维集成。

3、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,使用波长为355nm,功率小于5w,扫描速度为1500mm/s的激光进行解键合。

4、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,在250~300℃下,将mosfetmosfet结构层与mos2/si异质结光电探测器结构层直接键合,在165℃下退火8h,在115℃下退火16h。

5、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,在si衬底上形成mos2/si异质结光电探测器结构层包括以下步骤:在硅衬底上干氧氧化生长sio2薄膜;光刻定义形成异质结的区域,刻蚀去除该区域的sio2薄膜,暴露出si衬底;在两侧的sio2薄膜上形成电极;在所述异质结区域的si衬底上形成二维mos2薄膜,并延伸覆盖两侧电极的部分表面,形成mos2/si异质结光电探测器结构层。

6、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,所述sio2薄膜的厚度为100~150nm。

7、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,在soi晶圆上制作mosfet结构层,包括以下步骤:减薄抛光soi晶圆的顶层si薄膜;形成栅介质层和栅电极层,光刻、刻蚀去除两侧的栅介质层和栅电极层使顶层si薄膜露出,形成栅电极叠层;在栅电极叠层两侧形成高掺杂的源漏区域;形成源漏电极。

8、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,采用原子层沉积法淀积hfo2薄膜作为栅介质层,采用直流磁控溅射形成tin薄膜作为栅电极。

9、本发明的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法中,优选为,使用bf2以8~12kev的能量,2.5~3.5e14cm-2的剂量对源漏区域进行离子注入,形成高掺杂的源漏区域,能量及剂量决定了源漏区域的深度及载流子浓度。

10、本发明还公开一种基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成结构,根据上述基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法制备而成。

11、有益效果:

12、提出mos2/si异质结的光电探测器结构,利用二维材料mos2的性质,使其与si形成异质结,实现了各项参数更优的器件。

13、引入激光解键合技术进行pd与mosfet的三维集成,实现了含器件硅衬底的减薄转移,完成了镀铜填充si通孔对器件层之间的电学连接。

14、与si衬底集成,兼容现有si工艺流程,可行性高;热预算管理得当,工艺流程简洁。

技术特征:1.一种基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

2.根据权利要求1所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

3.根据权利要求1所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

4.根据权利要求1所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

5.根据权利要求4所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

6.根据权利要求1所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

7.根据权利要求6所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

8.根据权利要求6所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法,其特征在于,

9.一种基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成结构,根据权利要求1~8中任一项所述的基于激光解键合的mos2/si异质结光电探测器与mosfet三维集成方法制备而成。

技术总结本发明公开一种基于激光解键合的MoS<subgt;2</subgt;/Si异质结光电探测器与MOSFET三维集成方法及结构。该方法包括以下步骤:在Si衬底上形成MoS<subgt;2</subgt;/Si异质结光电探测器结构层;在SOI晶圆上制作MOSFET结构层;在MOSFET结构层表面形成层间介质层;在光电探测器表面形成粘附层与激光反应层,与支撑衬底直接键合,退火形成稳定的键合对;减薄Si衬底背面;将MOSFET结构层与MoS<subgt;2</subgt;/Si异质结光电探测器结构层直接键合,退火形成稳定的键合对;使用激光进行解键合,激光与激光反应层烧蚀反应,机械剥离支撑衬底;形成连接光电探测器结构层与MOSFET结构层的硅通孔;在硅通孔内填充Cu,去除粘附层表面的Cu,用去胶液洗去粘附层,完成MOSFET结构层与MoS<subgt;2</subgt;/Si异质结光电探测器结构层的三维集成。技术研发人员:朱颢,张天一,赵飞扬受保护的技术使用者:复旦大学技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296554.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。