时钟分布抖动减小系统和方法与流程

- 国知局

- 2024-10-21 14:26:35

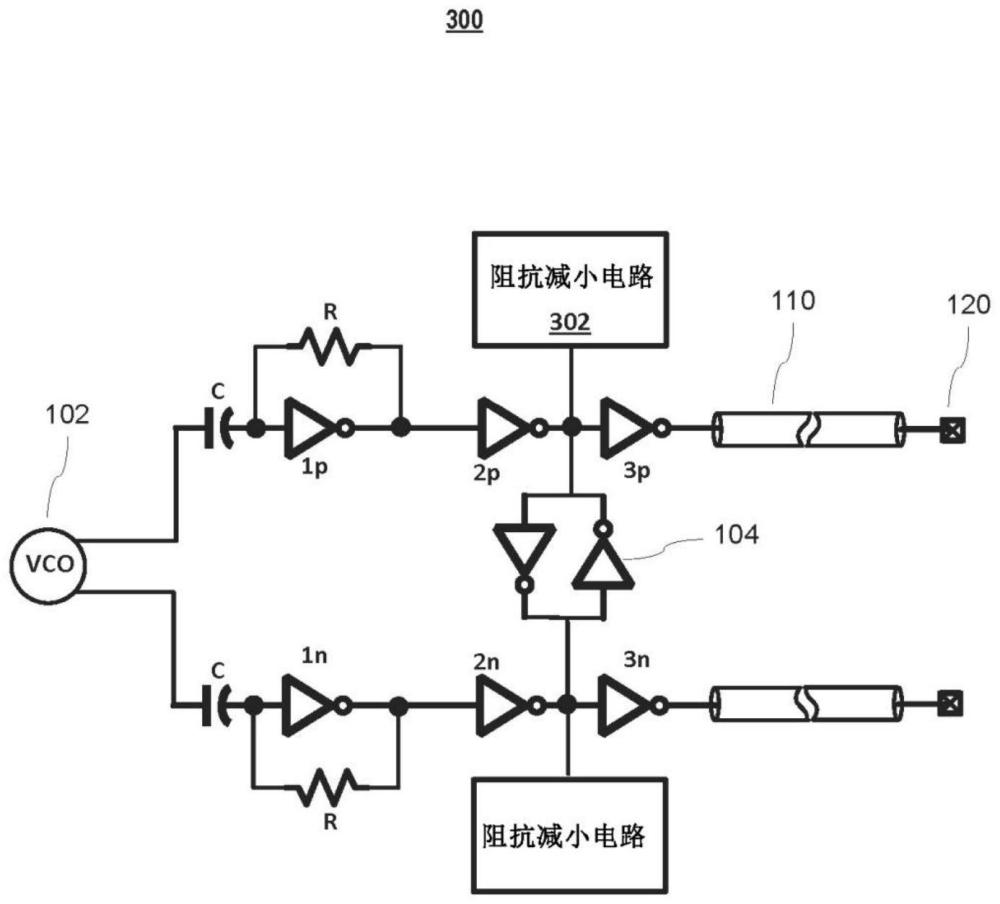

本公开一般涉及模拟或混合信号系统。更具体地,本公开涉及用于改善时钟电路和相关环境中的抖动性能的有源阻抗减小系统和方法。

背景技术:

1、抖动是时钟信号固有的已知问题,例如,由在时间交错模数(“adc”)或有线serdes接收器设计中用作定时基准的时钟电路生成的时钟信号。时钟信号通常由振荡器电路产生,例如lc振荡器或环形振荡器。还已知的是,与环形压控振荡器(“vco”)设计相比,使用低损耗振荡回路和可变电容器设计的lc-vco导致优异的抖动性能。时钟信号的抖动经常导致不希望的影响,诸如接收器中的误码率等。因而,所需要的是减少且理想地消除时钟分布电路中的时钟抖动的系统和方法。

技术实现思路

技术特征:1.一种时钟生成和分布方法,其包括:

2.根据权利要求1所述的方法,其进一步包括选择所述串联电阻器的值以及所述一组晶体管的物理或电气特性中的至少一者,以使得所述节点处的阻抗减小。

3.根据权利要求1所述的方法,其中所述时钟电路包括信号路径中的一组反相器,并且所述有源阻抗减小电路不位于所述信号路径中。

4.根据权利要求1所述的方法,其中所述一组晶体管包括在辅助时钟缓冲器中。

5.根据权利要求1所述的方法,其进一步包括使用使能信号和传输门中的至少一者来激活所述有源阻抗减小电路。

6.根据权利要求5所述的方法,其中所述传输门包括p-mos和n-mos元件。

7.根据权利要求1所述的方法,其中减小所述抖动包括减小在耦接至所述节点的反相器的输出端处的噪声。

8.一种有源阻抗减小电路,其包括:

9.根据权利要求8所述的电路,其中对于给定的频率或频率范围,所述抖动减小。

10.根据权利要求8所述的电路,其中所述激活元件包括电压源和传输门。

11.根据权利要求10所述的电路,其中所述传输门包括p-mos器件和n-mos器件中的至少一者。

12.根据权利要求8所述的电路,其中所述辅助时钟缓冲器和所述电阻元件导致所述时钟电路内的两个反相器之间的节点处的阻抗减小。

13.根据权利要求12所述的电路,其中所述辅助时钟缓冲器包括单个传输门。

14.根据权利要求13所述的电路,其中所述单个传输门导致在所述时钟电路内的两个反相器之间的节点处的阻抗减小。

15.根据权利要求12所述的电路,其中所述辅助时钟缓冲器包括多个传输门。

16.根据权利要求15所述的电路,其中所述多个传输门导致在所述时钟电路内的两个反相器之间的节点处的阻抗减小。

17.根据权利要求12所述的电路,其中所述两个反相器之间的所述节点处的所述阻抗减小由表示。

18.一种时钟电路,其包括:

19.根据权利要求18所述的时钟电路,其中所述第一多个反相器耦接至第一传输线并且所述第二多个反相器耦接至第二传输线。

20.根据权利要求19所述的时钟电路,其中第一发射焊盘耦接至所述第一传输线并且第二发射焊盘耦接至所述第二传输线。

技术总结本公开涉及时钟分布抖动减小系统和方法。本发明的实施例涉及根据本公开的各种实施例的时钟生成和分布电路(“时钟电路”)。时钟电路包括有源阻抗减小电路,所述有源阻抗减小电路通过降低时钟电路内的小信号阻抗来改善时钟电路的带宽和抖动性能。在某些实施例中,激活元件被定位在沿着传输路径的节点处以引起阻抗的减小。技术研发人员:R·纳古拉帕利,W·莱塞特苏姆布恩,刘海晨受保护的技术使用者:亚德诺半导体国际无限责任公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/318170.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。