一种缓启动功率MOS晶体管及其制备方法与流程

- 国知局

- 2024-11-06 15:06:34

本发明涉及半导体器件制造的,特别涉及一种缓启动功率mos晶体管及其制备方法。

背景技术:

1、米勒平台是在电子电路中,尤其是在功率开关管(如 mosfet、igbt 等)的开关过程中出现的一种现象。

2、在开关管导通和关断的过程中,由于开关管的栅极和漏极之间存在电容(称为米勒电容)。当开关管的状态发生变化时,对米勒电容的充电和放电过程会导致栅极电压在一段时间内保持相对稳定,从而形成米勒平台。例如,在 mosfet 的开通过程中,当栅极电压上升到一定程度后,漏极电流开始增加,漏极电压开始下降。此时,米勒电容通过栅极驱动源充电,由于米勒电容较大,充电电流主要流向米勒电容,使得栅极电压上升缓慢,出现一段相对稳定的时期,即米勒平台。

3、虽然米勒平台在高频应用来说是不利的,但是在电源缓启动中有很大的用处。mos晶体管两端漏源电压的下降区间,大部分都在米勒平台之间完成,如果人为的增加米勒电容,延长米勒平台持续时间,可以达到延长漏源电压的下降时间,也就可以利用此点,做电源的缓启动,在热拔插、独立模块供电、大功率设备上电等方法,都有益处。

4、由于米勒电容是功率mos晶体管寄生存在的,现有工艺不能对其调控,对于在电源缓启动的应用中,需要米勒平台持续时间长,现有的高性能mos晶体管如sgt、超结等由于其特点的限制,米勒电容都较小,开关速度快,难以满足要求。电路设计者需要额外增加电子元器件,增加了驱动电路的复杂度,也增加了额外的成本,更不利于系统电路的集成。

技术实现思路

1、基于此,本发明的目的是提供一种缓启动功率mos晶体管及其制备方法,旨在兼容现有先进工艺平台的基础上,可以单独对功率mos晶体管的米勒电容进行调控,并增大其米勒电容,延长米勒平台持续时间,延长开关时间。

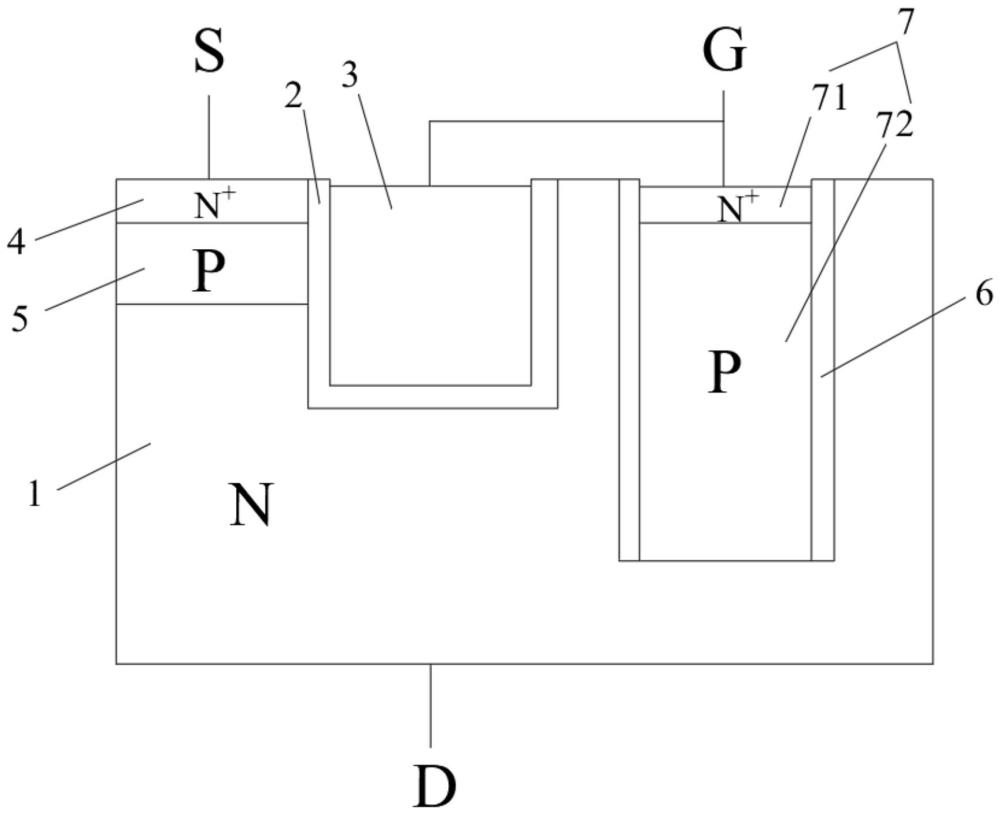

2、根据本发明实施例当中的一种mos晶体管,当mos晶体管为trench nmos晶体管时,mos晶体管包括设置于n型外延层中的第一沟槽和与所述第一沟槽间隔的第二沟槽;

3、所述第一沟槽的表面沉积有第一氧化层,所述第一氧化层形成的沟槽内填充有栅极多晶硅,所述第一沟槽远离所述第二沟槽一侧的n型外延层中,沿所述第一沟槽的深度方向上,依次设置有第一n型子层和第一p型子层,所述第一n型子层的掺杂浓度高于所述n型外延层的掺杂浓度;

4、所述第二沟槽的侧面沉积有第二氧化层,所述第二沟槽的底面部分裸露,所述第二氧化层形成的沟槽内填充有电容多晶硅,所述电容多晶硅沿所述第二沟槽的深度方向上,依次设置有第二n型子层和第二p型子层,所述第一n型子层与所述第二n型子层的掺杂浓度相同;

5、其中,所述第二沟槽的深度大于所述第一沟槽的深度;

6、当mos晶体管为trench pmos晶体管时,通过将所述trench nmos晶体管中所有掺杂反型即得。

7、进一步的,所述第一沟槽的深度为1μm~1.5μm。

8、进一步的,所述第二沟槽的深度为5μm~7μm。

9、进一步的,所述第二沟槽的宽度为2μm~6μm。

10、进一步的,所述第一氧化层和所述第二氧化层的厚度均为500å~1000å。

11、进一步的,所述第二p型子层的杂质为b,掺杂浓度为1e10 atom/cm3~1e14 atom/cm3,温度为700℃~1000℃。

12、进一步的,所述第一n型子层与所述第二n型子层的杂质为p,掺杂浓度为1e13atom/cm3~1e17atom/cm3,温度为800℃~1100℃。

13、进一步的,所述栅极多晶硅和所述电容多晶硅的表面低于对应氧化层的表面0.2μm~0.5μm。

14、根据本发明实施例当中的一种mos晶体管制备方法,用于制备上述的mos晶体管,当所述mos晶体管为trench nmos晶体管时,所述制备方法包括:

15、提供一n型外延层;

16、在所述n型外延层上刻蚀出第一沟槽和与所述第一沟槽间隔的第二沟槽,其中,所述第二沟槽的深度大于所述第一沟槽的深度;

17、在所述第一沟槽和所述第二沟槽表面沉积氧化层,以分别形成第一氧化层和第二氧化层,其中,通过对所述第二沟槽底部沉积的氧化层进行刻蚀,得到所述第二氧化层,且所述第二沟槽的底面部分裸露;

18、分别在第一氧化层和第二氧化层形成的沟槽内沉积多晶硅并进行cmp磨平回刻,以分别形成栅极多晶硅和电容多晶硅;

19、在所述电容多晶硅中以及n型外延层的预设区域中进行p型掺杂;

20、在进行p型掺杂的部分进行n型掺杂,以得到第一n型子层、第一p型子层、第二n型子层和第二p型子层,所述第一n型子层的掺杂浓度高于所述n型外延层的掺杂浓度,所述第一n型子层与所述第二n型子层的掺杂浓度相同;

21、或者,

22、当mos晶体管为trench pmos晶体管时,所述制备方法为将trench nmos晶体管中所有掺杂反型。

23、与现有技术相比:通过当mos晶体管为trench nmos晶体管时,设置于n型外延层中的第一沟槽和与第一沟槽间隔的第二沟槽;第一沟槽的表面沉积有第一氧化层,第一氧化层形成的沟槽内填充有栅极多晶硅,第一沟槽远离第二沟槽一侧的n型外延层中,沿第一沟槽的深度方向上,依次设置有第一n型子层和第一p型子层,第一n型子层的掺杂浓度高于n型外延层的掺杂浓度;第二沟槽的表面沉积有第二氧化层,第二氧化层形成的沟槽内填充有电容多晶硅,电容多晶硅沿第二沟槽的深度方向上,依次设置有第二n型子层和第二p型子层,第一n型子层与第二n型子层的掺杂浓度相同;其中,第二沟槽的深度大于第一沟槽的深度,当mos晶体管为trench pmos晶体管时,通过将trench nmos晶体管中所有掺杂反型即得,具体的,由于存在一npn结构的电容多晶硅,且pn结形成的电容与耗尽区的宽度及pn结截面积大小相关,因此可以根据需要调节第二沟槽的宽度以及第二p型子层的掺杂浓度来调节电容的大小,另外,形成的npn结构无论功率mos是开启状态还是关闭状态,npn结构都会有一个pn结处于反偏,使此处分路不会导通,不会影响mos器件的正常工作。

技术特征:1. 一种缓启动功率mos晶体管,其特征在于,当mos晶体管为trench nmos晶体管时,mos晶体管包括设置于n型外延层中的第一沟槽和与所述第一沟槽间隔的第二沟槽;

2.根据权利要求1所述的缓启动功率mos晶体管,其特征在于,所述第一沟槽的深度为1μm~1.5μm。

3.根据权利要求2所述的缓启动功率mos晶体管,其特征在于,所述第二沟槽的深度为5μm~7μm。

4.根据权利要求3所述的缓启动功率mos晶体管,其特征在于,所述第二沟槽的宽度为2μm~6μm。

5.根据权利要求4所述的缓启动功率mos晶体管,其特征在于,所述第一氧化层和所述第二氧化层的厚度均为500å~1000å。

6.根据权利要求5所述的缓启动功率mos晶体管,其特征在于,所述第二p型子层的杂质为b,掺杂浓度为1e10 atom/cm3~1e14 atom/cm3,温度为700℃~1000℃。

7.根据权利要求6所述的缓启动功率mos晶体管,其特征在于,所述第一n型子层与所述第二n型子层的杂质为p,掺杂浓度为1e13atom/cm3~1e17atom/cm3,温度为800℃~1100℃。

8.根据权利要求7所述的缓启动功率mos晶体管,其特征在于,所述栅极多晶硅和所述电容多晶硅的表面低于对应氧化层的表面0.2μm~0.5μm。

9.一种缓启动功率mos晶体管的制备方法,其特征在于,用于制备权利要求1至8中任一项所述的mos晶体管,当mos晶体管为trench nmos晶体管时,所述制备方法包括:

技术总结本发明提供一种缓启动功率MOS晶体管及其制备方法,通过设置于N型外延层中的第一沟槽和与第一沟槽间隔的第二沟槽;第一沟槽的表面沉积有第一氧化层,第一氧化层形成的沟槽内填充有栅极多晶硅,第一沟槽远离第二沟槽一侧的N型外延层中,沿第一沟槽的深度方向上,依次设置有第一N型子层和第一P型子层,第一N型子层的掺杂浓度高于N型外延层的掺杂浓度;第二沟槽的表面沉积有第二氧化层,第二氧化层形成的沟槽内填充有电容多晶硅,电容多晶硅沿第二沟槽的深度方向上,依次设置有第二N型子层和第二P型子层,第一N型子层与第二N型子层的掺杂浓度相同;其中,第二沟槽的深度大于第一沟槽的深度,以增大其米勒电容,延长米勒平台持续时间。技术研发人员:余快,杜天伦受保护的技术使用者:江西萨瑞半导体技术有限公司技术研发日:技术公布日:2024/11/4本文地址:https://www.jishuxx.com/zhuanli/20241106/325352.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。