减小板级扇出型封装芯片偏移量的凹槽型封装结构及方法

- 国知局

- 2024-11-21 11:33:34

本发明涉及半导体芯片封装,特别涉及一种利用混合键合技术制备晶圆级系统级封装的结构及方法。

背景技术:

1、混合键合(hybrid bonding)技术是指待键合的两片晶圆(或芯片)除了在室温下凹陷下去的铜bump完成键合,两片晶圆(或芯片)面对面的其它非导电部分也要贴合。完成hybrid bonding工艺后,在晶圆与晶圆(或芯片与芯片)之间是没有空隙的,不需要用环氧树脂进行填充。hybrid bonding工艺流程图如图1所示。图1混合键合流程图:(a)试片未接合面貌,(b)介电材料接合步骤,(c)提高温度铜接点接合过程,(d)高温时接点内部应力分布状态。

2、图像传感器芯片(cmos inage sensor,cis)是一种基于半导体cmos工艺的图像传感器,于上世纪90年底中期开始广泛商用。当前,cis芯片已广泛使用于手机、相机、汽车电子、安防等多个领域使用。随着手机、电脑、数码相机等移动消费型电子产品对高性能、低功耗、小型化、异质工艺集成、低成本的系统集成电子产品的封装的要求程度越来越高,高密度、多种类芯片系统级封装产品逐渐在新一代电子产品上成为主流。因此如何将cis芯片与其他种类芯片集成在一起形成系统集成电子产品一直是芯片封装领域研究的热点技术。

技术实现思路

1、为解决上述技术问题,本发明的目的在于提供一种利用混合键合技术制备晶圆级系统级封装的结构及方法。该封装结构及方法可以实现cis芯片与其他种类芯片晶圆级封装,在实现不同种类芯片集成的同时,能极大的提高封装效率,显著降低加工成本。

2、根据本发明的一方面,本发明提供一种利用混合键合技术制备晶圆级系统级封装的方法,通过以下技术方案实现,包括如下步骤:

3、s1,对晶圆级cis芯片表面进行清洁处理;

4、s2,在晶圆级cis芯片正面形成粘贴膜层和玻璃层;

5、s3,对晶圆级cis芯片背面进行减薄处理并形成非键合层;

6、s4,在晶圆级cis芯片背面形成导电通孔结构;

7、s5,在晶圆级cis芯片背面形成导电结构;

8、s6,对第二类晶圆级芯片正面进行清洁处理并粘贴保护膜层;

9、s7,对第二类晶圆级芯片背面进行减薄处理并形成非键合层;

10、s8,在第二类晶圆级芯片背面形成导电通孔结构;

11、s9,在第二类晶圆级芯片背面形成导电结构;

12、s10,将晶圆级cis芯片和第二类晶圆级芯片键合在一起;

13、s11,拆除第二类晶圆级芯片正面保护膜层;

14、s12,在键合后晶圆上形成第一层绝缘层;

15、s13,在键合后晶圆上形成第一层金属重布线层;

16、s14,在键合后晶圆上形成第二层绝缘层;

17、s15,在键合后晶圆上形成第二层金属重布线层(即焊盘);

18、s16,在键合后晶圆第二层金属重布线层上植球;

19、s17,切割得到单颗die。

20、进一步,其中s12和s14步骤中所述绝缘层的材料为环氧树脂、氧化硅绝缘材料或其他绝缘材料;在本实施例中,该绝缘层材料为感光性环氧树脂。

21、进一步,s13和s15步骤中所述金属重布线层的材料为铝、铜、金、铂、镍、锡中的一种或两种及以上的组合,在本实施例中,该绝缘层金属重布线层材料为铜。

22、本发明提供了一种利用混合键合技术制备晶圆级系统级封装的结构及方法,其是利用hybrid bonding技术将cis芯片与其他种类芯片集成在一起并完成整个封装工艺流程。

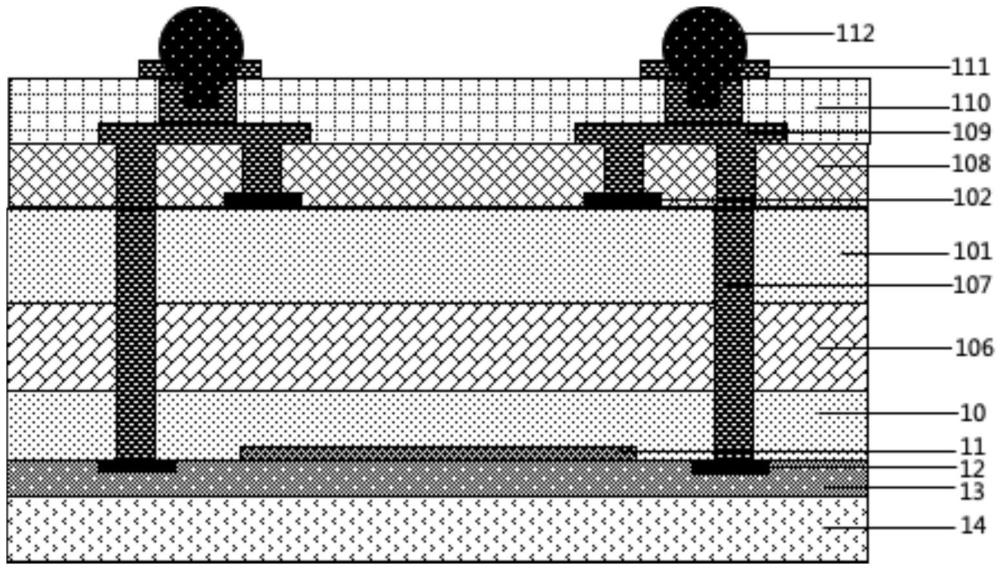

23、根据本发明的另一方面,本发明提供一种减小板级扇出型封装芯片偏移量的凹槽型封装结构,由所述方法制作,包括晶圆级cis芯片和第二类晶圆级芯片,利用hybridbonding技术将晶圆级cis芯片和第二类晶圆级芯片集成在一起。

24、进一步,所述晶圆级cis芯片包括cis芯片上表面和cis芯片下表面,cis芯片上表面设有感光区和导电结构;

25、所述cis芯片上表面依次设有具有高透光特性的粘贴膜层和玻璃层;

26、所述晶圆级cis芯片背面进行减薄,并形成hybrid bonding技术中的非导电层;

27、所述非导电层上与晶圆级cis芯片导电结构对应位置处设置导电结构通孔;

28、所述导电通孔结构处设有导电结构。

29、进一步,所述第二类晶圆级芯片包括芯片上表面和芯片下表面,芯片上表面设有芯片导电结构;

30、所述第二类晶圆级芯片上表面上粘贴保护膜层;

31、所述第二类晶圆级芯片背面进行减薄,并形成hybrid bonding技术中的非导电层;

32、所述非导电层与第二类晶圆级芯片导电结构对应位置处形成导电结构通孔,所述导电结构通孔贯穿非导电层和第二类晶圆级芯片;所述晶圆级芯片上形成的导电结构通孔所处位置与芯片导电结构所处位置错开;

33、所述结构导电通孔结构处形成导电结构。

34、进一步,具有导电结构的晶圆级cis芯片与具有导电结构的第二类晶圆级芯片通过hybrid bonding技术键合形成键合结构,所述键合结构包括两片晶圆键合后形成的非导电层和两片晶圆键合后形成的导电结构;

35、拆除所述键合结构经两片晶圆键合后得到的晶圆上表面膜层,并形成第一层绝缘层和导电通孔结构;

36、所述晶圆级结构上设置第一层金属重布线层;

37、所述第一层金属重布线层上设置第二层绝缘层和导电通孔结构;

38、所述第二层绝缘层和导电通孔结构上设置第二层金属重布线层;

39、所述第二层金属重布线层上完成植球,植球为锡球结构。

40、进一步,将完成植球的晶圆芯片进行切割,获得单颗cis芯片与其他种类芯片集成在一起的结构。

41、本发明的有益效果主要有以下三点:(1)利用hybrid bonding键合技术进行键合,该技术能够实现更高密度触点连接(在1×1cm的芯片内,能够制作出超过一百万的触点)和更小接点间距连接(间距可以微缩到1微米以下)。(2)将cis芯片与其他种类芯片集成,实现高性能、低功耗、小型化、异质工艺集成、低成本的系统集成电子产品的制备。(3)整个封装流程为晶圆级封装,封装效率高、成本低、产能大。

技术特征:1.一种利用混合键合技术制备晶圆级系统级封装的方法,其特征在于:包括如下步骤:

2.根据权利要求1所述的方法,其特征在于:其中s12和s14步骤中所述绝缘层的材料为环氧树脂、氧化硅绝缘材料或其他绝缘材料。

3.根据权利要求1所述的方法,其特征在于:s13和s15步骤中所述金属重布线层的材料为铝、铜、金、铂、镍、锡中的一种或两种及以上的组合。

4.根据权利要求1所述的方法,其特征在于:利用hybrid bonding技术将cis芯片与第二类晶圆级芯片集成在一起并完成整个封装工艺流程。

5.一种减小板级扇出型封装芯片偏移量的凹槽型封装结构,其特征在于:由权利要求1至4任一项所述方法制作,包括晶圆级cis芯片和第二类晶圆级芯片,利用hybrid bonding技术将晶圆级cis芯片和第二类晶圆级芯片集成在一起。

6.根据权利要求5所述的封装结构,其特征在于:所述晶圆级cis芯片包括cis芯片上表面和cis芯片下表面,cis芯片上表面设有感光区和导电结构;

7.根据权利要求5所述的封装结构,其特征在于:所述第二类晶圆级芯片包括芯片上表面和芯片下表面,芯片上表面设有芯片导电结构;

8.根据权利要求6或7所述的封装结构,其特征在于:具有导电结构的晶圆级cis芯片与具有导电结构的第二类晶圆级芯片通过hybrid bonding技术键合形成键合结构,所述键合结构包括两片晶圆键合后形成的非导电层和两片晶圆键合后形成的导电结构;

9.根据权利要求8所述的封装结构,其特征在于:将完成植球的晶圆芯片进行切割,获得单颗cis芯片与其他种类芯片集成在一起的结构。

技术总结一种利用混合键合技术制备晶圆级系统级封装的结构及方法。该封装结构及方法可以实现CIS芯片与其他种类芯片晶圆级封装。(1)利用Hybrid Bonding键合技术进行键合,该技术能够实现更高密度触点连接(在1×1cm的芯片内,能够制作出超过一百万的触点)和更小接点间距连接(间距可以微缩到1微米以下)。(2)将CIS芯片与其他种类芯片集成,实现高性能、低功耗、小型化、异质工艺集成、低成本的系统集成电子产品的制备。(3)整个封装流程为晶圆级封装,封装效率高、成本低、产能大。技术研发人员:刘吉康,李莎,李杰,刘秀峰,蔡新添,王怀兴,王筠,马晓萌,万振武受保护的技术使用者:湖北第二师范学院技术研发日:技术公布日:2024/11/18本文地址:https://www.jishuxx.com/zhuanli/20241120/331773.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表