IPD电容制作方法和滤波器与流程

- 国知局

- 2024-11-21 11:35:44

本发明涉及硅基器件制造领域,尤其涉及一种ipd电容制作方法和滤波器。

背景技术:

1、ipd电容即集成无源器件(integrated passive devices)电容,它采用硅材料作为绝缘体,并利用半导体技术进行制造。相比传统电容器ipd电容在高频应用中表现出色,能满足电子设备对更高频率、更小尺寸和更高性能的需求。ipd电容被广泛的应用于射频和模拟/混合电路芯片中,例如振荡、滤波、去耦、开关等场景,在许多场景都需要使用小容值的电容。

2、目前,针对小容值电容的实现传统方法主要依赖于平面电容器结构设计。平面电容的电值与电极面积呈正比关系,故当需要设计小容值电容时,必须大幅度减小电极面积,这在微电子制造工艺中带来了显著困难。由于面积缩小至微米甚至纳米级别,对工艺精度要求极高,实际生产中易受到工艺公差的影响,使得此类微小平面电容的制作变得尤为复杂且不稳定。此外,增大平面电容介质层垂直方向的厚度来降低电容值也是一种常规办法,但这同样存在明显的技术瓶颈。过厚的介质层不仅加工难度大增,而且可能造成加工过程中的工艺不可行性,同时还会引入额外的介质损耗以及影响器件的长期稳定性,不利于满足高频ipd滤波器的小型化、高性能需求。

技术实现思路

1、本发明提供一种ipd电容制作方法和滤波器,用以解决现有技术中ipd电容加工难度高、工艺复杂以及难以高效集成的问题,在制作过程中将电容由原来的平面结构改为垂直结构,使得电容的介质层在水平方向可以近乎无限,从而在工艺上轻松实现小容值电容的设计与制造。

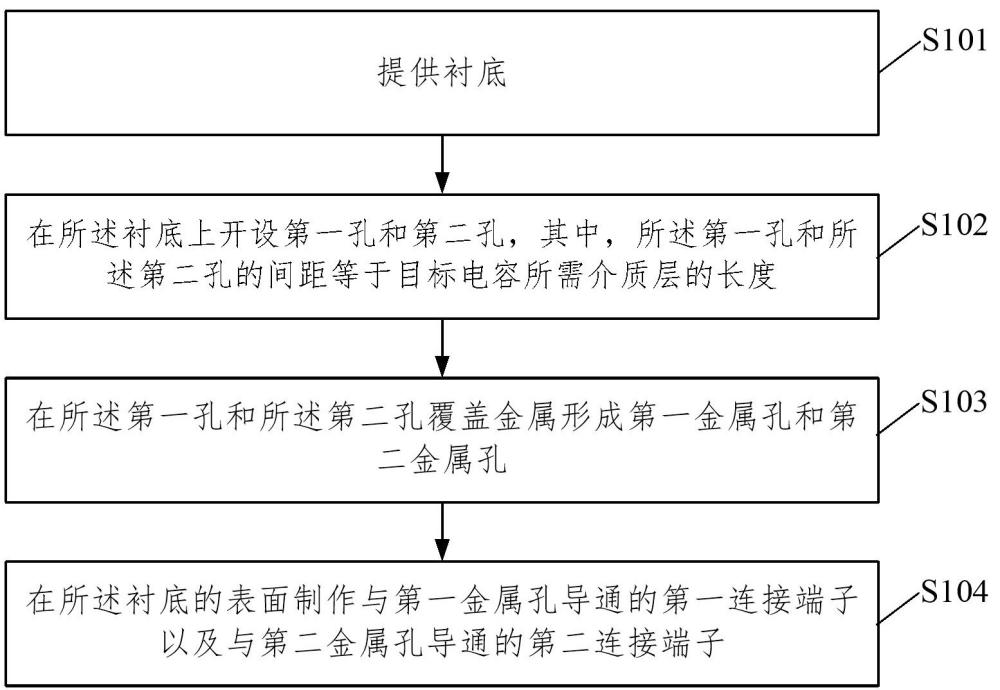

2、根据本发明的第一方面,本发明提供了一种ipd电容制作方法,所述方法包括:

3、提供衬底;

4、在所述衬底上开设第一孔和第二孔,其中,所述第一孔和所述第二孔的间距等于目标电容所需介质层的长度;

5、在所述第一孔和所述第二孔覆盖金属形成第一金属孔和第二金属孔;

6、在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子;

7、其中,位于所述第一金属孔与所述第二金属之间的衬底为目标电容的介质层,所述第一金属孔和所述第二金属孔相对面为目标电容的电极,所述第一连接端子和所述第二连接端子为目标电容的连接端子。

8、根据本发明的ipd电容制作方法,在所述衬底上开设第一孔和第二孔,包括:

9、制作第一掩模版,其中,所述第一掩模版上设置有第一标记和第二标记,所述第一标记和所述第二标记用于分别标识两个电极的相对位置,所述第一标记和第二标记的距离等于目标电容所需介质层的长度;

10、利用光刻工艺将所述第一掩模版的图形转移至所述衬底的表面,以使衬底的表面除所述第一标记和第二标记对应位置以外均覆盖光刻胶;

11、利用硅通孔工艺在未覆盖光刻胶的区域开孔形成所述第一孔和所述第二孔;

12、将覆盖在所述衬底上的光刻胶去除。

13、根据本发明的ipd电容制作方法,在所述第一孔和所述第二孔覆盖金属形成第一金属孔和第二金属孔,包括:

14、利用物理气相沉积工艺对带有第一孔和第二孔的衬底进行种子层溅射;

15、将所述第一孔上形成的种子层作为第一金属孔,将所述第二孔上形成的种子层作为第二金属孔,将所述衬底的表面上形成的种子层作为表面种子层。

16、根据本发明的ipd电容制作方法,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子,包括:

17、制作第二掩模版,其中,所述第二掩模版上设置有与所述第一孔有重叠的第三标记、以及与所述第二孔有重叠的第四标记,所述第三标记和所述第四标记用于分别标识两个连接端子的宽度及相对位置;

18、利用光刻工艺将所述第二掩模版的图形转移至所述衬底的表面,以使衬底的表面除所述第三标记和第四标记对应位置以外均覆盖光刻胶;

19、利用电镀工艺在未覆盖光刻胶的区域镀金属层;

20、在电镀完后将覆盖在所述衬底上的光刻胶去除;

21、将与所述第一金属孔连通的金属层作为所述第一连接端子,将与所述第二金属孔连通的金属层作为所述第二连接端子。

22、根据本发明的ipd电容制作方法,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子的步骤之前,所述方法还包括:使用金属填充所述第一金属孔和所述第二金属孔。

23、根据本发明的ipd电容制作方法,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子的步骤之后,所述方法还包括:将所述表面种子层裸露在外区域去除。

24、根据本发明的ipd电容制作方法,提供衬底的步骤包括:

25、将晶圆作为初始衬底;

26、利用热氧化工艺、化学气相沉积工艺、等离子体增强化学气相沉积中的任意一种在所述初始衬底上覆盖氧化层,形成所述衬底。

27、根据本发明的ipd电容制作方法,所述第一孔和所述第二孔均为盲孔或均为通孔。

28、根据本发明的ipd电容制作方法,所述第一连接端子和所述第二连接端子均朝向远离所述目标电容的介质层的方向延伸。

29、根据本发明的第二方面,本发明还提供了一种滤波器,所述滤波器包括电容和电感,所述电容采用以上所述ipd电容制作方法制得。

30、本发明提供的一种ipd电容制作方法,通过在衬底上开设第一孔和第二孔,并将第一孔和第二孔的距离设置为与目标电容所需介质层的长度,接着在第一孔和第二孔上覆盖金属形成金属孔,最后在衬底表面制作与金属孔连通的两个连接端子,从而制得ipd电容,突破了传统平面电容的限制,巧妙利用衬底及三维堆叠技术手段,使得电容介质层的厚度可以从水平方向获得近乎无限的调整空间,有助于缩小小容值电容体积,工艺简单且成本较低,使得ipd电容的制作方法更加丰富。

31、此外,本发明提供的一种滤波器,同样能实现上述技术效果,这里不再赘述。

技术特征:1.一种ipd电容制作方法,其特征在于,所述方法包括:

2.根据权利要求1所述的ipd电容制作方法,其特征在于,在所述衬底上开设第一孔和第二孔,包括:

3.根据权利要求1所述的ipd电容制作方法,其特征在于,在所述第一孔和所述第二孔覆盖金属形成第一金属孔和第二金属孔,包括:

4.根据权利要求1所述的ipd电容制作方法,其特征在于,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子,包括:

5.根据权利要求1所述的ipd电容制作方法,其特征在于,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子的步骤之前,所述方法还包括:使用金属填充所述第一金属孔和所述第二金属孔。

6.根据权利要求3所述的ipd电容制作方法,其特征在于,在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子的步骤之后,所述方法还包括:将所述表面种子层裸露在外区域去除。

7.根据权利要求1所述的ipd电容制作方法,其特征在于,提供衬底的步骤包括:

8.根据权利要求1所述的ipd电容制作方法,其特征在于,所述第一孔和所述第二孔均为盲孔或均为通孔。

9.根据权利要求1所述的ipd电容制作方法,其特征在于,所述第一连接端子和所述第二连接端子均朝向远离所述目标电容的介质层的方向延伸。

10.一种滤波器,其特征在于,所述滤波器包括电容和电感,所述电容采用权利要求1-9任意一项所述ipd电容制作方法制得。

技术总结本发明提供一种IPD电容制作方法和滤波器,涉及硅基器件制造领域。该方法包括:提供衬底;在所述衬底上开设第一孔和第二孔,所述第一孔和所述第二孔的间距等于目标电容所需介质层的长度;在所述第一孔和所述第二孔覆盖金属形成第一金属孔和第二金属孔;在所述衬底的表面制作与第一金属孔导通的第一连接端子以及与第二金属孔导通的第二连接端子;位于所述第一金属孔与所述第二金属之间的衬底为目标电容的介质层,所述第一金属孔和所述第二金属孔相对面为目标电容的电极,所述第一连接端子和所述第二连接端子为目标电容的连接端子。本发明方案有助于缩小小容值电容体积,工艺简单且成本较低,使得IPD电容的制作方法更加丰富。技术研发人员:高顺良,欧毅,张永斌,张浩,孙学艳,张智鹏,李雨航,吴沛,项超受保护的技术使用者:北京晨晶电子有限公司技术研发日:技术公布日:2024/11/18本文地址:https://www.jishuxx.com/zhuanli/20241120/331898.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表