一种氮化镓沟槽型MOSFET器件及其制备方法

- 国知局

- 2024-11-21 12:28:58

本发明涉及一种氮化镓沟槽型mosfet器件及其制备方法,属于半导体器件。

背景技术:

1、功率半导体晶体管是电力电子系统的核心,在消费电子、轨道交通、光伏发电和工业控制等多个领域广泛应用。其承担着变频、整流、变压、功率放大和功率管理等众多功能。相较于第一代半导体硅(si),第三代半导体氮化镓(gan)因其具有更大的禁带宽度、更高的临界击穿场强以及更快的饱和漂移速度等优势而备受瞩目。因此,gan基功率晶体管可以突破传统si基功率晶体管的发展瓶颈,进一步满足下一代功率电子系统的需求。

2、得益于位于algan/gan界面高迁移率的二维电子气(2deg),基于algan/gan异质结构的水平型功率器件获得了优异的性能,工作电压达650v的si衬底gan基横向高电子迁移率晶体管(hemt)已经成功商用化。然而对于高电压、大电流场景下的应用,垂直构型仍是最优选。对于水平型功率晶体管,如要实现更高的电压等级,则需要更大的源漏间距,这会增加芯片的尺寸并导致更高的产品成本。同时水平型功率晶体管的寄生元件和引脚与栅极到漏极的间距成正比,通过增加源漏间距的方式实现高耐压的器件会增加寄生效应,劣化器件的开关速度。

3、与gan基水平型功率晶体管相比,gan垂直型功率晶体管可以通过增加漂移区的厚度来实现更高的击穿电压,而不会增加芯片的封装尺寸。此外,gan垂直型功率晶体管的源极和漏极分别位于晶圆的两侧,有助于实现电流的均匀分布和更高的电流水平。目前垂直型gan功率晶体管主要有沟槽型mosfets(t-mosfets)、电流孔垂直电子晶体管(cavets)、结型fets(jfets)和鳍式功率场效应晶体管(finfets)。与其他主要的垂直型gan功率晶体管相比,t-mosfets的阈值电压为3-5伏,在保证器件实现常关模式的同时可避免输入信号的噪声导致的器件误开启,且其具有相对简单的制造工艺,故被广泛研究,然而传统t-mosfets存在诸多不足。

4、传统t-mosfets存在的一个问题是电流在漂移区的延展性不佳。传统t-mosfets的电流通过栅极对p型层的反型控制,当栅极电压为零时,p型层阻断了电流通路;随着栅极电压的增大,靠近栅极的p型层开始反型,形成电流通道,器件开启。电流在反型层被限制在一个薄层当中,当电流越过反型层进入漂移区后不能有效地横向扩展,这就导致了电流在漂移区分布不均并最终导致了较大的导通电阻。而gan功率晶体管应用在电路系统中,通常需要反向续流通路,传统的t-mosfets可通过channeldiode和内嵌的体二极管实现三象限续流能力,避免了外接反并联的续流二极管带来的额外的功率损耗、封装体积以及寄生效应和电路振铃等问题。但若漏极偏压过大,内嵌二极管开启,二极管的双极性电流会导致反向恢复性能劣化,器件的开关损耗增大。同时,传统t-mosfets存在的另一个问题是沟槽底部容易出现电场聚集,限制了器件击穿电压的进一步提升。

技术实现思路

1、针对现有技术的不足,本发明提供了一种氮化镓沟槽型mosfet器件及其制备方法。

2、本发明的技术方案如下:

3、一种氮化镓沟槽型mosfet器件,是在垂直型氮化镓mosfet器件或准垂直型氮化镓mosfet器件的n-gan漂移层与p-gan层之间设置有极化层,极化层的材料可选择algan、aln、ingan、inaln或alingan;在完成栅极、源极区域刻蚀后继续生长一层再生长氮化镓层。

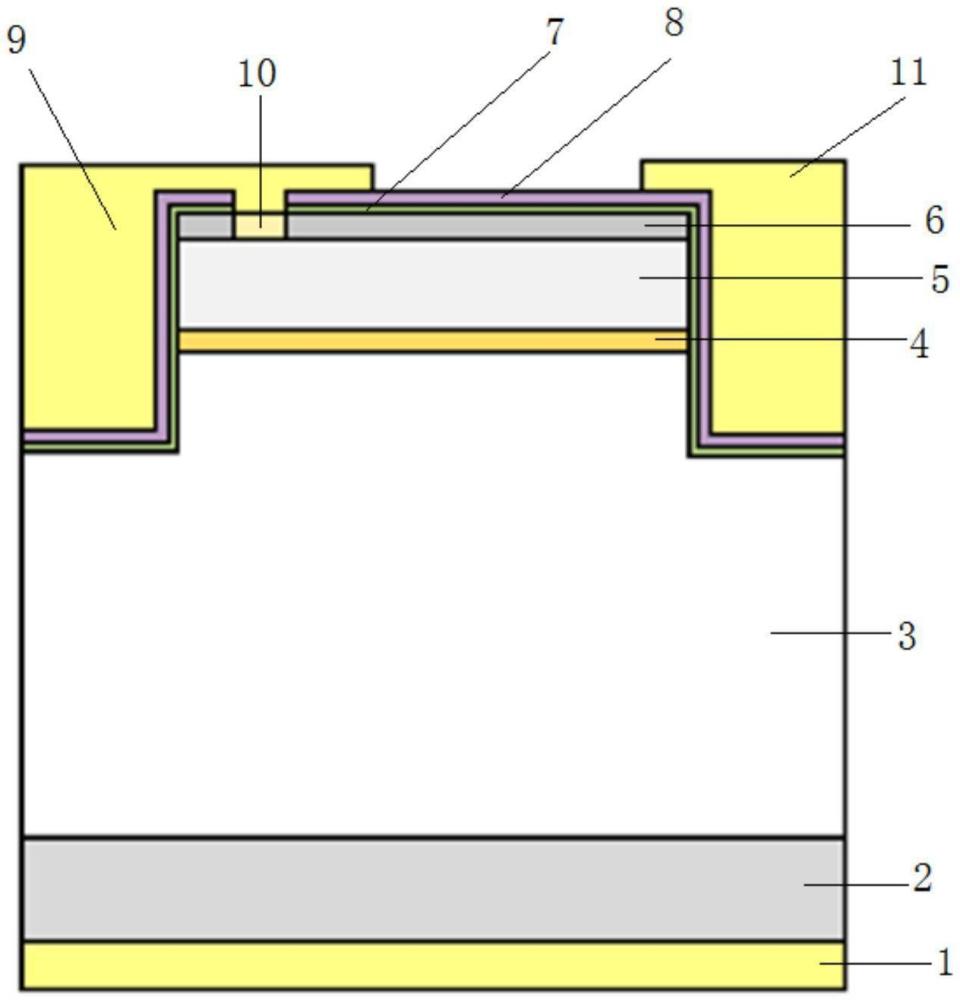

4、根据本发明优选的,所述垂直型氮化镓mosfet器件的外延结构由下至上依次包括衬底、n-gan漂移层、极化层、p-gan层和n+-gan层;所述衬底下方设置有漏极金属层。

5、根据本发明优选的,所述准垂直型氮化镓mosfet器件由下至上依次包括衬底、n-gan漂移层、极化层、p-gan层和n+-gan层;所述衬底上方,n-gan漂移区两侧设置漏极金属层。

6、根据本发明优选的,p-gan层上设置有沟槽,在沟槽的底面设置有体电极。

7、根据本发明优选的,n-gan漂移层的厚度为5~25μm;优选为13.97μm。

8、根据本发明优选的,极化层的厚度为5~100nm;优选为30nm。

9、根据本发明优选的,p-gan层的厚度为0.5~2μm;优选为0.7μm。

10、根据本发明优选的,n+-gan层的厚度为0.1~0.3μm;优选为0.2μm。

11、根据本发明优选的,再生长氮化镓层的厚度为5~50nm;优选为15nm。

12、根据本发明优选的,栅极金属层下方的sio2层(右侧)的厚度为50~100nm;优选为80nm。

13、根据本发明优选的,源极金属层下方的sio2层(左侧)的厚度为50nm~3μm;优选为2μm。

14、上述垂直型氮化镓沟槽型mosfet器件的制备方法,包括步骤如下:

15、(a)生长外延结构,在衬底上依次生长n-gan漂移层、极化层、p-gan层和n+-gan层;

16、(b)利用sio2做硬质掩膜进行icp(cl2/bcl3/ar)沟槽刻蚀,在外延结构两侧分别刻蚀出源极区域和漏极区域;

17、(c)通过mocvd沉积法,在步骤(b)刻蚀后外延结构的表面继续生长一层再生长氮化镓层;

18、(d)通过pecvd法,在再生长氮化镓层上沉积sio2层;其中,sio2层的厚度为80nm~2μm;

19、(e)利用光刻胶保护源极区域的sio2层,并利用缓冲氧化物刻蚀液(boe)对其他区域的sio2层进行刻蚀,至sio2层的厚度与栅极区域的sio2层保持一致,若要采用厚度相等的sio2层,则无需进行此步骤;

20、(f)利用光刻胶为掩膜进行icp(cl2/bcl3/ar)沟槽刻蚀,在p-gan层上方刻蚀出沟槽;

21、(g)利用电子束蒸镀法,在沟槽底部蒸镀体电极,体电极与p-gan层厚度相同,形成欧姆接触;

22、(h)利用电子束蒸镀法,在n+-gan衬底下方蒸镀栅极金属层,在源极区域和漏极区域分别蒸镀源极金属层和漏极金属层,得到垂直型氮化镓沟槽型mosfet器件。

23、根据本发明优选的,步骤(b)中,所述源极区域的深度为2~8μm,宽度为2~10μm;所述栅极区域的深度为2~8μm,宽度为2~10μm。

24、本发明中未详尽之处均可参照现有技术。

25、本发明的技术特点如下:

26、本发明为解决传统t-mosfet器件p型层下方电流拥挤的问题,在n-gan漂移层与p-gan层之间引入极化层,极化层与n-gan漂移层在c面的极化效应产生的2deg会极大程度的促进电流在水平面的延展,避免电流聚集,降低器件的导通电阻。同时极化层与n-gan漂移层之间由于极化,会形成势垒,该势垒的存在可抑制体二极管的开启,使得反向电流为单极性电流,提升器件的反向恢复性能,减小了开关损耗。

27、但极化也会在极化层与n-gan漂移层的界面处形成势垒,使得电流难以通过,为使得电流可凭借二维电子气延展的同时避免其被势垒阻挡,因此在沟槽刻蚀完成后再生长一层氮化镓,再生长氮化镓层的存在可使得电流可以顺利通过极化界面。

28、针对传统t-mosfet沟槽底部电场聚集导致器件耐压能力受限的问题,本发明在保证工艺兼容的同时,本发明在源极区域处预留场板结构空间,通过调整场板的深度以及厚度,缓解沟槽底部的电场,提升器件的耐压能力。

29、本发明的有益效果如下:

30、1、本发明在n-gan漂移层与p-gan层之间引入了极化层,n-gan漂移层与极化层在c面的极化效应产生的2deg会极大程度的促进电流在水平面的延展,避免电流在反型层下方聚集,有效利用漂移区,降低导通损耗;同时,其产生的势垒可抑制反向续流时体二极管的开启,降低了开关损耗。

31、2、本发明在刻蚀完源极、栅极沟槽后再生长了一层氮化镓,再生长氮化镓层的存在,避免了极化产生的势垒将整个电流通道封闭,使得电流可凭借二维电子气延展的同时避免其被势垒阻挡,使器件的阈值电压无法调控。

32、3、本发明提供的氮化镓沟槽型mosfet器件在实现更好的第一象限导通特性下,能够同时实现出色的三象限续流能力,并有更大击穿电压的设计潜力。同时由于没有空穴参与导电,器件的反向恢复电荷和反向恢复峰值电流可被有效抑制,减小了器件的三象限开关损耗。因此,本发明引入极化层与再生长氮化镓层后的新颖器件结构,将在现代电力系统的高频、高功率密度和低功耗应用领域中发挥巨大潜力。

33、4、本发明进一步优化了制备方法,在沉积氧化层sio2层时先生长一层厚的sio2层,再将栅极处的氧化层湿法刻蚀变薄,通过氧化层工艺兼容场板设计有效缓解了沟槽底部的电场聚集现象,提升了器件的击穿电压。优化后的制备方法步骤简单,与传统t-mosfet器件的制备工艺兼容,将难度与复杂度控制在相对可控的范围内。

本文地址:https://www.jishuxx.com/zhuanli/20241120/335458.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表