1.本发明涉及领域,尤其涉及一种电压调节装置及采用其的存储器。

背景技术:

2.在3d nand存储器中,存储单元(cell)的信息是以阈值电压(vth)的形式储存在存储单元中。读取存储信息的过程就是判断阈值电压(vth)的过程。在此过程中,首先对位线(bl,bit line)进行上拉,然后打开字线(wl,word line),对选中字线(select wl)施加读取电压(vrd),非选中字线(unselect wl)施加导通电压(vpass),并将公共源极端(acs,common source/100common source)拉到接地(gnd),以此形成一个电流路径,来对位线进行放电。

3.此时,烧录过的存储单元的阈值电压较高,对应的栅源电压(vgs)与阈值电压(vth)之差较低,放电速度慢;而没有烧录过的存储单元的阈值电压低,对应的栅源电压(vgs)与阈值电压(vth)之差较高,放电速度快。经过一个放电时间之后,对位线电压进行判断,基于位线电压是否低于参考电压来判断存储单元存储的信息是“0”还是“1”。在此过程中,放电电流的大小取决于栅源电压(vgs)与阈值电压(vth)之差。因此,放电电流既与栅电压和阈值电压有关,也与源极电压(即acs)相关。

4.现有技术中,在读取时,公共源极端通过一个开关管接到接地端。随着芯片存储容量和面积的增大,由于芯片的接地端网络强度的限制,当流过读取电流时,芯片不同位置的接地端电压可能不同,同一个位置、不同时间的接地端电压也可能不同。而接地端电压直接体现在栅源电压(vgs)上,因此,接地端电压会对读取的精度产生影响。

5.在tlc(trinary

‑

level cell)/qlc(quad

‑

level cell)的3d nand中,一个存储单元的阈值电压被分成了若干个区间,以此来尽可能存储更多的信息。例如,在tlc的3d nand中,一个存储单元的阈值电压被分为8区间,每个区间存储3bit信息,在qlc的3d nand中,一个存储单元的阈值电压被分为16个区间,每个区间存储4bit信息,于是对阈值电压(vth)判断的精度要求就越来越高,对接地端电压的稳定性、一致性也提出了更高的要求。

技术实现要素:

6.本发明所要解决的技术问题是,提供一种电压调节装置及采用其的存储器。

7.为了解决上述问题,本发明提供了一种电压调节装置,用于调节预设采样点处的电压,其包括:运算放大器,包括反相输入端、同相输入端及输出端,所述反相输入端输入一参考电压,所述同相输入端与所述预设采样点电连接,用于输入所述预设采样点的电压,形成反馈环路;上拉晶体管,包括控制端、第一端及第二端,所述控制端与所述运算放大器的所述输出端电连接,所述第一端与电源电连接,所述第二端与所述预设采样点电连接;下拉晶体管,包括控制端、第一端及第二端,所述控制端与所述运算放大器的所述输出端电连接,所述第一端与接地端电连接,所述第二端与所述预设采样点电连接。

8.进一步,所述上拉晶体管为pmos管,所述下拉晶体管为nmos管。

9.进一步,所述下拉晶体管的下拉能力大于所述上拉晶体管的上拉能力。

10.进一步,在上拉或者轻载时,所述电压调节装置工作于甲乙类模式下,在重载时,所述电压调节装置的工作在甲类模式下。

11.进一步,所述上拉晶体管与所述下拉晶体管为低压晶体管。

12.进一步,所述电压调节装置还包括开关管,所述上拉晶体管的第二端及所述下拉晶体管的第二端与所述开关管连接。

13.进一步,所述预设采样点设置在所述上拉晶体管的第二端及所述下拉晶体管的第二端与所述开关管连接的路径上,或者所述上拉晶体管的第二端及所述下拉晶体管的第二端通过所述开关管与所述预设采样点电连接。

14.进一步,所述开关管为高压晶体管。

15.进一步,所述电压调节装置还包括电平转换器,所述电平转换器与所述开关管电连接,用于将电压信号进行电平转换后作为所述开关管的控制信号。

16.本发明还提供一种存储器,其包括:存储阵列,具有公共源极端;如上所述的电压调节装置,与所述公共源极端电连接,用于将所述公共源极端连接至接地端,所述预设采样点设置在所述公共源极端与所述电压调节装置的连接路径上或者设置在所述公共源极端与所述存储阵列的连接路径上。

17.本发明的一个优点在于,电压调节装置能够根据预设采样点的反馈而调节预设采样点处的电压,使其保持稳定,提高预设采样点的电压稳定性及一致性。

18.本发明的另一优点在于,本发明存储器能够通过所述电压调节装置钳位所述预设采样点的电压,使得其维持稳定,从而使得所述存储阵列的公共源极端电压维持稳定,提高公共源极端电压稳定性及一致性,进而提高存储器的读取精度。

附图说明

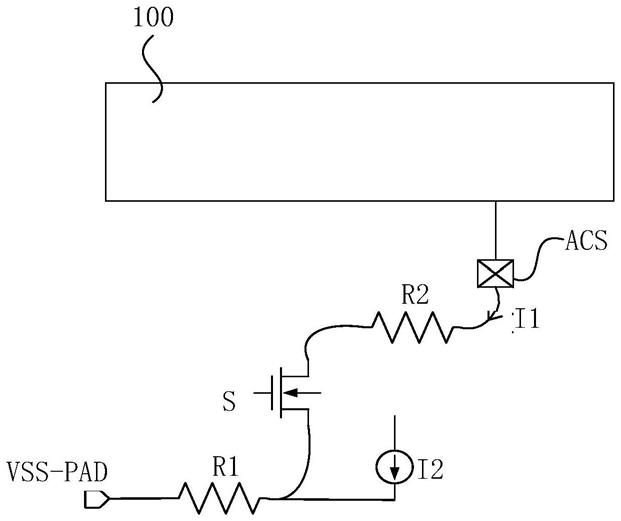

19.图1是现有技术中存储器的公共源极端接地电路示意图;

20.图2是本发明第一实施例的电压调节装置的电路示意图;

21.图3是本发明第一实施例的电压调节装置的另一电路示意图;

22.图4是本发明第二实施例的电压调节装置的电路示意图;

23.图5是本发明存储器的电路示意图;

24.图6是本发明存储器的存储阵列的电路示意图。

具体实施方式

25.下面结合附图对本发明提供的电压调节装置及采用其的存储器的实施例做详细说明。

26.图1是现有技术中存储器的公共源极端接地电路示意图。请参阅图1,在现有技术中,存储阵列100的公共源极端acs通过一个开关管s接到接地端vss_pad。发明人发现,导致公共源极端acs的电压不稳定的原因在于,在公共源极端acs至接地端vss_pad的路径上存在若干个电阻。具体地说,在公共源极端acs至接地端vss_pad的路径上存在的电阻包括:从vss_pad到开关管s的布线电阻r1、开关管s的导通电阻、从公共源极端acs到开关管s的布线电阻r2。当存储芯片的工作电流流过这些电阻时,会产生相应的压降。例如,存储芯片的存

储阵列100汇集到公共源极端acs的电流i1,存储芯片的其他工作模块的工作电流i2等。该些电阻上的压降使得公共源极端acs的电压不稳定,不是理想的“地”,而是随着存储芯片的不同位置、不同时间而变化。于是对存储阵列的放电电流产生了影响,最终影响了读取的精度。

27.因此,本发明提供一种电压调节装置,其能够调节公共源极端acs处的电压,将其钳位在一设定值,从而提高公共源极端acs的电压的稳定性及一致性。

28.本发明电压调节装置用于调节预设采样点处的电压。图2是本发明第一实施例的电压调节装置的电路示意图。请参阅图2,所述电压调节装置包括运算放大器opamp、上拉晶体管mp1及下拉晶体管mn1。

29.所述运算放大器opamp包括反相输入端、同相输入端及输出端。所述反相输入端输入一参考电压vref,所述同相输入端与预设采样点a电连接,用于输入所述预设采样点a的电压va,形成反馈环路。

30.所述参考电压vref可根据所述预设采样点a的需求电压而设置,所述参考电压vref可与所述预设采样点a的需求电压相等。

31.在本实施例中,所述上拉晶体管mp1为pmos管。所述上拉晶体管mp1包括控制端、第一端及第二端。所述控制端与所述运算放大器opamp的所述输出端电连接,所述第一端与电源vcc电连接,所述第二端与所述预设采样点a电连接。也就是说,所述运算放大器opamp的输出信号vout作为所述上拉晶体管mp1的控制端的输入信号,所述上拉晶体管mp1第二端的输出信号作为所述预设采样点a的电压信号。

32.在本实施例中,所述下拉晶体管mn1为nmos管。所述下拉晶体管mn1包括控制端、第一端及第二端。所述控制端与所述运算放大器opamp的所述输出端电连接,所述第一端与接地端vss电连接,所述第二端与所述预设采样点a电连接。也就是说,所述运算放大器opamp的输出信号vout作为所述下拉晶体管mn1的控制端的输入信号,所述下拉晶体管mn1第二端的输出信号作为所述预设采样点a的电压信号。

33.在本发明电压调节装置中,所述上拉晶体管mp1的控制端与所述下拉晶体管mn1的控制端均连接至所述运算放大器opamp的输出端,则所述运算放大器opamp的输出端的输出信号作为所述上拉晶体管mp1及所述下拉晶体管mn1的控制信号。所述上拉晶体管mp1的第二端(即输出端)与所述下拉晶体管mn1的第二端(即输出端)均连接至所述预设采样点a,则所述上拉晶体管mp1的输出信号与所述下拉晶体管mn1的输出信号共同作为所述预设采样点a的电压信号。

34.本发明电压调节装置的工作过程描述如下:

35.当预设采样点a的电压下降时,运算放大器opamp的同相输入端的电压va小于反相输入端的电压vref,则运算放大器opamp输出端的输出电压vout降低,这使得上拉晶体管mp1及下拉晶体管mn1的导通能力发生改变。具体地说,上拉晶体管mp1的控制端的电压降低,上拉晶体管mp1的上拉能力变强;下拉晶体管mn1的控制端的电压降低,下拉晶体管mn1的下拉能力变弱,上拉晶体管mp1与下拉晶体管mn1协同作用,所述输出端的电压上升,即使得所述预设采样点a的电压上升,从而可调节预设采样点a的电压,避免其下降,保持稳定。

36.当预设采样点a的电压升高时,运算放大器opamp的同相输入端的电压va大于反相输入端的电压vref,则运算放大器opamp输出端的输出电压vout升高,这使得上拉晶体管

mp1及下拉晶体管mn1的导通能力发生改变。具体地说,上拉晶体管mp1的控制端的电压升高,上拉晶体管mp1的上拉能力变弱;下拉晶体管mn1的控制端的电压升高,下拉晶体管mn1的下拉能力变强,,上拉晶体管mp1与下拉晶体管mn1协同作用,所述输出端的电压下降,即使得所述预设采样点a的电压下降,从而可调节预设采样点a的电压,避免其升高,保持稳定。

37.本发明电压调节装置能够根据预设采样点a的反馈而调节预设采样点a处的电压,使其保持稳定,提高预设采样点的电压稳定性及一致性。

38.进一步,当所述电压调节装置作为存储器的存储阵列的公共源极端与接地端之间的连接装置时,所述电压调节装置在工作时主要是吸收电流,而不是提供电流,而吸收电流的工作模式对应存储阵列的读取,此时对速度的要求较高,即对输出的下拉能力要求较高,而对输出的上拉能力要求较低,所以,在本实施例中,所述下拉晶体管mn1的下拉能力大于所述上拉晶体管mp1的上拉能力,以适用于其工作模式。也就是说,在本实施例中,所述下拉晶体管mn1与所述上拉晶体管mp1为非对称关系。其中,可通过改变所述下拉晶体管mn1与所述上拉晶体管mp1的宽长比等实现两者的非对称。

39.进一步,电压调节装置工作在伪甲乙类模式下。具体地说,在上拉或者轻载时,所述电压调节装置工作于甲乙类模式下,在重载时,所述电压调节装置的工作在甲类模式下。具体地说,请参阅图3,其为本发明第一实施例的另一电路示意图,所述运算放大器opamp包括跨导级(gm stage)、甲乙类的偏置电路(class ab bias)及电流镜ia及ib。该些结构为所述运算放大器opamp的常规结构,不再赘述。当所述电压调节装置作为存储器的存储阵列的公共源极端与接地端之间的连接装置时,由于下拉的电流需要很大,在读取时,下拉晶体管mn1的栅极电压(vg_mn1)会拉得很高,而甲乙类的偏置电路(classab bias)中的vbn、vbp都是预设的固定电压。当下拉晶体管mn1的栅极电压(vg_mn1)很高时,甲乙类的偏置电路(classab bias)中的nmos管(mnb)就会关闭,使得电路实际上工作于甲类放大器模式(classa);而当下拉的电流很小时,下拉晶体管mn1的栅极电压(vg_mn1)不会很高,甲乙类的偏置电路(classab bias)中的nmos管(mnb)不会关闭,使得电路工作于甲乙类放大器模式(classab)。因此,在上拉或轻载模式下,该电压调整装置工作于甲类模式;在重载模式下,工作于甲乙类模式。

40.进一步,所述运算放大器opamp和上拉晶体管mp1及下拉晶体管mn1均制作在低压的电源域(vcc域),因此,所述上拉晶体管mp1与所述下拉晶体管mn1均采用低压晶体管,以在实现功能的同时简化版图设计,并节省版图面积。

41.在某些情况下,例如,在存储器进行擦除操作时,不需要通过电压调节装置连接至接地端,即电压调节装置不需要接入存储器的电路中,因此,为了解决该问题,本发明还提供了一第二实施例。所述第二实施例与所述第一实施例的区别在于,所述电压调节装置还包括一开关管。下文将着重描述所述第二实施例与第一实施例的区别。

42.请参阅图4,其为本发明第二实施例的电压调节装置的电路示意图,在所述电压调节装置还包括开关管s,所述上拉晶体管mp1的第二端及所述下拉晶体管mn1的第二端与所述开关管s电连接。所述开关管s用于作为所述电压调节装置的开关,当所述开关管s导通时,所述电压调节装置工作,当所述开关管s截止时,所述电压调节装置不工作。

43.进一步,由于所述开关管s也会存在电压降,从而也会影响存储器的输出端(公共

源极端)的电压,因此,在本实施例中,所述上拉晶体管mp1的第二端及所述下拉晶体管mn1的第二端通过所述开关管s与所述预设采样点a电连接。即,在第二实施例中,所述开关管s也被反馈环路覆盖,使得开关管s的压降对预设采样点a的电压无影响,进一步提高预设采样点a处的电压稳定性及一致性。在本实施例中,当需要所述电压调节装置对所述预设采样点a进行电压调节时,所述开关管s导通,当不需要所述电压调节装置对所述预设采样点a进行电压调节时,所述开关管s截止,以实现所述电压调节装置可选择地对预设采样点a进行电压调节。

44.进一步,在本发明其他实施例中,若所述开关管s的导通电阻较小,其上的压降可以忽略不计,或者开关管s的压降对存储器的输出端(公共源极端)的电压影响不大,则所述预设采样点a也可设置在所述上拉晶体管mp1的第二端及所述下拉晶体管mn1的第二端与所述开关管s连接的路径上。

45.进一步,在第二实施例中,所述开关管s制作在高压域,因此其为高压晶体管。在本实施例中,所述开关管s为高压nmos晶体管。当不需要所述电压调节装置对所述预设采样点a进行电压调节时,向所述开关管s的控制端输入低电平信号,使所述开关管s截止,从而使所述电压调节装置与所述预设采样点a断开连接;当需要所述电压调节装置对所述预设采样点a进行电压调节时,向所述开关管s的控制端输入高电平使能信号,使所述开关管s导通,使所述电压调节装置与所述预设采样点a连接。

46.进一步,当所述电压调节装置作为存储器的存储阵列的公共源极端与接地端之间的连接装置时,在公共源极端的某些工作状态下,例如,执行擦除(erase)操作时,会产生高压,并且不需要所述电压调节装置与公共源极端连接,因此,为了保护所述电压调节装置的内部电路,需要所述开关管s截止。而此时,所述开关管s接收的是高电平信号,若是直接采用该电平信号作为所述开关管s的控制信号,会使所述开关管s导通。因此,本发明所述电压调节装置还包括电平转换器ls(level shifter),所述电平转换ls器与所述开关管s电连接,用于将电压信号进行电平转换后作为所述开关管s的控制信号,以实现所述开关管s的导通与截止。

47.本发明还提供一种采用上述电压调节装置的存储器。请参阅图5,其为本发明存储器的电路示意图,所述存储器包括存储阵列100及上述的电压调节装置500。

48.请参阅图6,其为所述存储阵列100的示意图,所述存储阵列包括在三维空间内阵列排布的多个存储单元,构成多个存储串,位于同一个存储串内的存储单元的沟道在物理上连接。每一个存储串的顶部的晶体管为上选择管tsg,上选择管tsg连接至位线bl,存储串底部的晶体管为下选择管bsg,不同存储串之间通过上选择管tsg和下选择管bsg区分。位于同一层内的多个存储单元组成存储行,位于不同存储串但位于同一存储行内的存储单元的栅极在物理上相连接,均连接至同一字线wl。

49.所述存储阵列100还包括公共源极端acs。所述公共源极端acs用于将所述存储阵列100与接地端电连接。

50.读取存储信息的过程就是判断阈值电压(vth)的过程。在此过程中,首先对位线bl进行上拉,然后打开字线wl,对选中字线(select wl)施加读取电压,非选中字线(unselect wl)施加导通电压(vpass),并将公共源极端acs拉到接地(gnd),以此形成一个电流路径,来对位线进行放电。而随着芯片存储容量和面积的增大,由于芯片的接地端网络强度的限制,

当流过读取电流时,芯片不同位置的接地端电压可能不同,同一个位置、不同时间的接地端电压也可能不同,导致公共源极端acs的电压不稳定,对存储阵列的性能及可靠性产生影响。

51.请继续参阅图5,为了解决上述问题,所述电压调节装置500与所述公共源极端acs电连接,用于将所述公共源极端acs连接至接地端。其中,所述预设采样点a设置在所述公共源极端acs与所述电压调节装置500的连接路径上。

52.本发明存储器能够通过所述电压调节装置500钳位所述预设采样点a的电压,使得其维持稳定,从而使得所述存储阵列100的公共源极端acs电压维持稳定,提高公共源极端acs电压稳定性及一致性,进而提高存储器的读取精度。

53.进一步,所述预设采样点a的设置位置越靠近所述存储阵列100越好,以使所述存储阵列的输出端与接地端的电流路径上的电压降尽可能地被包括在反馈环路中,从而提高存储阵列的输出端的电压的稳定性。

54.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。