技术特征:

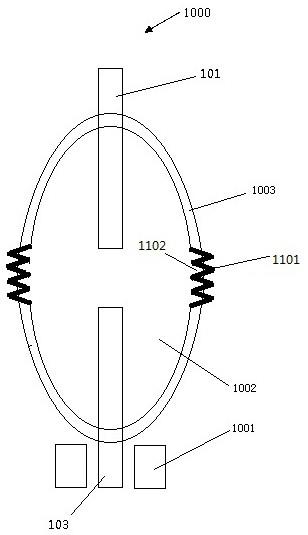

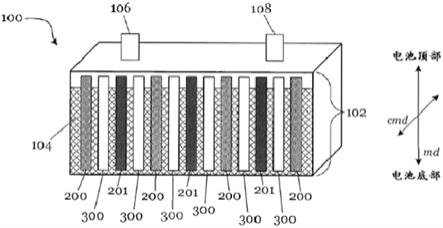

1.一种半导体结构的制备方法,其特征在于,包括如下步骤:提供上表面形成有栅极图形结构的衬底;至少于所述栅极图形结构的侧壁形成栅极侧壁保护层;对所述栅极图形结构执行离子注入;至少于所述栅极图形结构的上表面形成栅极导电层。2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述至少于所述栅极图形结构的上表面形成栅极导电层后,还包括:于所述栅极导电层的上表面形成顶部保护层。3.根据权利要求2所述的半导体结构的制备方法,其特征在于,形成所述栅极侧壁保护层的材料与形成所述顶部保护层的材料相同,所述栅极侧壁保护层的厚度为1nm

‑

5nm。4.根据权利要求2所述的半导体结构的制备方法,所述顶部保护层的厚度大于或等于所述栅极侧壁保护层的厚度。5.根据权利要求3所述的半导体结构的制备方法,其特征在于,形成所述栅极侧壁保护层的材料与形成所述顶部保护层的材料均包括氮化硅。6.根据权利要求2

‑

5任一项所述的半导体结构的制备方法,其特征在于,所述提供上表面具有栅极图形结构的衬底,包括:提供衬底,所述衬底内具有沟槽,所述沟槽内填充满介质材料层;形成栅极氧化层,所述栅极氧化层覆盖所述衬底的上表面及所述介质材料层的上表面;于所述栅极氧化层的上表面形成栅极材料层,并于所述栅极材料层的上表面形成第一图形化光刻胶层;基于所述第一图形化光刻胶层刻蚀所述栅极材料层,以形成所述栅极图形结构。7.根据权利要求6所述的半导体结构的制备方法,其特征在于,相邻所述栅极图形结构的下表面的所述栅极氧化层的厚度不相等。8.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述至少于所述栅极图形结构的侧壁形成栅极侧壁保护层,包括:形成第一保护材料层,所述第一保护材料层覆盖所述栅极图形结构的上表面、侧壁及所述栅极氧化层的上表面;去除位于所述栅极氧化层的上表面的及位于所述栅极图形结构的上表面的所述第一保护材料层,保留的所述第一保护材料层构成所述栅极侧壁保护层。9.根据权利要求8所述的半导体结构的制备方法,其特征在于,形成所述顶部保护层的步骤包括:形成导电材料层,所述导电材料层覆盖所述栅极图形结构的上表面、所述栅极侧壁保护层的上表面及侧壁、所述栅极氧化层的上表面;于所述导电材料层的上表面形成第二保护材料层,所述第二保护材料层的上表面高于所述栅极图形结构的上表面;于所述第二保护材料层的上表面形成第一图形化掩膜层;基于所述第一图形化掩膜层刻蚀所述第二保护材料层,以形成所述顶部保护层。10.根据权利要求9所述的半导体结构的制备方法,其特征在于,形成所述栅极导电层

的步骤包括:去除覆盖所述栅极侧壁保护层及所述栅极氧化层的上表面的所述导电材料层,保留的所述导电材料层构成所述栅极导电层。11.根据权利要求9所述的半导体结构的制备方法,其特征在于,所述于所述第二保护材料层的上表面形成第一图形化掩膜层,包括:于所述第二保护材料层的上表面形成第一掩膜层;于所述第一掩膜层的上表面形成第二图形化光刻胶层;基于所述第二图形化光刻胶层刻蚀所述第一掩膜层,以形成所述第一图形化掩膜层。12.根据权利要求9所述的半导体结构的制备方法,其特征在于,所述于所述第二保护材料层的上表面形成第一图形化掩膜层,包括:于所述第二保护材料层的上表面形成第一掩膜层;于所述第一掩膜层的上表面依次形成第二掩膜层和第三掩膜层;于所述第三掩膜层的上表面形成第二图形化光刻胶层;基于所述第二图形化光刻胶层刻蚀所述第三掩膜层和所述第二掩膜层,以形成第二图形化掩膜层;基于所述第二图形化掩膜层刻蚀所述第一掩膜层,以形成所述第一图形化掩膜层。13.根据权利要求9所述的半导体结构的制备方法,其特征在于:形成所述导电材料层的材料包括氮化钛、钛、硅化钨和钨中的一种或多种。14.根据权利要求1

‑

5任一项所述的半导体结构的制备方法,其特征在于,对所述栅极图形结构执行离子注入的步骤包括:对相邻所述栅极图形结构执行不同导电类型的离子注入。15.根据权利要求14所述的半导体结构的制备方法,其特征在于,对相邻所述栅极图形结构分别执行p型离子注入、n型离子注入。16.一种半导体结构,其特征在于,包括:衬底,其上表面形成有栅极图形结构;栅极侧壁保护层,至少覆盖所述栅极图形结构的侧壁,其中,所述栅极图形结构内形成有掺杂栅极材料层;栅极导电层,至少覆盖所述栅极图形结构的上表面。17.根据权利要求16所述的半导体结构,其特征在于,还包括:顶部保护层,覆盖所述栅极导电层的上表面。

技术总结

本申请涉及一种半导体结构的制备方法及半导体结构,所述方法包括:提供上表面形成有栅极图形结构的衬底;至少于所述栅极图形结构的侧壁形成栅极侧壁保护层;对所述栅极图形结构执行离子注入;至少于所述栅极图形结构的上表面形成栅极导电层。本申请避免掺杂的不均匀性导致后续在刻蚀异质结构的过程中产生栅极侧壁倾斜或扭曲现象,有效地优化栅极形貌,提高制成半导体产品的良率及可靠性。高制成半导体产品的良率及可靠性。高制成半导体产品的良率及可靠性。

技术研发人员:张仕然 陈洋 韩欣茹

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.07.19

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。