1.本发明涉及一种半导体封装及其制造方法,特别是一种能够有效提高焊接可靠性和对准精度的半导体封装及其制造方法。

背景技术:

2.半导体集成电路(ic)行业经历了指数级增长。ic材料和设计的技术进步已经产生了多代ic,其中每一代都具有比上一代更小和更复杂的电路。在ic发展的过程中,功能密度(例如,每芯片面积的互连器件的数量)通常已经增加,而几何尺寸(例如,可以使用制造工艺产生的最小的部件或线)已经减小。这种按比例缩小工艺通常通过提高生产效率和降低相关成本来提供收益。

3.倒装(flip chip)封装技术是一种基于小尺寸芯片、高i/o密度,并具有优秀电学和热学性能的互连方式。通过在芯片焊盘上制备焊球或者凸块后贴装在电路板上。在该技术中,相对于形成在晶圆上的集成电路(“ic”),金属焊盘形成在ic晶圆的上表面上。焊料凸块或铜凸块沉积在金属焊盘上。然后从晶圆上切割ic成ic管芯。切割的ic管芯被翻转并放置在载体衬底上,使得焊料凸块面向载体衬底上的连接件。然后,例如使用热超声接合或可选地回流焊工艺来重新熔化焊料凸块,使得ic牢固地耦合到载体衬底。在熔化的焊料凸块和连接件之间形成电连接。用电绝缘胶ic底部填充ic管芯和下面的载体衬底之间的小间隔。

4.在上述器件的生产封装过程中,芯片焊接是封装过程中的重点控制工序,此工艺的目的是将芯片表面金属凸块(bump)朝下进行基板互联,使芯片与封装基板形成良好的欧姆接触和散热通路。然而,在回流焊接过程时,由于回流焊接温度不合理设定,会导致大量的焊接缺陷产生,如金属凸块上锡球熔融过量,金属凸块破裂,凸块与锡球对位偏移,这些缺陷均影响了产品的性能和可靠性。

技术实现要素:

5.因此,本发明的目的在于克服以上技术障碍而提供一种创新性的半导体封装及其制造方法,使得熔融的焊料焊接更加均匀及减小了凸块回流缺陷及凸块与基板焊盘焊接偏移的风险,从而提高了产品信号传输及可靠性。

6.本发明提供了一种半导体封装,包括:

7.基板,顶面具有多个基板焊盘;

8.芯片,底面具有多个芯片焊盘;

9.多个堆叠结构,每个堆叠结构包括凸块和焊球,分别将多个基板焊盘的一个与多个芯片焊盘的相对应一个电连接;

10.多个第一柱体,在芯片底面的边缘处,与基板顶面上的多个对准标记或者多个第二柱体在竖直方向上对准;

11.密封剂,包裹芯片、多个堆叠结构、多个第一柱体和/或多个第二柱体。

12.其中,多个第一柱体和/或多个第二柱体的材料为金属、金属的合金、金属的导电氮化物、金属的导电氧化物及其组合,所述金属选自al、cu、mo、w、pt、ni、cr、nd、ti、ta、hf、zr、mg、zn的任一个。

13.其中,多个第一柱体与多个第二柱体的截面形状和/或尺寸相同。

14.其中,多个第一柱体的高度大于多个堆叠结构中凸块的高度,或者多个第一柱体的高度小于多个堆叠结构中凸块的高度并且多个第二柱体的高度大于多个堆叠结构中焊球的高度。

15.其中,多个第一柱体和/或多个第二柱体的侧壁竖直并具有对准图形。

16.其中,多个第一柱体的底面与多个第二柱体的顶面分别具有凹凸结构、粗糙纹理或者磁性构件。

17.其中,多个第一柱体关于芯片的中心对称分布,和/或多个第二柱体关于基板的中心对称分布。

18.本发明还提供了一种半导体封装的制造方法,包括步骤:

19.步骤1,在芯片的底面上边缘处形成多个第一柱体;

20.步骤2,在芯片的底面上的多个芯片焊盘的每一个上形成堆叠结构,堆叠结构包括凸块和焊球;

21.步骤3,将芯片倒装安放在基板上,使得多个第一柱体与基板顶面上的多个对准标记或者多个第二柱体在竖直方向上对准;

22.步骤4,执行回流焊接,利用焊球将芯片固定在基板上,并通过堆叠结构的凸块和焊球将多个基板焊盘的一个与多个芯片焊盘的相对应一个电连接。

23.其中,在步骤2之后、步骤3之前进一步包括步骤2b,在基板的顶面上形成多个第二柱体。

24.其中,步骤2在步骤1之前或者同时执行。

25.依照本发明的半导体封装及其制造方法,在芯片底部设置定位柱体,与基板上的定位柱体结合使用,在回流焊接过程中有效地预防焊锡熔融过大,提高了焊接可靠性和对准精度。

26.本发明所述目的,以及在此未列出的其他目的,在本技术独立权利要求的范围内得以满足。本发明的实施例限定在独立权利要求中,具体特征限定在其从属权利要求中。

附图说明

27.以下参照附图来详细说明本发明的技术方案,其中:

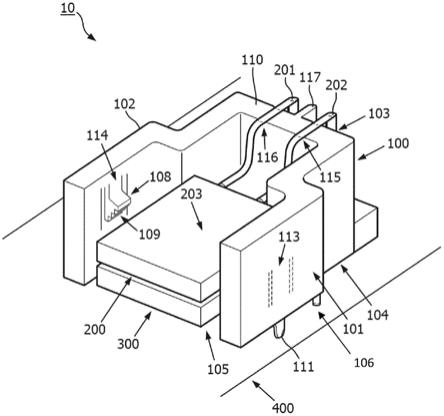

28.图1显示了根据本发明一个实施例的半导体封装的剖视图;

29.图2显示了图1的半导体封装中芯片底面的平视图;

30.图3显示了根据本发明另一实施例的半导体封装的剖视图;

31.图4显示了图3的半导体封装中基板顶面的平视图;以及

32.图5显示了根据本发明实施例的半导体封装制造方法的流程图。

具体实施方式

33.以下参照附图并结合示意性的实施例来详细说明本发明技术方案的特征及其技

术效果,公开了有效提高回流焊可靠性和对准精度的半导体封装及其制造方法。需要指出的是,类似的附图标记表示类似的结构,本技术中所用的术语“第一”、“第二”、“上”、“下”等等可用于修饰各种器件结构。这些修饰除非特别说明并非暗示所修饰器件结构的空间、次序或层级关系。

34.如图1所示,根据本发明一个优选实施例的半导体封装包括基板1、芯片2、封装树脂7。基板1例如是印刷电路板(pcb),其包括有机或无机材料构成的多个绝缘层,按照布线需要设置在各个绝缘层之间的金属互连层或再布线层(rdl),以及在基板顶表面上的多个焊盘(图1中未示出,图4中以4b表示)。此外,基板1也可以是引线框架(lead frame),具有被密封剂包裹的金属迹线和迹线顶表面上的焊盘。芯片2可以是各种常用的半导体芯片,例如基于cmos工艺制造的硅基逻辑/存储电路、基于双极或bimos工艺制造的功率器件、基于iii

‑

v或ii

‑

vi族化合物的发光二极管(led)等等。芯片2具有底面,其包括用作芯片2内部的电信号输入/输出的多个金属迹线或焊盘3,例如用al、cu、mo、w、pt、ni及其合金制成。

35.在芯片2底面的外围区域(图2中为左上角和右下角至少两个角部)形成有多个第一柱体4a,例如采用与金属迹线或焊盘3相同的制造工艺而形成较大的厚度,也可以在外围区域中的伪焊盘上采用键合、压合或粘合的方式形成。优选地,第一柱体4a为硬质导电材料,以便在后续回流焊过程中提供足够的机械支撑,预防凸块上焊锡熔融过大,同时也因为材质较硬具有准直的侧壁而便于在芯片倒装过程中提高对准精度,并且进一步由于良好的导热性而防止回流焊过程中芯片边缘翘曲从而进一步提高了对准精度。例如,第一柱体4a材料为金属、金属合金、导电金属氮化物、导电金属氧化物及其组合,其中所述金属选自al、cu、mo、w、pt、ni、cr、nd、ti、ta、hf、zr、mg、zn等等。虽然图2中示出第一柱体4a为圆形截面,但实际上还可以选用矩形、方形、梯形、三角形、椭圆形、星形、菱形、十字形、诸如五边形、六边形、八边形的其他多边形、或不规则形状等等。柱体4a具有竖直侧壁,并进一步优选地在侧壁上具有竖直分布的图形(例如凹槽或突起,诸如柱体的侧棱),以便在对准工艺期间利用竖直侧壁及其侧壁图形而提高目视或光学/激光对准的精度。进一步,虽然图2中示出的第一柱体4a为对称角部上的两个,但是也可以选用更多的数目,并且优选地多个第一柱体4a关于芯片2的几何中心分布对称(线对称、点对称或旋转对称),从而提高倒转对准工艺的效率。

36.芯片2的焊盘3上通过电镀、化学镀、键合、压合、导电胶粘合等等工艺而提供了金属凸块(bump)5,优选为cu、sn、al、ag、ni、au、pt、pd及其合金,用于在芯片2倒装回流焊期间提供足够的机械支撑,避免焊球移位,并且同时还优选可焊接材料以促进与焊锡球之间的接合强度。金属凸块5上形成有焊球6,通过焊球6与基板1表面的焊盘接触、焊接从而实现物理连接和电连接。金属凸块6的截面通常为圆形,以便焊球6在回流过程中均匀地分布在凸块表面上而不会从尖锐的角部或突出部向侧壁溢流。焊球6的材料可以是有铅焊料或无铅焊料。优选地,焊球6与基板1顶面焊盘之间还可以具有助焊剂或锡膏(未示出),提高与基板之间的焊接可靠性。

37.如图1所示,当仅在芯片2底部形成第一柱体4a时,第一柱体4a的高度优选地大于金属凸块5的高度,从而使得柱体4a与基板1之间的间隙足够小,例如小于等于5微米、小于等于100nm,如此使得回流焊过程中即便有少量焊球6熔化过度移位导致局部悬空或扭曲/倾斜,芯片2的水平面由于受到第一柱体4a的支撑从而不会过度倾斜,从而确保了焊接的可

靠性。

38.进一步,为了在芯片2倒装安放过程中提高对准精度,在图3、图4所示的另一个优选实施例中,在基板1顶面设置多个第二柱体4b,其材料、形状、尺寸和形成工艺与第一柱体4a相同,并且平面分布使得芯片2倒装在基板1顶面时每个第一柱体4a均与各自的第二柱体4b在厚度方向(z轴或基板法线方向)重叠,由此使得第一柱体4a与第二柱体4b能够垂直地对准。在该实施例中,第一柱体4a的高度可以略小于金属凸块5(例如高度差小于等于200nm)并且第二柱体4b的高度略大于焊球6的厚度(例如高度差大于等于200nm),从而使得柱体4a

‑

4b之间存在的间隙小于等于5微米、小于等于100nm,由此实现与图1所示的实施例所述相同的机械支撑强度。第二柱体4b的侧壁也是竖直的,并优选地,侧壁上具有与第一柱体4a侧壁图形相同或相对应的图形,从而便于从侧面实现目视或光学/激光对准,解决了传统工艺中难以从倒装的芯片2顶面测量水平方向位移的难题。在本发明其他优选实施例中,第二柱体4b的高度可以进一步缩减,直至其降低成为基板1表面的对准标记(例如仅超过基板1顶面50nm以内),此时该对准标记则需要扩大平面尺寸以便从芯片2顶面边界超出从而利于从顶部观察对准情况。

39.在本发明其他优选实施例中,第一柱体4a与第二柱体4b相对的面(例如第一柱体4a的底面,第二柱体4b的顶面)上还可以增设啮合结构,例如凹部与凸部的组合、或者其他互补的粗糙纹理等等,由此增强了柱体之间的机械结合强度,有利地避免了芯片2边缘处的翘曲或倾斜。进一步,还可以在第一柱体4a的底面与第二柱体4b的顶面上分别设置(例如通过焊接、键合、粘合、电镀等等)极性不同的磁性构件(例如强磁性膜层,未示出),从而利用磁性吸附提高倒装安放过程中的操作效率。

40.如图5所示,依照本发明上述优选实施例的半导体封装的制造方法包括以下步骤:

41.步骤1,在芯片2底面上形成多个第一柱体4a;

42.步骤2,在芯片2底面的焊盘3上形成凸块5,凸块5顶部优选地具有焊料,步骤2可以与步骤1同时进行,或者在步骤1之前进行;

43.优选地,插入步骤2b,在基板1的顶面上形成多个第二柱体4b,步骤2b也可以在步骤1、2之前进行;

44.步骤3,将芯片2倒装安放在基板1上,其中多个第一柱体4a与基板1上的对准标记或者多个第二柱体4b在平视图中重叠对准,其中采用设备吸嘴从晶圆上取芯同时将芯片的凸块5粘贴在基板焊接区域,图像识别参点为芯片上的第一柱体4a与基板上的对准标记或第二柱体4b;

45.步骤4,执行回流焊接,利用焊球6将芯片2固定在基板1上。

46.此后,芯片2上的第一柱体4a、基板1上的第二柱体4b不需要拆除或分解,随产品续流后工序塑封,例如在整个装置上涂覆封装树脂7,完成封装并进行质量检验。

47.步骤3之中,倒装连接方法可以是焊料焊接、热压焊接、热声焊接、或粘胶连接等等,只要能够使得芯片2倒装并与基板1对准即可。

48.依照本发明的半导体封装及其制造方法,在芯片底部设置第一柱体,与基板上的第二柱体结合使用,在回流焊接过程中有效地预防焊锡熔融过大,提高了焊接可靠性和对准精度。

49.尽管已参照一个或多个示例性实施例说明本发明,本领域技术人员可以知晓无需

脱离本发明范围而对器件结构做出各种合适的改变和等价方式。此外,由所公开的教导可做出许多可能适于特定情形或材料的修改而不脱离本发明范围。因此,本发明的目的不在于限定在作为用于实现本发明的最佳实施方式而公开的特定实施例,而所公开的器件结构及其制造方法将包括落入本发明范围内的所有实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。