一种用于芯片封装的引线框架及制备方法和芯片封装结构

[技术领域]

[0001]

本发明涉及芯片封装,尤其涉及一种用于芯片封装的引线框架及制备方法和芯片封装结构。

[

背景技术:

]

[0002]

引线框架的主要功能是为芯片提供机械支撑的载体,并作为导电介质内外连接芯片电路而形成电信号通路,以及与封装外壳一同向外散发芯片工作时产生热量的散热通路。

[0003]

申请号为cn202011273348.x用于芯片封装的引线框架及制备方法和芯片封装结构的发明公开了一种用于芯片封装的引线框架及制备方法和芯片封装结构。引线框架包括承载片、阻焊油墨层和复数个按矩阵布置的单元电路,单元电路包括复数个电极,电极包括顶电极和底电极;顶电极布置在阻焊油墨层的顶面;对应于每个单元电路,阻焊油墨层包括与电极对应的底电极孔,底电极布置在底电极孔中,底电极的顶部固定在顶电极的底面上;承载片可剥离地粘贴在阻焊油墨层和底电极的底面上。

[0004]

该发明的底电极直接固定在顶电极的底面上,底电极与顶电极之间没有耐蚀层隔开,顶电极的横向尺寸必须大于底电极的横向尺寸,而且两者不能错开,单元电路顶电极之间的空间狭小。难以布置较多的走线。

[

技术实现要素:

]

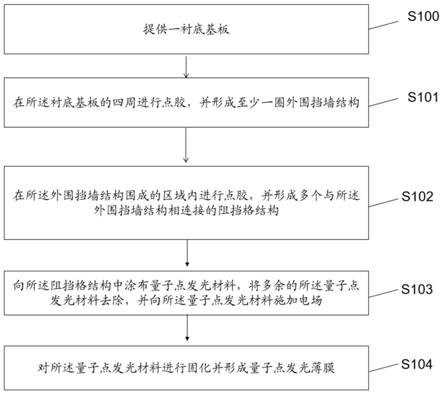

[0005]

本发明要解决的技术问题是提供一种单元电路顶电极之间的空间较大,便于布线的用于芯片封装的引线框架。

[0006]

本发明另一个要解决的技术问题是提供一种上述引线框架的制备方法。

[0007]

本发明另一个要解决的技术问题是提供一种顶电极之间的空间较大,便于布线的芯片封装结构。

[0008]

为了解决上述技术问题,本发明采用的技术方案是,一种用于芯片封装的引线框架,包括承载片、可沉铜油墨层和复数个按矩阵布置的单元电路,单元电路包括复数个电极,电极包括顶电极和底电极,顶电极布置在可沉铜油墨层的顶面上,底电极布置在可沉铜油墨层的底面上;电极包括布置在可沉铜油墨层中的第一金属化过孔,顶电极与底电极通过第一金属化过孔连接;承载片可剥离地粘贴在可沉铜油墨层和底电极的底面上。

[0009]

以上所述的用于芯片封装的引线框架,单元电路包括基岛,基岛包括上基岛、下基岛和布置在可沉铜油墨层中的第二金属化过孔;上基岛布置在可沉铜油墨层的顶面上,下基岛布置在可沉铜油墨层的底面上,上基岛与下基岛通过第二金属化过孔连接;承载片可剥离地粘贴在下基岛的底面上。

[0010]

以上所述的用于芯片封装的引线框架,包括阻焊油墨层,阻焊油墨层覆盖在可沉铜油墨层和顶电极的上方,阻焊油墨层包括与单元电路对应的窗口,顶电极的焊盘裸露于所述的窗口中。

[0011]

一种上述引线框架的制备方法,包括以下步骤:

[0012]

401)在铜箔的顶面贴承载膜,在铜箔的底面印刷可沉铜油墨层;

[0013]

402)在可沉铜油墨层上光刻或激光镭射出第一过孔,对第一过孔电镀金属填孔,形成所述的第一金属化过孔;在可沉铜油墨层的底面金属化镀铜,形成镀铜层;

[0014]

403)在镀铜层的底面上覆盖第一感光膜,第一感光膜通过光刻制作出与底电极对应的、镂空的图形;对镀铜层蚀刻,在可沉铜油墨层的下方形成底电极;

[0015]

404)将承载片可剥离地粘贴在可沉铜油墨层和底电极的底面上,将铜箔顶面的承载膜剥离,在铜箔顶面覆盖第二感光膜;

[0016]

405)第二感光膜通过光刻制作出与顶电极对应的、镂空的图形,对铜箔蚀刻,在可沉铜油墨层上方形成顶电极。

[0017]

以上所述的制备方法,所述的单元电路包括基岛,基岛包括上基岛、下基岛和布置在可沉铜油墨层中的第二金属化过孔;上基岛布置在可沉铜油墨层的顶面上,下基岛布置在可沉铜油墨层的底面上,上基岛与下基岛通过第二金属化过孔连接;承载片可剥离地粘贴在下基岛的底面上,制备方法包括以下步骤:

[0018]

501)在步骤402中,在可沉铜油墨层上同时光刻或激光镭射出第二过孔,对第二过孔电镀金属填孔,形成所述的第二金属化过孔;

[0019]

502)在步骤403中,第一感光膜通过光刻制作出与底电极及下基岛对应的、镂空的图形;对镀铜层蚀刻,在可沉铜油墨层的下方形成底电极和下基岛;

[0020]

503)在步骤404中,承载片同时可剥离地粘贴在下基岛的底面上;

[0021]

504)在步骤405中,第二感光膜通过光刻制作出与顶电极及上基岛对应的、镂空的图形;对铜箔蚀刻时,在可沉铜油墨层上方同时形成上基岛。

[0022]

以上所述的制备方法,所述的蚀刻为酸性蚀刻或碱性蚀刻。

[0023]

以上所述的制备方法,步骤405完成后,在可沉铜油墨层和顶电极的上方印刷阻焊油墨层;阻焊油墨层包括与单元电路对应的窗口,顶电极的焊盘裸露于所述的窗口中。

[0024]

一种芯片封装结构,包括芯片、封装胶层、复数个电极和可沉铜油墨层,电极包括顶电极、底电极和布置在可沉铜油墨层中的第一金属化过孔,顶电极布置在可沉铜油墨层的顶面上,底电极布置在可沉铜油墨层的底面上,顶电极与底电极通过第一金属化过孔连接;封装胶层覆盖在可沉铜油墨层和顶电极的上方,芯片封装在封装胶层中,芯片的复数个电极分别与复数个顶电极电连接。

[0025]

以上所述的芯片封装结构,包括阻焊油墨层,所述的芯片为倒装芯片;阻焊油墨层覆盖在可沉铜油墨层和顶电极的上方,并为封装胶层所覆盖;阻焊油墨层包括窗口,顶电极的焊盘裸露于所述的窗口中;倒装芯片布置在窗口中,倒装芯片的复数个电极分别与对应的顶电极的焊盘焊接。

[0026]

以上所述的芯片封装结构,包括基岛,基岛包括上基岛、下基岛和布置在可沉铜油墨层中的第二金属化过孔;上基岛布置在可沉铜油墨层的顶面上,下基岛布置在可沉铜油墨层的底面上,上基岛与下基岛通过第二金属化过孔连接;所述的芯片为正装芯片,正装芯片的底面固定在上基岛上,正装芯片的复数个电极分别通过键合线与对应的顶电极的焊盘电连接。

[0027]

本发明引线框架的顶电极与底电极之间有可沉铜油墨层隔开,两者仅通过金属化

过孔连接,顶电极的尺寸和形状不受底电极的限制,单元电路的布线较为方便。

[附图说明]

[0028]

下面结合附图和具体实施方式对本发明作进一步详细的说明。

[0029]

图1是本发明实施例2引线框架制备方法步骤1的示意图。

[0030]

图2是本发明实施例2引线框架制备方法步骤2的示意图。

[0031]

图3是本发明实施例2引线框架制备方法步骤3的示意图。

[0032]

图4是本发明实施例2引线框架制备方法步骤4的示意图。

[0033]

图5是本发明实施例2引线框架制备方法步骤5的示意图。

[0034]

图6是本发明实施例2引线框架制备方法步骤6的示意图。

[0035]

图7是本发明实施例2引线框架制备方法步骤7的示意图。

[0036]

图8是本发明实施例2引线框架制备方法步骤8的示意图。

[0037]

图9是本发明实施例2引线框架制备方法步骤9的示意图。

[0038]

图10是本发明实施例2引线框架制备方法步骤10的示意图。

[0039]

图11是本发明实施例2引线框架制备方法步骤11的示意图。

[0040]

图12是本发明实施例2引线框架制备方法步骤12的示意图,

[0041]

图13是本发明实施例2引线框架制备方法步骤13的示意图。

[0042]

图14是本发明实施例2引线框架制备方法步骤14的示意图。

[0043]

图15是本发明实施例1用于倒装芯片封装的引线框架一个单元电路的结构图。

[0044]

图16是本发明实施例4倒装led芯片封装结构的结构图。

[0045]

图17是本发明实施例3引线框架制备方法步骤5的示意图。

[0046]

图18是本发明实施例3引线框架制备方法步骤6的示意图。

[0047]

图19是本发明实施例3引线框架制备方法步骤7的示意图。

[0048]

图20是本发明实施例3引线框架制备方法步骤8的示意图。

[0049]

图21是本发明实施例3引线框架制备方法步骤9的示意图。

[0050]

图22是本发明实施例3引线框架制备方法步骤10的示意图。

[0051]

图23是本发明实施例3引线框架制备方法步骤11的示意图。

[0052]

图24是本发明实施例3引线框架制备方法步骤12的示意图。

[0053]

图25是本发明实施例3引线框架制备方法步骤13的示意图。

[0054]

图26是本发明实施例3引线框架制备方法步骤14的示意图。

[0055]

图27是本发明实施例3引线框架制备方法步骤15的示意图。

[0056]

图28是本发明实施例6引线框架制备方法步骤1的示意图。

[0057]

图29是本发明实施例6引线框架制备方法步骤2的示意图。

[0058]

图30是本发明实施例6引线框架制备方法步骤3的示意图。

[0059]

图31是本发明实施例6引线框架制备方法步骤4的示意图。

[0060]

图32是本发明实施例6引线框架制备方法步骤5的示意图。

[0061]

图33是本发明实施例6引线框架制备方法步骤6的示意图。

[0062]

图34是本发明实施例6引线框架制备方法步骤7的示意图。

[0063]

图35是本发明实施例6引线框架制备方法步骤8的示意图。

[0064]

图36是本发明实施例6引线框架制备方法步骤9的示意图。

[0065]

图37是本发明实施例7引线框架制备方法步骤1的示意图。

[0066]

图38是本发明实施例7引线框架制备方法步骤2的示意图。

[0067]

图39是本发明实施例7引线框架制备方法步骤3的示意图。

[0068]

图40是本发明实施例7引线框架制备方法步骤4的示意图。

[0069]

图41是本发明实施例7引线框架制备方法步骤5的示意图。

[0070]

图42是本发明实施例7引线框架制备方法步骤6的示意图。

[0071]

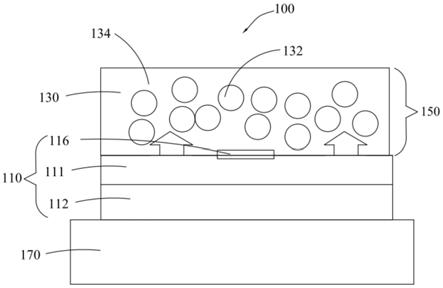

图43本发明实施例8正装芯片封装结构的结构图。

[具体实施方式]

[0072]

本发明实施例1用于倒装芯片封装的引线框架一个单元电路的结构如图15所示。引线框架包括承载片12、阻焊油墨层7、可沉铜油墨层3和多个按矩阵布置的单元电路。单元电路包括两个电极,电极包括顶电极1

‑

1、底电极4

‑

1和布置在可沉铜油墨层3中的第一金属化过孔4

‑

2,顶电极1

‑

1布置在可沉铜油墨层3的顶面上,底电极4

‑

1布置在可沉铜油墨层3的底面上。顶电极1

‑

1与底电极4

‑

1通过第一金属化过孔4

‑

2连接。承载片12可剥离地粘贴在可沉铜油墨层3和底电极4

‑

1的底面上。底电极4

‑

1的底面电镀有可焊金属层4

‑

3。阻焊油墨层7覆盖在可沉铜油墨层3和顶电极1

‑

1的上方,阻焊油墨层7上有与单元电路对应的窗口7

‑

1,顶电极1

‑

1的焊盘裸露于窗口7

‑

1中,顶电极1

‑

1的焊盘的表面电镀有可焊金属层1

‑

3。

[0073]

本发明实施例2为实施例1引线框架的制备方法,采用酸性蚀刻工艺,并包括以下步骤:

[0074]

1)如图1所示,在铜箔1的顶面贴承载膜2,在铜箔1的底面印刷可沉铜油墨层3。可沉铜油墨层3采用太阳(taiyo)公司psr

‑

4000bn black/ca

‑

40bn或psr

‑

4000lew3/ca

‑

40lew3的可沉铜树脂油墨。

[0075]

2)如图2所示,在可沉铜油墨层3上光刻或激光镭射出两个第一过孔3

‑

1。

[0076]

3)如图3所示,对第一过孔3

‑

1电镀金属填孔,形成第一金属化过孔4

‑

2。同步在可沉铜油墨层3的底面金属化镀铜,形成镀铜层4;金属化镀铜采用先化学沉铜再电镀铜的工艺。

[0077]

4)如图4所示,在镀铜层4的底面上覆盖第一感光膜5。

[0078]

5)如图5所示,第一感光膜5通过光刻制作出与底电极4

‑

1对应的、镂空的图形,第一感光膜5镂空图形的余留的实体部分5

‑

1与底电极4

‑

1的形状对应。

[0079]

6)如图6所示,对镀铜层4蚀刻,在可沉铜油墨层3的下方形成底电极4

‑

1。

[0080]

7)如图7所示,通过药液浸泡,去除第一感光膜5。

[0081]

8)如图8所示,在底电极4

‑

1的裸露区域上电镀可焊金属层4

‑

3。

[0082]

9)如图9所示,将承载片12可剥离地粘贴在可沉铜油墨层3和底电极4

‑

1可焊金属层4

‑

3的底面上。

[0083]

10)如图10所示,将铜箔1顶面的承载膜2剥离,在铜箔1顶面覆盖第二感光膜6。

[0084]

11)如图11所示,第二感光膜6通过光刻制作出与顶电极1

‑

1对应的、镂空的图形,第二感光膜6感光层镂空图形的余留的实体部分6

‑

1与顶电极1

‑

1的形状对应。

[0085]

12)如图12所示,对铜箔1蚀刻,在可沉铜油墨层3上方形成顶电极1

‑

1。

[0086]

13)如图13所示,通过药液浸泡,去除第二感光膜6。

[0087]

14)如图14所示,在可沉铜油墨层3和顶电极1

‑

1的上方印刷阻焊油墨层7。阻焊油墨层7包括与单元电路对应的窗口7

‑

1,顶电极1

‑

1的焊盘裸露于窗口7

‑

1中。

[0088]

15)如图15所示,在窗口7

‑

1中对顶电极1

‑

1裸露的焊盘部分电镀可焊金属层1

‑

3。

[0089]

本发明实施例3为实施例1引线框架的另一种制备方法,采用碱性蚀刻,与实施例2酸性蚀刻的方法相比,步骤1至4相同,区别在步骤5以后:

[0090]

5)如图17所示,第一感光膜5通过光刻制作出与底电极4

‑

1对应的、镂空的图形,第一感光膜5感光层镂空图形的镂空部分5

‑

2与底电极4

‑

1的形状对应。

[0091]

6)如图18所示,在第一感光层的镂空部分对镀铜层4的底面上电镀耐碱蚀的可焊金属层4

‑

3,耐碱蚀的可焊金属层4

‑

3可以是镀锡层、镀银层或镀金层。

[0092]

7)如图19所示,通过药液浸泡,去除第一感光膜5。

[0093]

8)如图20所示,对镀铜层4蚀刻,去除裸露的镀铜层4,在可沉铜油墨层3的下方形成底电极4

‑

1。

[0094]

9)如图21所示,将承载片12可剥离地粘贴在可沉铜油墨层3和底电极4

‑

1可焊金属层4

‑

3的底面上。

[0095]

10)如图22所示,将铜箔1顶面的承载膜2剥离,在铜箔1顶面覆盖第二感光膜6。

[0096]

11)如图23所示,第二感光膜6通过光刻制作出与顶电极1

‑

1对应的、镂空的图形,第二感光膜6感光层镂空图形的镂空部分6

‑

2与顶电极1

‑

1的形状对应。

[0097]

12)如图24所示,在第二感光层6的镂空部分6

‑

2对铜箔1的顶面、电镀耐碱蚀的可焊金属层1

‑

3,耐碱蚀的可焊金属层1

‑

3可以是镀锡层、镀银层或镀金层。

[0098]

13)如图25所示,通过药液浸泡,去除第二感光膜6。

[0099]

14)如图26所示,对铜箔1蚀刻,在可沉铜油墨层3上方形成顶电极1

‑

1。

[0100]

15)如图27所示,在可沉铜油墨层3和顶电极1

‑

1的上方印刷阻焊油墨层7。阻焊油墨层7上有与单元电路对应的窗口7

‑

1,顶电极1

‑

1的焊盘部分裸露于窗口7

‑

1中,制作出实施例1用于倒装芯片封装另一形式的引线框架。

[0101]

本发明实施例4倒装led芯片的封装结构如图16所示,包括倒装芯片8a、封装胶层9、阻焊油墨层7、两个电极和可沉铜油墨层3,电极包括顶电极1

‑

1、底电极4

‑

1和布置在可沉铜油墨层3中的第一金属化过孔4

‑

2,顶电极1

‑

1布置在可沉铜油墨层3的顶面上,底电极4

‑

1布置在可沉铜油墨层3的底面上。顶电极1

‑

1与底电极4

‑

1通过第一金属化过孔4

‑

2连接。倒装芯片8a封装在封装胶层9中,封装胶层9覆盖在阻焊油墨层7的上方,阻焊油墨层7覆盖在可沉铜油墨层3和顶电极1

‑

1的上方。阻焊油墨层7有一个窗口7

‑

1,顶电极1

‑

1的焊盘裸露于窗口7

‑

1中。顶电极1

‑

1的焊盘上镀有可焊金属层1

‑

3,倒装芯片8a布置在窗口7

‑

1上方,倒装芯片8a的两个电极分别与两个顶电极1

‑

1的焊盘焊接。

[0102]

本发明实施例5用于正装芯片封装的引线框架的结构如图36所示,实施例5与实施例1的主要区别在于,实施例5的单元电路包括一个基岛,基岛包括上基岛1

‑

2、下基岛4

‑

4和布置在可沉铜油墨层3中的第二金属化过孔4

‑

5。上基岛1

‑

2布置在可沉铜油墨层3的顶面上,下基岛4

‑

4布置在可沉铜油墨层3的底面上,上基岛1

‑

2与下基岛4

‑

4通过第二金属化过孔4

‑

5连接。承载片12还可剥离地粘贴在下基岛4

‑

4的底面上;另外,本发明实施例5的引线框架用于正装芯片封装,顶电极1

‑

1的数量多,面积小,可沉铜油墨层3和顶电极1

‑

1的上方

没有覆盖阻焊油墨层7。

[0103]

本发明实施例6为实施例5引线框架的制备方法,与实施例2的引线框架的制备方法有诸多共同点,如采用酸性蚀刻等,不同点主要有以下几点:

[0104]

1)如图28所示,在实施例2的步骤2中,在可沉铜油墨层3上形成多个过孔3

‑

1同时光刻或激光镭射出一个第二过孔3

‑

2。

[0105]

2)如图29所示,在实施例2的步骤3中,在对多个第一过孔3

‑

1电镀金属填孔同时,对第二过孔3

‑

2电镀金属填孔,形成第二金属化过孔4

‑

5。

[0106]

3)如图30所示,在镀铜层4的底面上覆盖第一感光膜5后,在实施例2的步骤5中,第一感光膜5通过光刻制作出与底电极4

‑

1及下基岛4

‑

4对应的、镂空的图形。第一感光膜5镂空图形的余留的实体部分5

‑

1与底电极4

‑

1的形状对应,5

‑

3与下基岛4

‑

4的形状对应。

[0107]

4)如图31所示,在实施例2的步骤6中,对镀铜层4蚀刻,同时在可沉铜油墨层3的下方形成底电极4

‑

1和下基岛4

‑

4。

[0108]

5)如图32所示,去除第一感光膜5后,在实施例2的步骤8中,同时在下基岛4

‑

4的裸露区域上电镀可焊金属层4

‑

3。

[0109]

6)如图33所示,在实施例2的步骤9中,承载片12同时可剥离地粘贴在下基岛4

‑

4可焊金属层4

‑

3的底面上。

[0110]

7)如图34所示,将铜箔1顶面的承载膜2剥离,在铜箔1顶面覆盖第二感光膜6后,在实施例2的步骤11中,第二感光膜6通过光刻制作出与顶电极1

‑

1对应的、镂空的实体图形6

‑

1及与上基岛1

‑

2对应的、镂空的实体图形6

‑

3,

[0111]

8)如图35所示,在实施例2的步骤12中,对铜箔1蚀刻,在可沉铜油墨层3上方同时形成顶电极1

‑

1和上基岛1

‑

2。

[0112]

9)如图36所示,去除第二感光膜6,不用印刷阻焊油墨层,在实施例2的步骤15中,对顶电极1

‑

1和上基岛1

‑

2的裸露部分分别电镀可焊金属层1

‑

3,得到实施例5的引线框架。

[0113]

本发明实施例7为实施例5引线框架的又一种制备方法,采用碱性蚀刻,与实施例6酸性蚀刻的方法相比,步骤1和2相同,但下基岛4

‑

4镀的金属层为耐碱蚀金属层。主要区别在步骤3以后:

[0114]

1)如图37所示,与实施例6步骤3不同的是,第一感光膜5通过光刻制作出镂空图形的镂空部分5

‑

2和5

‑

4分别与与底电极4

‑

1及下基岛4

‑

4的形状对应。

[0115]

2)如图38所示,在第一感光膜5的镂空部分5

‑

2和5

‑

4中对镀铜层4的底面电镀耐碱蚀的可焊金属层4

‑

3,耐碱蚀的可焊金属层可以是镀锡层、镀银层或镀金层。

[0116]

3)如图39所示,去除第一感光膜5后,对镀铜层4进行碱蚀性蚀刻,将镀铜层4底面未镀有耐碱蚀的可焊金属层、裸露的镀铜层4蚀刻掉,形成底电极4

‑

1和下基岛4

‑

4。

[0117]

4)如图40所示,将承载片12粘贴在下基岛4

‑

4可焊金属层4

‑

3的底面上、将铜箔1顶面的承载膜2剥离,在铜箔1顶面覆盖第二感光膜6后,第二感光膜6通过光刻制作出镂空图形的镂空部分6

‑

2和6

‑

4分别与顶电极1

‑

1及上基岛1

‑

2的形状对应,

[0118]

5)如图41所示,在第二感光膜6的镂空部分6

‑

2和6

‑

4中对铜箔1的顶面电镀耐碱蚀的可焊金属层1

‑

3。

[0119]

6)如图42所示,去除第二感光膜6后,对铜箔1进行碱蚀性蚀刻,将铜箔1顶面未镀有耐碱蚀的可焊金属层、裸露的铜箔1蚀刻掉,形成顶电极1

‑

1和上基岛1

‑

2。得到本发明实

施例5引线框架的另一种形式。

[0120]

本发明实施例8正装芯片的封装结构如图43所示,包括正装芯片8b、封装胶层9、基岛、多个电极和可沉铜油墨层3。多个电极布置在基岛的周边。电极包括顶电极1

‑

1、底电极4

‑

1和可沉铜油墨层3中的第一金属化过孔4

‑

2,基岛包括上基岛1

‑

2、下基岛4

‑

4和可沉铜油墨层3中的第二金属化过孔4

‑

5,上基岛1

‑

2和顶电极1

‑

1布置在可沉铜油墨层3的顶面上,下基岛4

‑

4和底电极4

‑

1布置在可沉铜油墨层3的底面上。顶电极1

‑

1与底电极4

‑

1通过第一金属化过孔4

‑

2连接,下基岛4

‑

4与上基岛1

‑

2通过第二金属化过孔4

‑

5连接。正装芯片8b的底面固定在上基岛1

‑

2的顶面上,正装芯片8b的多个电极分别通过键合线10与对应的顶电极1

‑

1的焊盘电连接。正装芯片8b和键合线10封装在封装胶层9中,封装胶层9覆盖在可沉铜油墨层3、上基岛1

‑

2和顶电极1

‑

1的上方。

[0121]

本发明以上实施例引线框架的顶电极与底电极之间有可沉铜油墨层隔开,两者仅通过金属化过孔连接,顶电极的尺寸和形状均不受底电极的限制,顶电极之间的空间较大,单元电路的布线较为方便。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。