1.本发明是有关于除错讯息提供方法,特别是指一种基本输入输出系统的除错讯息自动提供方法。

背景技术:

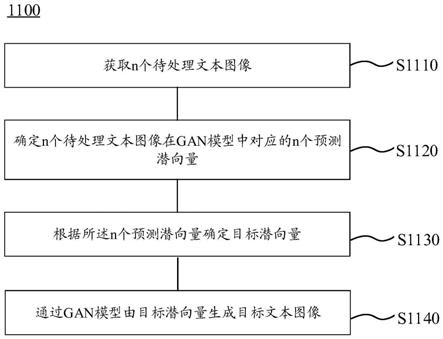

::2.传统服务器系统启动时,会透过基本输入/输出系统(bios)进行自我测试(power-onself-test,post)和初始化,若系统出现问题时,服务器会以代码的形式记录,用户往往只能根据服务器所记录的代码并需透过手动查看在基本输入输出系统规范(biosspecification)的bios开机自我测试代码表(biospostcodetable)来判断服务器系统在post阶段测试到哪个硬件后发生问题。3.然而,此种方式不仅无法立即判断服务器系统发生的问题,且若没有biospostcodetable可以查看,使用者仅透过蜂鸣代码(beepcode)或是根据经验猜测哪个硬件出问题,非常费时且无法准确判断问题点而造成误判。技术实现要素:4.本发明要解决的技术问题是提供一种能实时提供除错讯息的基本输入输出系统的除错讯息自动提供方法。5.为解决上述技术问题,本发明基本输入输出系统的除错讯息自动提供方法,借由一计算机装置执行,该计算机装置包括一内存及一电连接该内存的处理单元,该处理单元执行多个分别相关于多个待驱动硬件的驱动程序,每一驱动程序包括多个第一除错指令,该方法包含一步骤(a)、一步骤(b),及一步骤(c)。6.在该步骤(a)中,在该处理单元执行到一驱动程序的一第一除错指令时,根据该第一除错指令产生一对应该驱动程序所对应的待驱动硬件且包括一第一状态描述的第一除错讯息。7.在该步骤(b)中,该处理单元将该第一除错讯息储存至该内存。8.在该步骤(c)中,该处理单元判定是否发生一满足一驱动默认条件的驱动错误,当该处理单元判定出发生该驱动错误时,该处理单元输出该内存所储存的所有第一除错讯息。9.相较于现有技术,本发明的处理单元将该第一除错讯息储存至该内存,并在判定出发生该驱动错误时自动输出该内存所储存的所有第一除错讯息,以让用户能立即根据该等第一除错讯息准确判断出问题点。10.【附图说明】本发明的其他的特征及功效,将于参照图式的实施方式中清楚地呈现,其中:图1是一方块图,示例说明一计算机装置,其用来实施本发明基本输入输出系统的除错讯息自动提供方法之一实施例;图2是一流程图,说明该实施例在pei阶段执行的步骤;及图3是一流程图,说明该实施例在dxe阶段执行的步骤。11.【具体实施方式】参阅图1,说明了一用来实施本发明实施例的一种基本输入输出系统的除错讯息自动提供方法的计算机装置1。例如,该计算机装置1包含一显示单元11、一内存12、一基板管理控制器(baseboardmanagementcontroller,bmc)13、一处理单元14,及一电连接该显示单元11、该内存12、该基板管理控制器13,及该处理单元14的平台路径控制器(platformcontrollerhub,pch)15。值得注意的是,在其他实施方式中,该处理单元14及该平台路径控制器15亦可整合为系统单芯片(systemonachip,soc),该系统单芯片电连接该显示单元11、该内存12,及该基板管理控制器13,此外,在其他实施方式中,该显示单元11亦可以外接的方式,连接该计算机装置1。12.该内存12例如为非挥发性内存(non-volatilememory,nvm),但不以此为限。13.该基板管理控制器13包括一与一使用端2通讯连接的串行端口(serialport)131,该基板管理控制器13储存一用于设定该串行端口131的默认连接参数。值得注意的是,该串行端口131可为该基板管理控制器13的输出埠,该基板管理控制器13电连接主板上预留之连接器(connector),以用于电连接除错工具板(debugtoolboard),并外接外部计算机,或是外接通讯端口(communicationport);该串行端口131亦可设置于该基板管理控制器13外部而为主板上预留之连接器或是用于外接的通讯端口。14.该处理单元14包括一快取(cache)141,该处理单元14执行统一的可扩展固件接口(unifiedextensiblefirmwareinterface,uefi)系统,并在可扩展固件接口前期初始化(pre-extensiblefirmwareinterfaceinitialization,以下简称pei)环境阶段下,在该计算机装置1刚进入可扩展固件接口前期初始化环境阶段时,该内存12尚未完成初始化而无法被使用,执行多个分别相关于多个待初始硬件的pei初始化程序,并在驱动执行环境(driverexecutionenvironment,以下简称dxe)阶段下,及多个分别相关于多个待驱动硬件的dxe驱动程序,每一pei初始化程序包括多个pei除错指令,每一dxe驱动程序包括多个dxe除错指令,以进行uefi系统的开机程序。值得注意的是,该快取141例如为静态随机存取内存(staticrandomaccessmemory,sram),该快取141保持通电时,里面储存的数据恒常保持;而当电力供应停止时,该快取141储存的数据会消失(即挥发性内存),该等待初始硬件例如为中央处理器、平台路径控制器、内存、主板,该等待驱动硬件例如为通用串行总线(universalserialbus,usb)、键盘、pci总线、pciscsi主机控制器(hostcontroller)、启动整体服务(bootintegrityservice,bis)、pci主桥(pcihostbridge)。15.参阅图1、图2、与图3,示例说明了该计算机装置1在执行uefi系统的开机程序的过程中,如何实施本发明实施例一种基本输入输出系统的除错讯息自动提供方法,该实施例包含在pei阶段执行的步骤201~212,及在dxe阶段执行的步骤301~309。在此实施例中,例如总共有m个pei除错指令,n个dxe除错指令,其中m>1,n>1,而该处理单元14在pei阶段将依序执行该等pei初始化程序,并在执行每一pei初始化程序期间依序执行该pei初始化程序的该等pei除错指令;而该处理单元14在dxe阶段将依序执行该等dxe驱动程序,并在执行每一dxe驱动程序期间依序执行该dxe驱动程序的该等dxe除错指令。16.在步骤201中,初始时,该处理单元14执行第1个pei除错指令,也就是i=1。17.在步骤202中,该处理单元14根据第i个pei除错指令产生一对应该pei初始化程序所对应的待初始硬件的第i个pei除错讯息。值得注意的是,在本实施例中,每一pei除错讯息包括一pei除错码,在其他实施方式中,每一pei除错讯息包括一pei状态描述,该pei状态指示出例如指出对应待初始硬件的初始化状态。18.在步骤203中,该处理单元14将该第i个pei除错讯息储存至该快取141。值得注意的是,在本实施例中,该处理单元14系透过hand-offblocks(hob)将该pei除错讯息储存至该快取141,但不以此为限。19.在步骤204中,该处理单元14判定是否发生一满足一初始化预设条件的初始化错误,当该处理单元14判定出发生该初始化错误时,流程进行步骤205;当该处理单元14判定出未发生该初始化错误时,则流程进行步骤208。值得注意的是,该初始化预设条件例如为cpuinstance为空值(null)、stacktop为空值,及gdtbuffer为空值等,但不以此为限。20.在步骤205中,该处理单元14经由该平台路径控制器15输出该快取141所储存的所有pei除错讯息至该基板管理控制器13。21.在步骤206中,该处理单元14传送一第一更新连接参数至该基板管理控制器13。22.在步骤207中,该基板管理控制器13在接收到该处理单元14输出的所有pei除错讯息后,根据该第一更新连接参数更新该预设连接参数,并经由该串行端口131传送该等pei除错讯息至该使用端2。要特别注意的是,在其他实施方式中,该预设连接参数亦可用于设定该基板管理控制器13的局域网络串行端口(serialoverlan,sol),该基板管理控制器13亦可经由该sol传送该等pei除错讯息至该使用端2。23.在步骤208中,该处理单元14判定该第i个pei除错指令是否为第m个pei除错指令,亦即判断是否i=m。当判定该第i个pei除错指令为第m个pei除错指令时,流程结束;当判定该第i个pei除错指令不为第m个pei除错指令时,流程进行步骤209。24.在步骤209中,该处理单元14执行第(i 1)个pei除错指令,亦即将i设为i 1。之后,重复步骤202~204直到i=m。25.在步骤210中,当该处理单元14接收到一中断讯号时,该处理单元14停止执行该等pei初始化程序,并自动输出该快取141所储存的所有pei除错讯息至该基板管理控制器13。值得注意的是,该中断讯号可由该处理单元14或是由其他硬件产生,不以此为限。26.在步骤211中,该处理单元14经由该平台路径控制器15传送一第二更新连接参数至该基板管理控制器13。27.在步骤212中,该基板管理控制器13在接收到该处理单元14输出的所有pei除错讯息后,根据该第二更新连接参数更新该预设连接参数,并经由该串行端口131传送所接收到的该等pei除错讯息至该使用端2。28.要特别注意的是,在本实施例中,步骤206在步骤205之后,步骤212在步骤211,在其他实施方式中,步骤206可在步骤205之前或同时进行,步骤212可在步骤211之前或同时进行,不以此为限。29.要再特别注意的是,步骤210~212可在步骤201~209之其中一者之后执行,在执行uefibios系统的开机程序的过程中,当uefibios系统发生不正常的错误导致无法继续执行该uefi系统的时候,该处理单元14会接收到该中断讯号,以进行步骤210~212,即进行例外处理(exceptionhandling)。值得注意的是,由于本发明之特征并不在于熟知此技艺者所已知的该处理单元14如何判断该uefi系统是否发生错误,为了简洁,故在此省略了他们的细节。30.在步骤301中,该处理单元14将该快取141所储存的所有第二除错讯息储存至该内存12。值得注意的是,该内存12在pei阶段(步骤201~212)执行初始化后,才执行步骤301。31.在步骤302中,初始时,该处理单元14执行第1个dxe除错指令,也就是j=1。32.在步骤303中,该处理单元14根据第j个dxe除错指令产生一对应该dxe驱动程序所对应的待驱动硬件且包括一dxe状态描述的第j个dxe除错讯息。值得注意的是,在本实施例中,每一dxe除错讯息包括一dxe除错码,在其他实施方式中,每一dxe除错讯息包括一dxe状态描述,该dxe状态描述例如描述对应待驱动硬件的韧体状态。33.在步骤304中,该处理单元14将该第j个dxe除错讯息储存至该内存12。34.在步骤305中,该处理单元14判定是否发生发生一满足一驱动默认条件的驱动错误,当该处理单元14判定出发生该驱动错误时,流程进行步骤306;当该处理单元14判定出未发生该驱动错误时,则流程进行步骤307。值得注意的是,该驱动默认条件例如为tempstring为空值、newstring为空值,及guidhob为空值等,但不以此为限。35.在步骤306中,该处理单元14经由该平台路径控制器15输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11。36.在步骤307中,该处理单元14判定该第i个dxe除错指令是否为第n个dxe除错指令,亦即判断是否j=n。当判定该第j个dxe除错指令为第n个dxe除错指令时,流程结束;当判定该第j个dxe除错指令不为第n个dxe除错指令时,流程进行步骤308。37.在步骤308中,该处理单元14执行第(j 1)个pei除错指令,亦即将i设为j 1。之后,重复步骤303~305直到j=n。38.在步骤309中,当该处理单元14接收到一中断讯号时,该处理单元14停止执行该等dxe驱动程序,并输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11。39.要特别注意的是,步骤309可在步骤301~308之其中一者之后执行,当uefibios系统发生不正常的错误导致无法继续执行该uefi系统的时候,该处理单元14会接收到该中断讯号,以进行步骤309,即进行例外处理。40.综上所述,本发明基本输入输出系统的除错讯息自动提供方法,在pei阶段,由于该内存12还不能使用,故借由该处理单元14将该等pei除错讯息储存至该快取141,并在该处理单元14判定出发生该初始化错误时,自动输出该快取141所储存的所有pei除错讯息至该基板管理控制器13,以致该基板管理控制器13传送该等pei除错讯息至该使用端2,让使用者能在pei阶段即能根据该等pei除错讯息准确判断出问题点;在dxe阶段,借由该处理单元14将该等pei除错讯息及该等dxe除错讯息储存至该内存12,并在该处理单元14判定出发生该驱动错误时,该处理单元14自动输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11,以让用户能立即根据该等pei除错讯息及该等dxe除错讯息准确判断出问题点,故确实能达成本发明的目的。41.惟以上所述者,仅为本发明的实施例而已,当不能以此限定本发明实施的范围,凡是依本发明权利要求书及专利说明书内容所作的简单的等效变化与修饰,皆仍属本发明专利涵盖的范围内。当前第1页12当前第1页12

背景技术:

::2.传统服务器系统启动时,会透过基本输入/输出系统(bios)进行自我测试(power-onself-test,post)和初始化,若系统出现问题时,服务器会以代码的形式记录,用户往往只能根据服务器所记录的代码并需透过手动查看在基本输入输出系统规范(biosspecification)的bios开机自我测试代码表(biospostcodetable)来判断服务器系统在post阶段测试到哪个硬件后发生问题。3.然而,此种方式不仅无法立即判断服务器系统发生的问题,且若没有biospostcodetable可以查看,使用者仅透过蜂鸣代码(beepcode)或是根据经验猜测哪个硬件出问题,非常费时且无法准确判断问题点而造成误判。技术实现要素:4.本发明要解决的技术问题是提供一种能实时提供除错讯息的基本输入输出系统的除错讯息自动提供方法。5.为解决上述技术问题,本发明基本输入输出系统的除错讯息自动提供方法,借由一计算机装置执行,该计算机装置包括一内存及一电连接该内存的处理单元,该处理单元执行多个分别相关于多个待驱动硬件的驱动程序,每一驱动程序包括多个第一除错指令,该方法包含一步骤(a)、一步骤(b),及一步骤(c)。6.在该步骤(a)中,在该处理单元执行到一驱动程序的一第一除错指令时,根据该第一除错指令产生一对应该驱动程序所对应的待驱动硬件且包括一第一状态描述的第一除错讯息。7.在该步骤(b)中,该处理单元将该第一除错讯息储存至该内存。8.在该步骤(c)中,该处理单元判定是否发生一满足一驱动默认条件的驱动错误,当该处理单元判定出发生该驱动错误时,该处理单元输出该内存所储存的所有第一除错讯息。9.相较于现有技术,本发明的处理单元将该第一除错讯息储存至该内存,并在判定出发生该驱动错误时自动输出该内存所储存的所有第一除错讯息,以让用户能立即根据该等第一除错讯息准确判断出问题点。10.【附图说明】本发明的其他的特征及功效,将于参照图式的实施方式中清楚地呈现,其中:图1是一方块图,示例说明一计算机装置,其用来实施本发明基本输入输出系统的除错讯息自动提供方法之一实施例;图2是一流程图,说明该实施例在pei阶段执行的步骤;及图3是一流程图,说明该实施例在dxe阶段执行的步骤。11.【具体实施方式】参阅图1,说明了一用来实施本发明实施例的一种基本输入输出系统的除错讯息自动提供方法的计算机装置1。例如,该计算机装置1包含一显示单元11、一内存12、一基板管理控制器(baseboardmanagementcontroller,bmc)13、一处理单元14,及一电连接该显示单元11、该内存12、该基板管理控制器13,及该处理单元14的平台路径控制器(platformcontrollerhub,pch)15。值得注意的是,在其他实施方式中,该处理单元14及该平台路径控制器15亦可整合为系统单芯片(systemonachip,soc),该系统单芯片电连接该显示单元11、该内存12,及该基板管理控制器13,此外,在其他实施方式中,该显示单元11亦可以外接的方式,连接该计算机装置1。12.该内存12例如为非挥发性内存(non-volatilememory,nvm),但不以此为限。13.该基板管理控制器13包括一与一使用端2通讯连接的串行端口(serialport)131,该基板管理控制器13储存一用于设定该串行端口131的默认连接参数。值得注意的是,该串行端口131可为该基板管理控制器13的输出埠,该基板管理控制器13电连接主板上预留之连接器(connector),以用于电连接除错工具板(debugtoolboard),并外接外部计算机,或是外接通讯端口(communicationport);该串行端口131亦可设置于该基板管理控制器13外部而为主板上预留之连接器或是用于外接的通讯端口。14.该处理单元14包括一快取(cache)141,该处理单元14执行统一的可扩展固件接口(unifiedextensiblefirmwareinterface,uefi)系统,并在可扩展固件接口前期初始化(pre-extensiblefirmwareinterfaceinitialization,以下简称pei)环境阶段下,在该计算机装置1刚进入可扩展固件接口前期初始化环境阶段时,该内存12尚未完成初始化而无法被使用,执行多个分别相关于多个待初始硬件的pei初始化程序,并在驱动执行环境(driverexecutionenvironment,以下简称dxe)阶段下,及多个分别相关于多个待驱动硬件的dxe驱动程序,每一pei初始化程序包括多个pei除错指令,每一dxe驱动程序包括多个dxe除错指令,以进行uefi系统的开机程序。值得注意的是,该快取141例如为静态随机存取内存(staticrandomaccessmemory,sram),该快取141保持通电时,里面储存的数据恒常保持;而当电力供应停止时,该快取141储存的数据会消失(即挥发性内存),该等待初始硬件例如为中央处理器、平台路径控制器、内存、主板,该等待驱动硬件例如为通用串行总线(universalserialbus,usb)、键盘、pci总线、pciscsi主机控制器(hostcontroller)、启动整体服务(bootintegrityservice,bis)、pci主桥(pcihostbridge)。15.参阅图1、图2、与图3,示例说明了该计算机装置1在执行uefi系统的开机程序的过程中,如何实施本发明实施例一种基本输入输出系统的除错讯息自动提供方法,该实施例包含在pei阶段执行的步骤201~212,及在dxe阶段执行的步骤301~309。在此实施例中,例如总共有m个pei除错指令,n个dxe除错指令,其中m>1,n>1,而该处理单元14在pei阶段将依序执行该等pei初始化程序,并在执行每一pei初始化程序期间依序执行该pei初始化程序的该等pei除错指令;而该处理单元14在dxe阶段将依序执行该等dxe驱动程序,并在执行每一dxe驱动程序期间依序执行该dxe驱动程序的该等dxe除错指令。16.在步骤201中,初始时,该处理单元14执行第1个pei除错指令,也就是i=1。17.在步骤202中,该处理单元14根据第i个pei除错指令产生一对应该pei初始化程序所对应的待初始硬件的第i个pei除错讯息。值得注意的是,在本实施例中,每一pei除错讯息包括一pei除错码,在其他实施方式中,每一pei除错讯息包括一pei状态描述,该pei状态指示出例如指出对应待初始硬件的初始化状态。18.在步骤203中,该处理单元14将该第i个pei除错讯息储存至该快取141。值得注意的是,在本实施例中,该处理单元14系透过hand-offblocks(hob)将该pei除错讯息储存至该快取141,但不以此为限。19.在步骤204中,该处理单元14判定是否发生一满足一初始化预设条件的初始化错误,当该处理单元14判定出发生该初始化错误时,流程进行步骤205;当该处理单元14判定出未发生该初始化错误时,则流程进行步骤208。值得注意的是,该初始化预设条件例如为cpuinstance为空值(null)、stacktop为空值,及gdtbuffer为空值等,但不以此为限。20.在步骤205中,该处理单元14经由该平台路径控制器15输出该快取141所储存的所有pei除错讯息至该基板管理控制器13。21.在步骤206中,该处理单元14传送一第一更新连接参数至该基板管理控制器13。22.在步骤207中,该基板管理控制器13在接收到该处理单元14输出的所有pei除错讯息后,根据该第一更新连接参数更新该预设连接参数,并经由该串行端口131传送该等pei除错讯息至该使用端2。要特别注意的是,在其他实施方式中,该预设连接参数亦可用于设定该基板管理控制器13的局域网络串行端口(serialoverlan,sol),该基板管理控制器13亦可经由该sol传送该等pei除错讯息至该使用端2。23.在步骤208中,该处理单元14判定该第i个pei除错指令是否为第m个pei除错指令,亦即判断是否i=m。当判定该第i个pei除错指令为第m个pei除错指令时,流程结束;当判定该第i个pei除错指令不为第m个pei除错指令时,流程进行步骤209。24.在步骤209中,该处理单元14执行第(i 1)个pei除错指令,亦即将i设为i 1。之后,重复步骤202~204直到i=m。25.在步骤210中,当该处理单元14接收到一中断讯号时,该处理单元14停止执行该等pei初始化程序,并自动输出该快取141所储存的所有pei除错讯息至该基板管理控制器13。值得注意的是,该中断讯号可由该处理单元14或是由其他硬件产生,不以此为限。26.在步骤211中,该处理单元14经由该平台路径控制器15传送一第二更新连接参数至该基板管理控制器13。27.在步骤212中,该基板管理控制器13在接收到该处理单元14输出的所有pei除错讯息后,根据该第二更新连接参数更新该预设连接参数,并经由该串行端口131传送所接收到的该等pei除错讯息至该使用端2。28.要特别注意的是,在本实施例中,步骤206在步骤205之后,步骤212在步骤211,在其他实施方式中,步骤206可在步骤205之前或同时进行,步骤212可在步骤211之前或同时进行,不以此为限。29.要再特别注意的是,步骤210~212可在步骤201~209之其中一者之后执行,在执行uefibios系统的开机程序的过程中,当uefibios系统发生不正常的错误导致无法继续执行该uefi系统的时候,该处理单元14会接收到该中断讯号,以进行步骤210~212,即进行例外处理(exceptionhandling)。值得注意的是,由于本发明之特征并不在于熟知此技艺者所已知的该处理单元14如何判断该uefi系统是否发生错误,为了简洁,故在此省略了他们的细节。30.在步骤301中,该处理单元14将该快取141所储存的所有第二除错讯息储存至该内存12。值得注意的是,该内存12在pei阶段(步骤201~212)执行初始化后,才执行步骤301。31.在步骤302中,初始时,该处理单元14执行第1个dxe除错指令,也就是j=1。32.在步骤303中,该处理单元14根据第j个dxe除错指令产生一对应该dxe驱动程序所对应的待驱动硬件且包括一dxe状态描述的第j个dxe除错讯息。值得注意的是,在本实施例中,每一dxe除错讯息包括一dxe除错码,在其他实施方式中,每一dxe除错讯息包括一dxe状态描述,该dxe状态描述例如描述对应待驱动硬件的韧体状态。33.在步骤304中,该处理单元14将该第j个dxe除错讯息储存至该内存12。34.在步骤305中,该处理单元14判定是否发生发生一满足一驱动默认条件的驱动错误,当该处理单元14判定出发生该驱动错误时,流程进行步骤306;当该处理单元14判定出未发生该驱动错误时,则流程进行步骤307。值得注意的是,该驱动默认条件例如为tempstring为空值、newstring为空值,及guidhob为空值等,但不以此为限。35.在步骤306中,该处理单元14经由该平台路径控制器15输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11。36.在步骤307中,该处理单元14判定该第i个dxe除错指令是否为第n个dxe除错指令,亦即判断是否j=n。当判定该第j个dxe除错指令为第n个dxe除错指令时,流程结束;当判定该第j个dxe除错指令不为第n个dxe除错指令时,流程进行步骤308。37.在步骤308中,该处理单元14执行第(j 1)个pei除错指令,亦即将i设为j 1。之后,重复步骤303~305直到j=n。38.在步骤309中,当该处理单元14接收到一中断讯号时,该处理单元14停止执行该等dxe驱动程序,并输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11。39.要特别注意的是,步骤309可在步骤301~308之其中一者之后执行,当uefibios系统发生不正常的错误导致无法继续执行该uefi系统的时候,该处理单元14会接收到该中断讯号,以进行步骤309,即进行例外处理。40.综上所述,本发明基本输入输出系统的除错讯息自动提供方法,在pei阶段,由于该内存12还不能使用,故借由该处理单元14将该等pei除错讯息储存至该快取141,并在该处理单元14判定出发生该初始化错误时,自动输出该快取141所储存的所有pei除错讯息至该基板管理控制器13,以致该基板管理控制器13传送该等pei除错讯息至该使用端2,让使用者能在pei阶段即能根据该等pei除错讯息准确判断出问题点;在dxe阶段,借由该处理单元14将该等pei除错讯息及该等dxe除错讯息储存至该内存12,并在该处理单元14判定出发生该驱动错误时,该处理单元14自动输出该内存12所储存的所有pei除错讯息及所有dxe除错讯息至该显示单元11,以让用户能立即根据该等pei除错讯息及该等dxe除错讯息准确判断出问题点,故确实能达成本发明的目的。41.惟以上所述者,仅为本发明的实施例而已,当不能以此限定本发明实施的范围,凡是依本发明权利要求书及专利说明书内容所作的简单的等效变化与修饰,皆仍属本发明专利涵盖的范围内。当前第1页12当前第1页12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。