基于dma的高速ad采样数据传输方法、设备、介质、产品及装置

技术领域

1.本发明涉及嵌入式设备高速ad采样技术领域,尤其涉及基于dma的高速ad采样数据传输方法、设备、介质、产品及装置。

背景技术:

2.当前市场上常用的高速ad采样芯片大部分都是adi公司的adc系列,然而市场上常见的微处理器都没有提供与adc系列的ad采样芯片匹配的数据传输接口。现在市场上常用的方案是使用微处理器的gpio接口模拟adc系列的ad采样芯片并行接口进行数据传输。这种方案会占用cpu的大量资源,导致微处理器的性能下降,甚至需要增加额外的处理器进行其他业务处理,导致开发成本和物料成本的增加。

技术实现要素:

3.为了克服现有技术的不足,本发明的目的在于提供基于dma的高速ad采样数据传输方法,借助处理器片内外设,即定时器、dma(直接存储器访问)和dmamux(直接存储器访问请求复用器),配合gpio接口,模拟adc系列的ad采样芯片并行接口实现高速ad数据传输。

4.本发明提供基于dma的高速ad采样数据传输方法,包括以下步骤:

5.配置定时器参数,将微处理器的定时器配置为通过输出通道上升沿捕获模式;

6.配置直接存储器访问参数,将微处理器的直接存储器访问的数据流配置目的地址指向一块内存、源地址指定通用输入输出端口的输入数据寄存器、请求线设置为直接存储器访问采集定时器输出通道的数据;

7.启动设备,启动所述定时器和所述直接存储器访问,并触发ad采样芯片进行自动连续采样;

8.采样数据,当ad采样芯片每完成一次采样时,ad采样芯片将采样数据通过数据引脚输出,同时在时钟信号引脚输出脉冲信号,所述定时器捕获输出通道的上升沿,并使用该信号驱动直接存储器访问的数据流从通用输入输出端口的输入数据寄存器读取一组数据并存储到直接存储器访问的数据流指定的内存,完成一次ad采样;

9.循环采样,循环执行所述采样数据步骤,直到完成预设采样次数,所述直接存储器访问触发完成中断,关闭所述定时器和直接存储器访问,并停止ad采样芯片采样。

10.进一步地,所述配置定时器参数步骤中,将微处理器的第一定时器配置为通过第一输出通道上升沿捕获模式。

11.进一步地,所述配置直接存储器访问参数步骤中,将微处理器的第二直接存储器访问的第一数据流配置目的地址指向一块内存、源地址指定通用输入输出端口的输入数据寄存器、请求线设置为直接存储器访问采集第一定时器第一输出通道的数据。

12.一种电子设备,包括:处理器;

13.存储器;以及程序,其中所述程序被存储在所述存储器中,并且被配置成由处理器执行,所述程序包括用于执行基于dma的高速ad采样数据传输方法。

14.一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行基于dma的高速ad采样数据传输方法。

15.一种计算机程序产品,包括计算机程序/指令,该计算机程序/指令被处理器执行时实现基于dma的高速ad采样数据传输方法。

16.基于dma的高速ad采样数据传输装置,包括微处理器和ad采样芯片,所述微处理器的定时器的输出通道与所述ad采样芯片的时钟信号引脚连接,所述微处理器的定时器配置的通用输入输出口与所述ad采样芯片的数据引脚连接。

17.进一步地,所述微处理器的第一定时器的第一输出通道与所述ad采样芯片的时钟信号引脚连接。

18.进一步地,所述微处理器为stm32系列微处理器,所述ad采样芯片为adc系列采样芯片。

19.进一步地,所述stm32系列微处理器的第一至第十二通用输入输出引脚与所述ad采样芯片的第一至第十二数据引脚连接,所述stm32系列微处理器的第十三至第十五通用输入输出引脚接地。

20.相比现有技术,本发明的有益效果在于:

21.本发明借助微处理器中拥有信号捕获能力的定时器、dma(直接存储器访问)和dmamux(直接存储器访问请求复用器)三种片内外设,配合gpio接口,模拟adc系列的ad采样芯片并行接口实现高速ad数据传输。可以通过dma将ad采样数据直接传输到微处理的内存中,大大降低cpu资源的占用,节约了开发成本和物料成本,提高了数据传输的稳定性、正确性。

22.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,并可依照说明书的内容予以实施,以下以本发明的较佳实施例并配合附图详细说明如后。本发明的具体实施方式由以下实施例及其附图详细给出。

附图说明

23.此处所说明的附图用来提供对本发明的进一步理解,构成本技术的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

24.图1为本发明的基于dma的高速ad采样数据传输装置原理图;

25.图2为本发明的信号时序图;

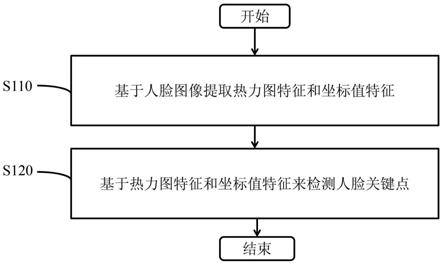

26.图3为本发明的基于dma的高速ad采样数据传输方法流程图;

27.图4为本发明实施例的高速ad采样数据传输方法流程图。

具体实施方式

28.下面,结合附图以及具体实施方式,对本发明做进一步描述,需要说明的是,在不相冲突的前提下,以下描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例。

29.基于dma的高速ad采样数据传输装置,包括微处理器和ad采样芯片,微处理器的定时器的输出通道与ad采样芯片的时钟信号引脚连接,微处理器的定时器配置的通用输入输出口与ad采样芯片的数据引脚连接。

30.如图1所示,微处理器为stm32系列微处理器,具体为stm32h753微处理器,ad采样芯片为adc系列采样芯片,具体为ad9629芯片。ad采样芯片ad9629的并行接口包含一个时钟信号引脚dco和12个数据引脚d0~d11。每完成一次采样,ad9629会在dco引脚输出一个脉冲,同时将采样数据输出到d0~d11引脚,如图2所示。ad9629芯片的时钟信号引脚dco与stm32h753微处理器的第一定时器tim1的第一输出通道ch1相连,ad9629芯片的第一至第十二数据引脚d0~d11与stm32h753微处理器的第一至第十二通用输入输出引脚gpiog0~gpiog11相连。stm32h753微处理器的第十三至第十五通用输入输出引脚gpiog12~gpio15接地。

31.stm32h753微处理器配置如下:

32.1、第一定时器tim1配置为通过第一输出通道ch1上升沿捕获模式;

33.2、第二直接存储器访问dma2的第一数据流stream0配置目的地址指向一块内存;

34.3、第二直接存储器访问dma2的第一数据流stream0配置源地址指定gpiog的idr寄存器(通用输入输出端口的输入数据寄存器);

35.4、第二直接存储器访问dma2的第一数据流stream0配置请求线设置为dma_request_tim1_ch1(第二直接存储器访问dma2采集第一定时器tim1第一输出通道ch1的数据)。

36.基于dma的高速ad采样数据传输方法,基于上述高速ad采样数据传输装置实现,如图3所示,包括以下步骤:

37.配置定时器参数,将微处理器的定时器配置为通过输出通道上升沿捕获模式。本实施例中,将stm32h753微处理器的第一定时器tim1配置为通过第一输出通道ch1上升沿捕获模式。

38.配置直接存储器访问参数,将微处理器的直接存储器访问的数据流配置目的地址指向一块内存、源地址指定通用输入输出端口的输入数据寄存器、请求线设置为直接存储器访问采集定时器输出通道的数据。本实施例中,将stm32h753微处理器的第二直接存储器访问dma2的第一数据流stream0配置目的地址指向一块内存,将stm32h753微处理器的第二直接存储器访问dma2的第一数据流stream0配置源地址指定通用输入输出端口的输入数据寄存器(gpiog的idr寄存器),将stm32h753微处理器的第二直接存储器访问dma2的第一数据流stream0配置请求线设置为直接存储器访问采集第一定时器第一输出通道的数据(dma_request_tim1_ch1)。

39.启动设备,启动定时器和直接存储器访问,并触发ad采样芯片进行自动连续采样;

40.采样数据,当ad采样芯片每完成一次采样时,ad采样芯片将采样数据通过数据引脚输出,同时在时钟信号引脚输出脉冲信号,定时器捕获输出通道的上升沿,并使用该信号驱动直接存储器访问的数据流从通用输入输出端口的输入数据寄存器读取一组数据并存储到直接存储器访问的数据流指定的内存,完成一次ad采样;

41.循环采样,循环执行采样数据步骤,直到完成预设采样次数,直接存储器访问触发完成中断,关闭定时器和直接存储器访问,并停止ad采样芯片采样。

42.如图4所示,若需要连续进行1024次采样,那么dma2的stream0配置目的地址指向的内存空间的大小应为16位*1024=2048字节。采样开始,启动tim1和dma2,并触发ad9629芯片进行自动连续采样。ad每完成一次采样,会将采样数据通过d0~d11输出,同时在dco线

输出一个脉冲信号。tim1捕获ch1的上升沿,并使用该信号驱动dma2的stream0从gpiog端口的输入数据寄存器读取一组数据(2字节)并存储到dma2的stream0指定的内存,一次ad采样完成。

43.由于ad9629被配置为自动连续采样,因此采样工作会自动循环,直到第1024次完成,dma2会触发完成中断,在这里关闭tim1和dma2,并停止ad9629芯片采样。

44.本发明巧妙使用微处理器的dma和tim,实现基于dma的高速ad采样数据传输。由于adi公司的adc系列芯片的并行接口是由一个信号引脚和一组数据引脚组成,每次采样完成,都会将采样数据输出到这一组并行数据引脚上,同时会在信号引脚上产生一个脉冲。因此,借助微处理器的dma和tim,使用tim捕获信号引脚上的脉冲,然后使用该信号驱动dma读取并行数据引脚上的数据并存储到内存中,由于dma的目的地址可以配置成自动增加,进而实现了连续ad采样。

45.一种电子设备,包括:处理器;

46.存储器;以及程序,其中程序被存储在存储器中,并且被配置成由处理器执行,程序包括用于执行基于dma的高速ad采样数据传输方法。

47.一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行基于dma的高速ad采样数据传输方法。

48.一种计算机程序产品,包括计算机程序/指令,该计算机程序/指令被处理器执行时实现基于dma的高速ad采样数据传输方法。

49.以上,仅为本发明的较佳实施例而已,并非对本发明作任何形式上的限制;凡本行业的普通技术人员均可按说明书附图所示和以上而顺畅地实施本发明;但是,凡熟悉本专业的技术人员在不脱离本发明技术方案范围内,利用以上所揭示的技术内容而做出的些许更动、修饰与演变的等同变化,均为本发明的等效实施例;同时,凡依据本发明的实质技术对以上实施例所作的任何等同变化的更动、修饰与演变等,均仍属于本发明的技术方案的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。