技术特征:

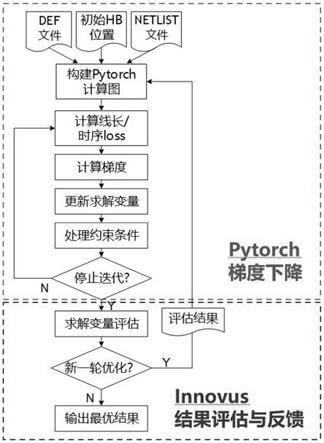

1.一种三维集成电路片间混合键合布局布线优化方法,用于优化调整面对面堆叠的两个裸片之间混合键合位置、和/或优化调整两个裸片各自标准单元位置,使得三维集成电路片间混合键合布局布线最优,其特征在于包括以下步骤:s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路布局片间混合键合布线计算图模型;s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解片间混合键合最佳位置或者新一轮迭代片间混合键合位置;具体地,s21、计算包含片间混合键合位置的目标待测量损失函数;s22、计算包含片间混合键合位置的目标待测量损失函数相应的梯度函数;s23、更新片间混合键合位置;s24、根据约束条件优化调整片间混合键合位置;s25、获得优化调整后的片间混合键合位置,执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3

‑

1;或者获得片间混合键合最佳位置,执行步骤s3

‑

2;s3

‑

1、分析反馈程序模块根据步骤s2迭代求解产生新一轮迭代片间混合键合位置,利用数字集成电路设计平台优化调整三维集成电路两个裸片各自标准单元位置生成三维集成电路片间混合键合布局布线中间文件,对三维集成电路片间混合键合布局布线的真实目标待测量进行评估分析,如果真实目标待测量不满足整体最优要求,执行步骤s1;或者如果真实目标待测量满足整体最优要求,执行步骤s4;或者s3

‑

2、分析反馈程序模块根据步骤s2迭代求解产生的片间混合键合最佳位置,利用数字集成电路设计平台生成目标待测量整体最优的三维集成电路片间混合键合布局布线文件;s4、分析反馈程序模块利用数字集成电路设计平台输出真实目标待测量整体最优的三维集成电路片间混合键合布局布线文件。2.根据权利要求1所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:步骤s2所述目标待测量是全局总线长、和/或建立时间松弛;所述全局总线长是指三维集成电路片间混合键合布局布线中片间混合键合和与所述片间混合键合相连的第一级标准单元管脚的曼哈顿距离的总和;所述建立时间松弛是指三维集成电路片间混合键合布局布线中每条时序通路时钟松弛,采用片间混合键合位置布局布线后真实的时钟松弛减去估测曼哈顿线长延时参数进行估测。3.根据权利要求2所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:当目标待测量为全局总线长时,全局总线长损失函数为三维集成电路片间混合键合布局布线中所有线的曼哈顿距离之和:

其中(x

i

,y

i

)是标准单元布局位置(x

std

,y

std

),(x

hb

,y

hb

)是片间混合键合布局位置;当目标待测量为建立时间松弛时,每条时序通路时间松弛损失函数为:loss

path

其中slack

initial

是当前片间混合键合位置布局布线后真实的时钟松弛,β是单位曼哈顿距离引发的线延时。4.根据权利要求3所述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局固定三维集成电路片间混合键合布局布线优化方法,目标待测量是全局总线长,用于两个裸片上标准单元布局位置固定不变,确定混合键合位置;其特征在于包括以下步骤:s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解片间混合键合最佳位置;具体地,s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的全局总线长损失函数;s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的全局总线长损失函数相应的梯度函数;s23、更新片间混合键合位置坐标(x

hb

,y

hb

);s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;每几轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都处理片间混合键合位置坐标(x

hb

,y

hb

)对齐、防止出现片间混合键合位置坐标(x

hb

,y

hb

)冲突;s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得片间混合键合最佳位置,执行步骤s3;s3、分析反馈程序模块根据步骤s2迭代求解产生的片间混合键合最佳位置,利用数字集成电路设计平台生成全局总线长整体最优的三维集成电路片间混合键合布局布线文件;s4、分析反馈程序模块利用数字集成电路设计平台输出全局总线长整体最优的三维集成电路片间混合键合布局布线文件。5.根据权利要求3所述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局固定、时序优先三维集成电路片间混合键合布局布线优化方法,目标待测量是建立时间松弛,用于两个裸片上标准单元布局位置固定不变,确定混合键合位置;其特征在于包括以下步骤:s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解新一轮迭代片间混合键合位置;具体地,

s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数;s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数相应的梯度函数;s23、更新片间混合键合位置坐标(x

hb

,y

hb

);s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3;s3、分析反馈程序模块根据步骤s2迭代求解产生的新一轮迭代片间混合键合位置,利用数字集成电路设计平台生成三维集成电路片间混合键合布局布线中间文件,使用静态时序分析与收敛软件对三维集成片间混合键合电路布局布线的真实每条时序通路时间松弛进行评估分析,如果真实建立时间松弛不满足整体最优要求,执行步骤s1;或者如果真实建立时间松弛满足整体最优要求,执行步骤s4;s4、分析反馈程序模块利用数字集成电路设计平台输出建立时间松弛整体最优的三维集成电路片间混合键合布局布线文件。6.根据权利要求3所述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局可变、时序优先三维集成电路布局布线优化方法,目标待测量是建立时间松弛,用于两个裸片上标准单元布局位置和片间混合键合位置需要同时改变,实现三维集成电路片间混合键合布局布线时序最优;其特征在于包括以下步骤:s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解新一轮迭代片间混合键合位置;具体地,s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数;s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数相应的梯度函数;s23、更新片间混合键合位置坐标(x

hb

,y

hb

);s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3;s3、分析反馈程序模块根据步骤s2迭代求解产生的新一轮迭代片间混合键合位置,利用数字集成电路设计平台优化调整三维集成电路两个裸片各自标准单元位置生成三维集成电路片间混合键合布局布线中间文件,使用静态时序分析与收敛软件对三维集成片间混合键合电路布局布线的真实每条时序通路时间松弛进行评估分析,如果真实建立时间松弛不满足整体最优要求,执行步骤s1;或者如果真实建立时间松弛满足整体最优要求,执行步骤s4;s4、分析反馈程序模块利用数字集成电路设计平台输出建立时间松弛整体最优的三维

集成电路片间混合键合布局布线文件。7.根据权利要求5或者权利要求6任一权利要求所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:所述静态时序分析与收敛软件是tempus静态时序分析与收敛工具。8.根据权利要求1所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:所述机器学习平台是pytorch机器学习平台,所述数字集成电路设计平台是innovus数字集成电路设计平台。9.根据权利要求8所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:所述步骤s24利用片间混合键合位置坐标(x

hb

,y

hb

)不超过三维集成电路芯片的面积范围,和/或片间混合键合位置坐标(x

hb

,y

hb

)位于三维集成电路芯片内可选的位置,和/或片间混合键合位置坐标(x

hb

,y

hb

)的位置不发生冲突这三个约束条件对片间混合键合位置进行调整和更新。10.根据权利要求9所述的一种三维集成电路片间混合键合布局布线优化方法,其特征在于:针对片间混合键合位置坐标(x

hb

,y

hb

)不超过三维集成电路芯片的面积范围约束条件,使用pytorch机器学习平台中clamp()函数进行截断操作;针对片间混合键合位置坐标(x

hb

,y

hb

)位于三维集成电路芯片内可选的位置约束条件,使用pytorch机器学习平台中round()函数,将片间混合键合位置放置在最相邻且符合设计规则检查的位置;针对片间混合键合位置坐标(x

hb

,y

hb

)的位置不发生冲突约束条件,若多个片间混合键合位置发生冲突,则将新生成的片间混合键合分配到外面一圈范围中的空闲位置。

技术总结

本发明涉及一种三维集成电路片间混合键合布局布线优化方法,包括数据识别程序模块将初始位置和每轮迭代后的计算数据导入设计,通过读取数据信息进行计算,得出每轮迭代后待求量的统计计数值;数据预测程序模块使用自动求导计算架构,根据每轮迭代更新的损失函数进行新一轮的数据预测;分析反馈程序模块对每次迭代后设计的总线长和时序信息进行分析,输出每轮迭代结果,以求出整体最优结果。有益效果是优化调整面对面堆叠的两个裸片之间混合键合位置、和/或优化调整两个裸片各自标准单元位置,使得三维集成电路片间混合键合布局布线最优。优。优。

技术研发人员:李永福 纪宇鑫 张宇航 马策 王国兴 连勇

受保护的技术使用者:上海交通大学

技术研发日:2021.08.11

技术公布日:2021/11/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。