一种三维集成电路片间混合键合布局布线优化方法

【技术领域】

1.本发明涉及半导体制造技术领域,具体涉及一种三维集成电路片间混合键合布局布线优化方法。

背景技术:

2.集成电路的发展进入了后摩尔时代,芯片的研发成本不断提高,多芯片的异构集成设计成为更多产品的选择。然而传统的二维芯片封装结构具有芯片间数据通信速度缓慢,功耗较大,且系统面积较大等缺陷。三维芯片通过硅通孔等技术实现电路的垂直互连,使芯片能够在三维方向堆叠的密度最大,而外形的尺寸最小,极大地提升了芯片速度、降低了功耗,成为了芯片产业中一个全新的研究热点。三维集成电路(three

‑

dimensional integrated circuit,3d ic)设计方法应用于多芯片互联封装的场合中,比如多芯片异构设计、多内存模块系统设计、嵌入式桥接系统设计等。

3.在三维集成电路设计中,两个裸片进行面对面堆叠,组成一个三维芯片。在两个裸片的交界处需要确定片间混合键合(hybrid bonding)的位置及相关信号的分配关系。晶圆级混合键合技术可以实现金属之间和介质之间的同时键合,不仅解决了晶圆级底部填充问题,还显著地提高了微连接可靠性;混合键合技术能够加速实现10微米及以下的凸点间距(pitch),提供更高的互连密度、更小更简单的电路、更大的带宽、更低的电容、更低的功耗。根据两个芯片各自的标准单元(standard cell)摆放位置,通过片间混合键合位置将两个裸片进行互联,从而对三维集成电路设计进行全局布局布线,确定信号之间的连接关系,得出全局时序信息。其中,片间混合键合位置的确定,对三维集成电路设计整体的绕线长度和时序信息非常重要。

4.pytorch是一个开源的python机器学习库,基于torch,用于自然语言处理等应用程序,是一个基于python的可续计算包,提供两个高级功能:1、具有强大的gpu加速的张量计算(如numpy);2、包含自动求导系统的深度神经网络。cadence发布的cadence innovus设计实现系统,是新一代的物理设计实现解决方案,功能包括数字集成电路设计中的版图规划、预布线、时序分析、时钟树综合、详细布线、时序优化等环节,使系统芯片(system

‑

on

‑

chip,soc)开发人员能够在加速上市时间的同时交付最佳功耗、性能和面积(ppa)指标的的设计,innovus设计实现系统由具备突破性优化技术所构成的大规模的并行架构所驱动,在先进的16/14/10纳米finfet工艺制程和其他成熟的制程节点上通常能提升10%到20%的功耗、性能和面积指标,并实现最高达10倍的全流程提速和容量增益。出租车几何或曼哈顿距离(manhattan distance)是由十九世纪的赫尔曼

·

闵可夫斯基所创词汇,是种使用在几何度量空间的几何学用语,用以标明两个点在标准坐标系上的绝对轴距总和。为简化和加速复杂ic的开发,cadence设计系统公司推出tempus静态时序分析与收敛工具,旨在帮助系统级芯片(soc)开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

5.静态时序分析简称sta,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个dff(触发器)的建立和保持时间以及

其他基于路径的时延要求是否满足。静态时序分析分类主要分为四种:reg2reg、reg2pin、pin2reg、pin2pin。时钟延时,时钟走全局时钟网络,希望时钟到达寄存器的时间保持一致,但是现实不是这样的,到达各个寄存器的时间不同,称时钟到达目标寄存器和源端寄存器之间的时钟差称为时钟偏斜即tclk2

‑

tclk1,称为时钟延迟。建立(时间)松弛指的是,在下一次时钟触发脉冲来时,第一级触发器输出数据到建立时间前之间的时间最大为多少,这个一般用来确定时钟最大的工作频率。

6.梯度下降是迭代法的一种,可以用于求解最小二乘问题(线性和非线性都可以);在求解机器学习算法的模型参数,即无约束优化问题时,梯度下降(gradient descent)是最常采用的方法之一,另一种常用的方法是最小二乘法;在求解损失函数的最小值时,可以通过梯度下降法来一步步的迭代求解,得到最小化的损失函数和模型参数值。在机器学习中,基于基本的梯度下降法发展了两种梯度下降方法,分别为随机梯度下降法和批量梯度下降法。损失函数(loss function)或代价函数(cost function)是将随机事件或其有关随机变量的取值映射为非负实数以表示该随机事件的“风险”或“损失”的函数。在应用中,损失函数通常作为学习准则与优化问题相联系,即通过最小化损失函数求解和评估模型。梯度的本意是一个向量(矢量),表示某一函数在该点处的方向导数沿着该方向取得最大值,即函数在该点处沿着该方向(此梯度的方向)变化最快,变化率最大(为该梯度的模)。

7.本发明针对确定片间混合键合位置的技术问题,对三维集成电路片间混合键合布局布线方法进行了技术改进。

技术实现要素:

8.本发明的目的是,提供一种优化调整面对面堆叠的两个裸片之间混合键合位置、和/或优化调整两个裸片各自标准单元位置,使得三维集成电路片间混合键合布局布线最优的方法。

9.为实现上述目的,本发明采取的技术方案是一种三维集成电路片间混合键合布局布线优化方法,用于优化调整面对面堆叠的两个裸片之间混合键合位置、和/或优化调整两个裸片各自标准单元位置,使得三维集成电路片间混合键合布局布线最优,包括以下步骤:

10.s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路布局片间混合键合布线计算图模型;

11.s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解片间混合键合最佳位置或者新一轮迭代片间混合键合位置;具体地,

12.s21、计算包含片间混合键合位置的目标待测量损失函数;

13.s22、计算包含片间混合键合位置的目标待测量损失函数相应的梯度函数;

14.s23、更新片间混合键合位置;

15.s24、根据约束条件优化调整片间混合键合位置;

16.s25、获得优化调整后的片间混合键合位置,执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3

‑

1;或者获得片间混合键合最佳位置,执行步骤s3

‑

2;

17.s3

‑

1、分析反馈程序模块根据步骤s2迭代求解产生新一轮迭代片间混合键合位

置,利用数字集成电路设计平台优化调整三维集成电路两个裸片各自标准单元位置生成三维集成电路片间混合键合布局布线中间文件,对三维集成电路片间混合键合布局布线的真实目标待测量进行评估分析,如果真实目标待测量不满足整体最优要求,执行步骤s1;或者如果真实目标待测量满足整体最优要求,执行步骤s4;

18.或者s3

‑

2、分析反馈程序模块根据步骤s2迭代求解产生的片间混合键合最佳位置,利用数字集成电路设计平台生成目标待测量整体最优的三维集成电路片间混合键合布局布线文件;

19.s4、分析反馈程序模块利用数字集成电路设计平台输出真实目标待测量整体最优的三维集成电路片间混合键合布局布线文件。

20.优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,步骤s2所述目标待测量是全局总线长、和/或建立时间松弛;所述全局总线长是指三维集成电路片间混合键合布局布线中片间混合键合和与所述片间混合键合相连的第一级标准单元管脚的曼哈顿距离的总和;所述建立时间松弛是指三维集成电路片间混合键合布局布线中每条时序通路时钟松弛,采用片间混合键合位置布局布线后真实的时钟松弛减去估测曼哈顿线长延时参数进行估测。

21.优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,当目标待测量为全局总线长时,全局总线长损失函数为三维集成电路片间混合键合布局布线中所有线的曼哈顿距离之和:

[0022][0023][0024]

其中(x

i

,y

i

)是标准单元布局位置(x

std

,y

std

),(x

hb

,y

hb

)是片间混合键合布局位置;

[0025]

当目标待测量为建立时间松弛时,每条时序通路时间松弛损失函数为:loss

path

[0026]

其中slack

initial

是当前片间混合键合位置布局布线后真实的时钟松弛,β是单位曼哈顿距离引发的线延时。

[0027]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局固定三维集成电路片间混合键合布局布线优化方法,目标待测量是全局总线长,用于两个裸片上标准单元布局位置固定不变,确定混合键合位置;包括以下步骤:

[0028]

s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;

[0029]

s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解片间混合键合最佳位置;具体地,

[0030]

s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的全局总线长损失函数;

[0031]

s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的全局总线长损失函数相应的梯度函数;

[0032]

s23、更新片间混合键合位置坐标(x

hb

,y

hb

);

[0033]

s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;每几轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都处理片间混合键合位置坐标(x

hb

,y

hb

)对齐、防止出现片间混合键合位置坐标(x

hb

,y

hb

)冲突;

[0034]

s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得片间混合键合最佳位置,执行步骤s3;

[0035]

s3、分析反馈程序模块根据步骤s2迭代求解产生的片间混合键合最佳位置,利用数字集成电路设计平台生成全局总线长整体最优的三维集成电路片间混合键合布局布线文件;

[0036]

s4、分析反馈程序模块利用数字集成电路设计平台输出全局总线长整体最优的三维集成电路片间混合键合布局布线文件。

[0037]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局固定、时序优先三维集成电路片间混合键合布局布线优化方法,目标待测量是建立时间松弛,用于两个裸片上标准单元布局位置固定不变,确定混合键合位置;包括以下步骤:

[0038]

s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;

[0039]

s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解新一轮迭代片间混合键合位置;具体地,

[0040]

s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数;

[0041]

s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数相应的梯度函数;

[0042]

s23、更新片间混合键合位置坐标(x

hb

,y

hb

);

[0043]

s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;

[0044]

s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3;

[0045]

s3、分析反馈程序模块根据步骤s2迭代求解产生的新一轮迭代片间混合键合位置,利用数字集成电路设计平台生成三维集成电路片间混合键合布局布线中间文件,使用静态时序分析与收敛软件对三维集成片间混合键合电路布局布线的真实每条时序通路时间松弛进行评估分析,如果真实建立时间松弛不满足整体最优要求,执行步骤s1;或者如果真实建立时间松弛满足整体最优要求,执行步骤s4;

[0046]

s4、分析反馈程序模块利用数字集成电路设计平台输出建立时间松弛整体最优的三维集成电路片间混合键合布局布线文件。

[0047]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,是一种布局可变、时序优先三维集成电路布局布线优化方法,目标待测量是建立时间松弛,用于两个裸片上标准单元布局位置和片间混合键合位置需要同时改变,实现三维集成电路片间混合键合布局布线时序最优;包括以下步骤:

[0048]

s1、数据识别程序模块将三维集成电路片间混合键合布局布线初始文件或者每轮迭代后生成的三维集成电路片间混合键合布局布线中间文件导入机器学习平台,构建三维集成电路片间混合键合布局布线计算图模型;

[0049]

s2、数据预测程序模块根据步骤s1构建的三维集成电路布局布线计算图模型,使用机器学习平台包含的梯度下降法迭代求解新一轮迭代片间混合键合位置;具体地,

[0050]

s21、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数;

[0051]

s22、计算包含片间混合键合位置坐标(x

hb

,y

hb

)的建立时间松弛损失函数相应的梯度函数;

[0052]

s23、更新片间混合键合位置坐标(x

hb

,y

hb

);

[0053]

s24、每轮更新片间混合键合位置坐标(x

hb

,y

hb

)后,都约束片间混合键合位置坐标(x

hb

,y

hb

)最大最小值,使片间混合键合位置坐标(x

hb

,y

hb

)合理化;

[0054]

s25、获得优化调整后的片间混合键合位置坐标(x

hb

,y

hb

),执行步骤s21;或者获得新一轮迭代片间混合键合位置,执行步骤s3;

[0055]

s3、分析反馈程序模块根据步骤s2迭代求解产生的新一轮迭代片间混合键合位置,利用数字集成电路设计平台优化调整三维集成电路两个裸片各自标准单元位置生成三维集成电路片间混合键合布局布线中间文件,使用静态时序分析与收敛软件对三维集成片间混合键合电路布局布线的真实每条时序通路时间松弛进行评估分析,如果真实建立时间松弛不满足整体最优要求,执行步骤s1;或者如果真实建立时间松弛满足整体最优要求,执行步骤s4;

[0056]

s4、分析反馈程序模块利用数字集成电路设计平台输出建立时间松弛整体最优的三维集成电路片间混合键合布局布线文件。

[0057]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,所述静态时序分析与收敛软件是tempus静态时序分析与收敛工具。

[0058]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,所述机器学习平台是pytorch机器学习平台,所述数字集成电路设计平台是innovus数字集成电路设计平台。

[0059]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,所述步骤s24利用片间混合键合位置坐标(x

hb

,y

hb

)不超过三维集成电路芯片的面积范围,和/或片间混合键合位置坐标(x

hb

,y

hb

)位于三维集成电路芯片内可选的位置,和/或片间混合键合位置坐标(x

hb

,y

hb

)的位置不发生冲突这三个约束条件对片间混合键合位置进行调整和更新。

[0060]

优选地,上述的一种三维集成电路片间混合键合布局布线优化方法,针对片间混合键合位置坐标(x

hb

,y

hb

)不超过三维集成电路芯片的面积范围约束条件,使用pytorch机器学习平台中clamp()函数进行截断操作;针对片间混合键合位置坐标(x

hb

,y

hb

)位于三维集成电路芯片内可选的位置约束条件,使用pytorch机器学习平台中round()函数,将片间混合键合位置放置在最相邻且符合设计规则检查的位置;针对片间混合键合位置坐标(x

hb

,y

hb

)的位置不发生冲突约束条件,若多个片间混合键合位置发生冲突,则将新生成的片间混合键合分配到外面一圈范围中的空闲位置。

[0061]

本发明与现有技术相比有如下有益效果:在符合电路设计规则检查,电路互联工艺的情况下,优化裸片之间的混合键合和标准单元的位置,调整信号分配,从而使得三维集

成电路设计在整体绕线长度和时序上实现最优解;通过改变数据预测模块中求导函数和损失函数来调整布线长度的优化方向,具有高可扩展性,可以根据具体的芯片实现参数,仅对相关函数进行调整,系统架构可重用性强;提供一种对全局总线长的近似估算方法,运行速度快、算法实现所需的内存较少。

【附图说明】

[0062]

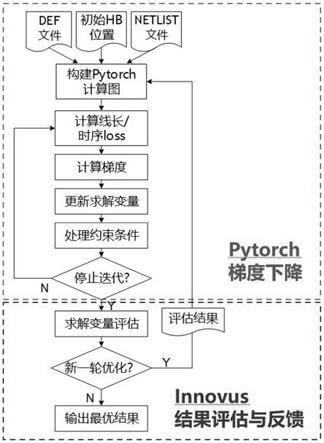

图1是基于pytorch

‑

innovus软件框架的一种三维集成电路片间混合键合布局布线优化方法流程图。

[0063]

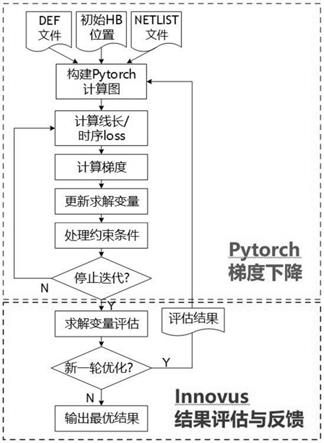

图2是基于pytorch

‑

innovus软件框架的一种布局固定三维集成电路片间混合键合布局布线优化方法流程图。

[0064]

图3是基于pytorch

‑

innovus软件框架的一种布局固定、时序优先三维集成电路片间混合键合布局布线优化方法流程图。

[0065]

图4是基于pytorch

‑

innovus软件框架的一种布局可变、时序优先三维集成电路片间混合键合布局布线优化方法流程图。

[0066]

图5是一种三维集成电路片间混合键合布局布线优化方法多片间混合键合位置冲突时的位置调整分配策略示意图。

[0067]

图6是一种三维集成电路片间混合键合布局布线优化方法全局总线长估测示意图。

【具体实施方式】

[0068]

下面结合实施例并参照附图对本发明作进一步描述。

[0069]

实施例1

[0070]

本实施例实现一种三维集成电路片间混合键合布局布线优化方法。

[0071]

图1是基于pytorch

‑

innovus软件框架的一种三维集成电路片间混合键合布局布线优化方法流程图。如附图1所示,本实施例一种三维集成电路片间混合键合布局布线优化方法的基于的软件架构主要包括以下几个模块:数据识别、数据预测、分析反馈。数据识别使用了innovus将初始位置和每轮迭代后的计算数据导入设计,通过读取数据信息进行计算,得出每轮迭代后待求量的统计计数值。数据预测使用了pytorch的自动求导计算架构,根据每轮迭代更新的损失函数进行新一轮的数据预测。分析反馈使用了innovus和tempus对每次迭代后设计的总线长和时序信息进行分析,输出每轮迭代结果,以求出整体最优结果。本实施例一种三维集成电路片间混合键合布局布线优化方法通过改变互联算法损失函数和进行逐次迭代的方法,实现了对三维集成电路布局布线的优化,具有高可扩展、高运行速度、算法实现内存占用少等特点。

[0072]

本实施例一种三维集成电路片间混合键合布局布线优化方法,基于pytorch

‑

innovus联合框架进行实现,针对不同的目标待测量,可扩展性强。

[0073]

本实施例一种三维集成电路片间混合键合布局布线优化方法三维集成电路互联布线的优化可以根据所选择的目标待测量进行变化,包括以下步骤:数据识别、数据预测、分析反馈。

[0074]

a.设计数据识别;

[0075]

b.目标数据预测;

[0076]

c.目标量分析反馈;

[0077]

d.最优目标量筛选。

[0078]

本实施例一种三维集成电路片间混合键合布局布线优化方法的目标数据预测是通过预估全局待测量,构建待测函数及其求导函数来实现的。

[0079]

a.设计中片间混合键合和与其相连的第一级标准单元的pin的曼哈顿距离的总和作为全局总线长的预估函数;

[0080]

b.设计中每条时序通路的时钟松弛,采用特定混合键合位置、布局布线后真实的时钟松弛减去估测曼哈顿线长参数来进行估测;

[0081]

c.自动求导架构对目标待测量的损失函数进行求导,算出损失函数的梯度函数,对设计中的目标待测量进行按轮次的优化更新;

[0082]

d.基于pytorch

‑

innovus联合框架支持对多种目标待测量及其梯度函数的自动求导,系统架构能够针对不同的优化目标采用统一的实现流程。

[0083]

本实施例一种三维集成电路片间混合键合布局布线优化方法的目标量分析反馈是使用innovus平台得出本轮迭代真实的总线长或时序报告,并对下一轮的目标函数进行更新,包括以下步骤:

[0084]

a.基于innovus平台得出真实目标参数;

[0085]

b.抓取有效参数,反馈到原有目标函数;

[0086]

c.更新下一轮运算的目标函数。

[0087]

实施例2

[0088]

本实施例实现一种三维集成电路片间混合键合布局布线优化方法。

[0089]

图1是基于pytorch

‑

innovus软件框架的一种三维集成电路片间混合键合布局布线优化方法流程图。如附图1所示,本实施例一种三维集成电路片间混合键合布局布线优化方法基于pytorch

‑

innovus联合框架,在进行三维集成电路布局布线之前,需要确定两个面对面堆叠的裸片之间混合键合的位置,对两个裸片之间的信号进行合理分配,以达到三维芯片整体待测量(总线长、建立时钟松弛)的最优解。

[0090]

本实施例一种三维集成电路片间混合键合布局布线优化方法将三维集成电路的互联问题转化为目标待测量的最优化问题,目标待测量包括全体混合键合和与其相连的第一级标准单元的pin的线长的总和、以及全局最差的reg2reg的建立时钟松弛。本实施使用梯度下降算法对目标待测量的最优值进行求解,使用了基于pytorch

‑

innovus联合框架进行实现,多次迭代逐次优化,每轮迭代计算损失函数及其梯度,按照梯度下降方法对损失函数进行更新。

[0091]

根据两个裸片的def文件、网表文件、初始混合键合位置文件和时序文件,在innovus中读取设计相关数据。当两个裸片上的标准单元布局的位置(x

std

,y

std

)固定不变时,调整混合键合的位置(x

hb

,y

hb

),并根据以下三个约束条件对混合键合位置进行调整和更新:x

hb

,y

hb

不超过芯片的面积范围,x

hb

,y

hb

位于芯片内可选的位置,x

hb

,y

hb

的位置不发生冲突。

[0092]

x=clamp(x,0,200μm)

[0093]

x=round(x|pitch)

×

pitch

[0094]

针对第一个约束,本实施例一种三维集成电路片间混合键合布局布线优化方法使用了pytorch平台中clamp()函数进行截断操作。针对第二个约束,本实施例一种三维集成电路片间混合键合布局布线优化方法利用了round()函数,将混合键合的位置放置在最相邻且符合设计规则检查的位置。图5是一种三维集成电路片间混合键合布局布线优化方法多片间混合键合位置冲突时的位置调整分配策略示意图。如附图5所示,本实施例一种三维集成电路片间混合键合布局布线优化方法针对第三个约束,若多个混合键合位置发生冲突,则将新生成的混合键合分配到外面一圈范围中的空闲位置,以此类推。

[0095]

三维集成电路中准确的线长测定需要调用innovus,难以计算线长的梯度函数。图6是一种三维集成电路片间混合键合布局布线优化方法全局总线长估测示意图。如附图6所示,本实施例一种三维集成电路片间混合键合布局布线优化方法提供了一种针对全局总线长的近似估计方法,使用了混合键合与其相连的第一级标准单元的pin的曼哈顿距离作为这条线线长的近似值。总线长即为所有线的曼哈顿距离线长之和。当目标待测量为设计的总线长时,损失函数loss为设计中所有线的曼哈顿距离之和。

[0096][0097][0098]

当目标待测量为优化整体设计中关键路径的时钟松弛(timing slack)时,每条时序通路的时钟松弛采用下式进行统计估计。当loss

total

=

‑

1时,所有时序通路中损失函数loss的最小值,其中slack

initial

是在当前混合键合位置下,布局布线后真实的时钟松弛,β近似等于单位曼哈顿距离引发的线延时。

[0099]

loss

path

[0100]

当三维集成电路设计的整体布局可变时,电路中的标准单元(x

std

,y

std

)和混合键合(x

hb

,y

hb

)的位置都需要根据innovus平台中反馈的目标待测量的变化,进行逐轮迭代,直到选出目标待测量的最优解。在每轮次迭代计算中,在pytorch平台进行梯度下降算法与innovus平台进行设计的时序分析之间,使用innovus对全局设计的标准单元进行重新布局(placement),优化当前混合键合位置下的标准单元的位置。

[0101]

本实施例一种三维集成电路片间混合键合布局布线优化方法使用了基于pytorch

‑

innovus联合框架进行实现,支持对目标待测量及其梯度函数的自动求导,使得系统架构能够针对不同的优化目标采用统一的实现流程,减少芯片的设计开发周期。

[0102]

实施例3

[0103]

本实施例实现一种三维集成电路片间混合键合布局布线优化方法。

[0104]

图1是基于pytorch

‑

innovus软件框架的一种三维集成电路片间混合键合布局布线优化方法流程图。如附图1所示,本实施例一种三维集成电路片间混合键合布局布线优化方法是一种基于pytorch

‑

innovus联合框架的三维集成电路互联优化算法。本实施例一种三维集成电路互联优化方法利用了innovus的布局布线功能和pytorch平台的自动求导、梯度优化框架。主要包括以下几个模块:数据识别、数据预测、分析反馈。

[0105]

数据识别使用了innovus将初始位置和每轮迭代后的计算数据导入设计,通过读取数据信息进行计算,得出每轮迭代后待求量的统计计数值。数据预测使用了pytorch的自动求导计算架构,根据每轮迭代更新的损失函数进行新一轮的数据预测。分析反馈使用了innovus和tempus对每次迭代后设计的总线长和时序信息进行分析,输出每轮迭代结果,以求出整体最优结果。本实施例一种三维集成电路片间混合键合布局布线优化方法可以针对三种不同应用场景及需求下的三维集成电路设计,进行布局布线操作的优化。

[0106]

图2是基于pytorch

‑

innovus软件框架的一种布局固定三维集成电路片间混合键合布局布线优化方法流程图。如附图2所示,本实施例一种三维集成电路片间混合键合布局布线优化方法第一个应用场景中,两个裸片上的标准单元布局的位置固定不变,确定混合键合的位置;在混合键合符合芯片设计规则检查、不超出芯片面积的条件下,最小化三维集成电路设计的总线长。

[0107]

本实施例一种三维集成电路片间混合键合布局布线优化方法第一个应用场景中,根据两个裸片的def文件、网表文件、初始混合键合位置文件,在innovus中构建出计算图,之后进行多次迭代,求出混合键合的最佳位置。每轮迭代都会计算出新一轮的混合键合的位置(x

hb

,y

hb

),并根据此位置坐标,对算法中的损失函数进行更新,并计算出相应的梯度函数。每轮更新混合键合位置后,都需要约束其坐标最大最小值,使其位置坐标合理化。每隔几轮数据更新,都需要处理混合键合的位置对齐,解决位置冲突。

[0108]

图3是基于pytorch

‑

innovus软件框架的一种布局固定、时序优先三维集成电路片间混合键合布局布线优化方法流程图。如附图3所示,本实施例一种三维集成电路片间混合键合布局布线优化方法第二个应用场景中,两个裸片上的标准单元布局的位置固定不变,确定混合键合的位置;在混合键合符合芯片设计规则检查、不超出芯片面积的条件下,最大化三维集成电路设计中reg2reg最差情况下的时钟松弛(the worst timing slack)。

[0109]

本实施例一种三维集成电路片间混合键合布局布线优化方法第二个应用场景中,根据两个裸片的def文件、网表文件、初始混合键合位置文件和时序文件,在innovus中构建出计算图,之后进行多次迭代,求出混合键合的最佳位置。每轮迭代都会计算出新一轮的混合键合的位置(x

hb

,y

hb

),梯度下降过程和第一个应用场景一致,但是算法的损失函数不同。每轮更新混合键合位置后,调整键合位置,使其位置坐标合理化。利用innovus重新计算每条路径上的时序信息,得到时序报告,重新构建计算图。

[0110]

图4是基于pytorch

‑

innovus软件框架的一种布局可变、时序优先三维集成电路片间混合键合布局布线优化方法流程图。如附图4所示,本实施例一种三维集成电路片间混合键合布局布线优化方法第三个应用场景中,两个裸片上的标准单元布局的位置和混合键合的位置需要同时改变,来实现系统的时序最优;在混合键合符合芯片设计规则检查、不超出芯片面积的条件下,最大化三维集成电路设计中reg2reg最差情况下的时钟松弛(the worst timing slack)。

[0111]

本实施例一种三维集成电路片间混合键合布局布线优化方法第三个应用场景中,根据两个裸片的def文件、网表文件、初始混合键合位置文件和时序文件,在innovus中构建出计算图,之后进行多次迭代,求出混合键合的最佳位置。每轮迭代都会计算出新一轮的混合键合的位置(x

hb

,y

hb

),梯度下降过程和第一个应用场景一致,在梯度下降算法和时序分析之间,使用innovus重新进行布局(placement),从而优化当前混合键合下的标准单元位

置。其他流程与第二个应用场景相同,利用innovus重新计算每条路径上的时序信息,得到时序报告,重新构建计算图。

[0112]

本实施例一种三维集成电路片间混合键合布局布线优化方法还提供一种针对全局总线长的近似估计方法。本实施例中线长的估算方法,采用了混合键合与其相连的第一级标准单元的pin的曼哈顿距离(manhattan distance)作为这条线(net)的线长近似值。总线长即为所有线的曼哈顿距离线长之和。

[0113]

本实施例算法通过改变数据预测模块中求导函数和损失函数来调整布线长度的优化方向,具有高可扩展性,可以根据具体的芯片实现参数,仅对相关函数进行调整,系统架构可重用性强。本实施例提供一种对全局总线长的近似估算方法,运行速度快、算法实现所需的内存较少。

[0114]

本领域普通技术人员可以理解,实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,所述的程序可以存储于任一种计算机可读存储介质中,其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(read

‑

only memory,rom)或随机存储记忆体(random access memory,ram)等。

[0115]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和补充,这些改进和补充也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。