1.本公开涉及通信领域,特别涉及一种极化码编码及译码方法和装置、信息传输系统。

背景技术:

2.在对极化码进行译码的过程中,通过将所接收的具有预设长度的极化码分为多个相互耦合的分段信息,在分别对各分段信息独立地进行译码后,通过对各分段译码结果进行联合检测判决和位置置换以得到最终译码结果,并对最终译码结果进行校验以判断译码是否正确。

技术实现要素:

3.发明人通过研究发现,由于在现有技术中,只有经过联合检测判决和位置置换处理后才能得到最终译码结果,这时通过对最终译码结果进行校验以判断译码是否正确,而在位置置换前并不具备对各分段译码结果进行校验的能力。

4.据此,本公开提供一种极化码编码及译码方案,以便在译码器侧为各分段译码结果提供校验能力,有效提高译码性能。

5.根据本公开实施例的第一方面,提供一种极化码编码方法,包括:生成第一待编码码元序列;按照预设规则将所述第一待编码码元序列进行第一位置置换,以得到m个长度为n的分段,其中m和n为2的整次幂;分别对每个分段中的信息码元序列进行校验码生成运算以得到相对应的校验码;用所得到的m个校验码取代所述第一待编码码元序列中的初始校验码,以得到第二待编码码元序列;将所述第二待编码码元序列进行极化码编码以得到编码码字,以便极化码译码器在对接收到的编码码字进行分段译码后,利用每个校验码对相对应的分段中的信息码元序列进行校验。

6.在一些实施例中,生成第一待编码码元序列包括:按照预设参数的极化码编码公式,利用待编码信息码元序列、预设的冻结码元序列和所述初始校验码生成所述第一待编码码元序列,其中所述初始校验码中各码元的值任意设定。

7.在一些实施例中,所述校验码为crc校验码、奇偶校验码或哈希校验码。

8.根据本公开实施例的第二方面,提供一种极化码编码器,包括:第一序列生成模块,被配置为生成第一待编码码元序列;第一位置置换模块,被配置为按照预设规则将所述第一待编码码元序列进行第一位置置换,以得到m个长度为n的分段,其中m和n为2的整次幂;校验码生成模块,被配置为分别对每个分段中的信息码元序列进行校验码生成运算以得到相对应的校验码;第二序列生成模块,被配置为用所得到的m个校验码取代所述第一待编码码元序列中的初始校验码,以得到第二待编码码元序列;编码模块,被配置为将所述第二待编码码元序列进行极化码编码以得到编码码字,以便极化码译码器在对接收到的编码码字进行分段译码后,利用每个校验码对相对应的分段中的信息码元序列进行校验。

9.在一些实施例中,第一序列生成模块被配置为按照预设参数的极化码编码公式,

利用待编码信息码元序列、预设的冻结码元序列和所述初始校验码生成所述第一待编码码元序列,其中所述初始校验码中各码元的值任意设定。

10.在一些实施例中,所述校验码为crc校验码、奇偶校验码或哈希校验码。

11.根据本公开实施例的第三方面,提供一种极化码编码器,包括:存储器,被配置为存储指令;处理器,耦合到存储器,处理器被配置为基于存储器存储的指令执行实现如上述任一实施例所述的方法。

12.根据本公开实施例的第四方面,提供一种极化码译码方法,包括:将接收到的编码码字按顺序分为相互耦合的m个长度为n的第一码元序列,其中参数m和n分别与所述权利要求1中的参数m和n相同;分别对所述m个第一码元序列独立地进行译码处理,以得到m个第一分段译码结果;对所述m个第一分段译码结果进行联合检测判决,以得到m个第二分段译码结果,其中在每个第二分段译码结果中包括信息码元序列、冻结码元序列和相对应的校验码;在每个第二分段译码结果中,利用所述校验码对所述信息码元序列进行校验;若每个第二分段译码结果中的所述信息码元序列均通过校验,则按照预设规则将所述m个第二分段译码结果进行第二位置置换,以得到相应的输出码元序列,其中所述第二位置置换是所述权利要求1中的第一位置置换的逆操作,所述输出码元序列中的信息码元序列为所述权利要求1中的第一待编码码元序列中的待编码信息码元序列的译码结果。

13.在一些实施例中,分别对所述m个第一码元序列独立地进行译码处理包括:利用m个分段译码器并行地对所述m个第一码元序列进行译码处理,以得到m个第一分段译码结果。

14.在一些实施例中,在任意一个第二分段译码结果中的信息码元序列未通过校验的情况下,则判定译码失败,并停止对所述接收到的编码码字的译码处理。

15.在一些实施例中,所述校验码为crc校验码、奇偶校验码或哈希校验码。

16.根据本公开实施例的第五方面,提供一种极化码译码器,包括:码字处理模块,被配置为将接收到的编码码字按顺序分为相互耦合的m个长度为n的第一码元序列,其中参数m和n分别与所述权利要求1中的参数m和n相同;译码模块,被配置为分别对所述m个第一码元序列独立地进行译码处理,以得到m个第一分段译码结果;检测模块,被配置为对所述m个第一分段译码结果进行联合检测判决,以得到m个第二分段译码结果,其中在每个第二分段译码结果中包括信息码元序列、冻结码元序列和相对应的校验码;校验模块,被配置为在每个第二分段译码结果中,利用所述校验码对所述信息码元序列进行校验;第二位置置换模块,被配置为若每个第二分段译码结果中的所述信息码元序列均通过校验,则按照预设规则将所述m个第二分段译码结果进行第二位置置换,以得到相应的输出码元序列,其中所述第二位置置换是所述权利要求1中的第一位置置换的逆操作,所述输出码元序列中的信息码元序列为所述权利要求1中的第一待编码码元序列中的待编码信息码元序列的译码结果。

17.在一些实施例中,所述译码模块包括:m个分段译码器,被配置为并行地对所述m个第一码元序列进行译码处理,以得到m个第一分段译码结果。

18.在一些实施例中,校验模块还被配置为在任意一个第二分段译码结果中的信息码元序列未通过校验的情况下,则判定译码失败,并停止对所述接收到的编码码字的译码处理。

19.在一些实施例中,所述校验码为crc校验码、奇偶校验码或哈希校验码。

20.根据本公开实施例的第六方面,提供一种极化码译码器,包括:存储器,被配置为存储指令;处理器,耦合到存储器,处理器被配置为基于存储器存储的指令执行实现如上述任一实施例所述的方法。

21.根据本公开实施例的第七方面,提供一种信息传输系统,包括:信息发送端,所述信息发送端包括如上述任一实施例所述的极化码编码器;信息接收端,所述信息接收端如上述任一实施例所述的极化码译码器。

22.根据本公开实施例的第八方面,提供一种计算机可读存储介质,其中,计算机可读存储介质存储有计算机指令,指令被处理器执行时实现如上述任一实施例涉及的方法。

23.通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其优点将会变得清楚。

附图说明

24.构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解释本公开的原理。

25.参照附图,根据下面的详细描述,可以更加清楚地理解本公开,其中:

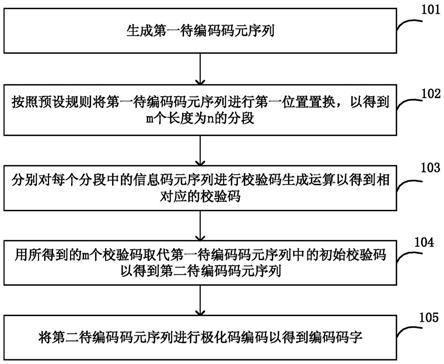

26.图1是根据本公开一个实施例的极化码编码方法的流程示意图;

27.图2是根据本公开一个实施例的极化码编码器的结构示意图;

28.图3是根据本公开另一个实施例的极化码编码器的结构示意图;

29.图4是根据本公开一个实施例的极化码译码方法的流程示意图;

30.图5是根据本公开一个实施例的极化码译码器的结构示意图;

31.图6是根据本公开另一个实施例的极化码译码器的结构示意图;

32.图7是根据本公开另一个实施例的极化码译码器的结构示意图;

33.图8是根据本公开一个实施例的信息传输系统的结构示意图。

34.应当明白,附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。此外,相同或类似的参考标号表示相同或类似的构件。

具体实施方式

35.现在将参照附图来详细描述本公开的各种示例性实施例。对示例性实施例的描述仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。本公开可以以许多不同的形式实现,不限于这里所述的实施例。提供这些实施例是为了使本公开透彻且完整,并且向本领域技术人员充分表达本公开的范围。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、材料的组分和数值应被解释为仅仅是示例性的,而不是作为限制。

36.本公开中使用的“包括”或者“包含”等类似的词语意指在该词前的要素涵盖在该词后列举的要素,并不排除也涵盖其他要素的可能。

37.本公开使用的所有术语(包括技术术语或者科学术语)与本公开所属领域的普通技术人员理解的含义相同,除非另外特别定义。还应当理解,在诸如通用字典中定义的术语应当被解释为具有与它们在相关技术的上下文中的含义相一致的含义,而不应用理想化或

极度形式化的意义来解释,除非这里明确地这样定义。

38.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。

39.图1是根据本公开一个实施例的极化码编码方法的流程示意图。在一些实施例中,下面的极化码编码方法步骤由极化码编码器执行。

40.在步骤101,生成第一待编码码元序列。

41.在一些实施例中,按照预设参数的极化码编码公式,利用待编码信息码元序列、预设的冻结码元序列和初始校验码生成第一待编码码元序列,其中初始校验码占用非冻结码元的比特位,初始校验码中各码元的值任意设定。例如,初始校验码中各码元的值均为0。

42.这里需要说明的是,由于极化码编码公式本身并不是本公开的发明点所在,因此这里不展开描述。

43.在步骤102,按照预设规则将第一待编码码元序列进行第一位置置换,以得到m个长度为n的分段,其中m和n为2的整次幂。

44.通过位置置换,将第一待编码码元序列中的每个码元映射到相应的位置上,以便得到m个长度为n的分段。

45.在步骤103,分别对每个分段中的信息码元序列进行校验码生成运算以得到相对应的校验码。

46.在一些实施例中,校验码为crc(cyclic redundancy check,循环冗余校验)校验码、奇偶校验码、哈希校验码、或者其它适当的校验码。

47.在步骤104,用所得到的m个校验码取代第一待编码码元序列中的初始校验码,以得到第二待编码码元序列。

48.在步骤105,将第二待编码码元序列进行极化码编码以得到编码码字,以便极化码译码器在对接收到的编码码字进行分段译码后,利用每个校验码对相对应的分段中的信息码元序列进行校验。

49.由于如何通过极化编码以得到编码码字并不是本公开的发明点所在,因此这里不展开描述。

50.例如,首先按照预设参数的极化码编码公式,利用待编码信息码元序列、预设的冻结码元序列和初始校验码生成第一待编码码元序列,其中初始校验码中各码元的值均为0。然后按照预设规则将第一待编码码元序列进行第一位置置换,以得到64个分段,每个分段的长度为2的整次幂。分别对这64个分段中的信息码元序列进行crc校验码生成运算以得到相对应的crc校验码。接下来,利用所得到的64个crc校验码对第一待编码码元序列中的初始校验码进行替换,以得到第二待编码码元序列。最后将第二待编码码元序列进行极化码编码以得到编码码字。由此可使得极化码译码器在对接收到的编码码字进行分段译码后,利用每个校验码对相对应的分段中的信息码元序列进行校验。

51.在本公开上述实施例提供的极化码编码方法中,通过在编码过程中,为每个分段生成相应的校验码,以便极化码译码器可直接利用校验码对相对应的分段中的信息码元序列进行校验,从而在译码过程中实现并行校验,有效提升译码性能。

52.图2是根据本公开一个实施例的极化码编码器的结构示意图。如图2所示,极化码编码器包括第一序列生成模块21、第一位置置换模块22、校验码生成模块23、第二序列生成

模块24和编码模块25。

53.第一序列生成模块21被配置为生成第一待编码码元序列。

54.在一些实施例中,第一序列生成模块被配置为按照预设参数的极化码编码公式,利用待编码信息码元序列、预设的冻结码元序列和初始校验码生成第一待编码码元序列,其中初始校验码占用非冻结码元的比特位,初始校验码中各码元的值任意设定。例如,初始校验码中各码元的值均为0。

55.第一位置置换模块22被配置为按照预设规则将第一待编码码元序列进行第一位置置换,以得到m个长度为n的分段,其中m和n为2的整次幂。

56.校验码生成模块23被配置为分别对每个分段中的信息码元序列进行校验码生成运算以得到相对应的校验码。

57.在一些实施例中,校验码为crc校验码、奇偶校验码、哈希校验码、或者其它适当的校验码。

58.第二序列生成模块24被配置为用所得到的m个校验码取代第一待编码码元序列中的初始校验码,以得到第二待编码码元序列。

59.编码模块25被配置为将第二待编码码元序列进行极化码编码以得到编码码字,以便极化码译码器在对接收到的编码码字进行分段译码后,利用每个校验码对相对应的分段中的信息码元序列进行校验。

60.图3是根据本公开另一个实施例的极化码编码器的结构示意图。如图3所示,极化码编码器包括存储器31和处理器32。

61.存储器31用于存储指令。处理器32耦合到存储器31。处理器32被配置为基于存储器存储的指令执行实现如图1中任一实施例涉及的方法。

62.如图3所示,极化码编码器还包括通信接口33,用于与其它设备进行信息交互。同时,该极化码编码器还包括总线34,处理器32、通信接口33、以及存储器31通过总线34完成相互间的通信。

63.存储器31可以包含高速ram(random access memory,随机存取存储器),也可还包括nvm(non-volatile memory,非易失性存储器)。例如至少一个磁盘存储器。存储器31也可以是存储器阵列。存储器31还可能被分块,并且块可按一定的规则组合成虚拟卷。

64.此外,处理器32可以是一个中央处理器,或者可以是asic(application specific integrated circuit,专用集成电路),或者是被配置成实施本公开实施例的一个或多个集成电路。

65.本公开还提供一种计算机可读存储介质。计算机可读存储介质存储有计算机指令,指令被处理器执行时实现如图1中任一实施例涉及的方法。

66.图4是根据本公开一个实施例的极化码译码方法的流程示意图。在一些实施例中,下面的极化码译码方法步骤由极化码译码器执行。

67.在步骤401,将接收到的编码码字按顺序分为相互耦合的m个长度为n的第一码元序列,其中参数m和n分别与图1所示实施例中的参数m和n相同。

68.在步骤402,分别对m个第一码元序列独立地进行译码处理,以得到m个第一分段译码结果。

69.在一些实施例中,可通过设置一个分段译码器,以便依次对该m个第一码元序列进

行译码处理。

70.在另一些实施例中,还可设置l个分段译码器,其中l

×

k=m。将m个第一码元序列分为k组,每一组中包括l个分段。首先利用l个分段译码器并行地对第一组中的l个分段进行译码处理,然后利用l个分段译码器并行地对第二组中的l个分段进行译码处理,依次类推,直到利用l个分段译码器并行地对第k组中的l个分段进行译码处理为止。

71.在又一些实施例中,还可设置m个分段译码器,以便并行地对m个第一码元序列进行译码处理。

72.这里需要说明的是,在分段译码器的数量较多的情况下,可提升译码处理的效率,但占用的空间较多。相反,在分段译码器的数量较少的情况下,译码处理效率会受到影响,但占用的空间较小,在诸如可穿戴设备领域有相应优势。因此可根据需要选择分段译码器的数量。

73.在一些实施例中,分段译码器为sc(successive cancellation,连续消除)译码器。

74.在步骤403,对m个第一分段译码结果进行联合检测判决,以得到m个第二分段译码结果,其中在每个第二分段译码结果中包括信息码元序列、冻结码元序列和相对应的校验码。在每个第二分段译码结果中,校验码占用非冻结码元的比特位。

75.这里需要说明的是,由于联合检测判决本身并不是本公开的发明点所在,因此这里不展开描述。

76.在一些实施例中,校验码为crc校验码、奇偶校验码、哈希校验码、或者其它适当的校验码。

77.在步骤404,在每个第二分段译码结果中,利用校验码对信息码元序列进行校验。

78.在步骤405,若每个第二分段译码结果中的信息码元序列均通过校验,则按照预设规则将m个第二分段译码结果进行第二位置置换,以得到相应的输出码元序列。

79.需要说明的是,第二位置置换是图1所示实施例中的第一位置置换的逆操作,输出码元序列中的信息码元序列为图1所示实施例中的第一待编码码元序列中的待编码信息码元序列的译码结果。

80.在一些实施例中,在任意一个第二分段译码结果中的信息码元序列未通过校验的情况下,则判定译码失败,并停止对接收到的编码码字的译码处理。

81.例如,将接收到的编码码字按顺序分为相互耦合的64个第一码元序列,每个第一码元序列的长度为2的整数幂。通过对各第一码元序列进行并行地sc译码,并将所得到的64个第一分段译码结果进行联合检测判决,以得到64个第二分段译码结果,其中在每个第二分段译码结果中包括信息码元序列、冻结码元序列和相对应的crc校验码。接下来,在每个第二分段译码结果中,利用crc校验码对信息码元序列进行校验。若64个第二分段译码结果中的信息码元序列均通过校验,则按照预设规则将这64个第二分段译码结果进行第二位置置换,以得到相应的输出码元序列。输出码元序列中的信息码元序列为图1所示实施例中的第一待编码码元序列中的待编码信息码元序列的译码结果。

82.在本公开上述实施例提供的极化码译码方法中,通过在译码过程中,利用校验码对相对应的分段中的信息码元序列进行并行校验,从而有效提高译码性能。

83.图5是根据本公开一个实施例的极化码译码器的结构示意图。如图5所示,极化码

译码器包括码字处理模块51、译码模块52、检测模块53、校验模块54和第二位置置换模块55。

84.码字处理模块51被配置为将接收到的编码码字按顺序分为相互耦合的m个长度为n的第一码元序列,其中参数m和n分别与图1所示实施例中的参数m和n相同。

85.译码模块52被配置为分别对m个第一码元序列独立地进行译码处理,以得到m个第一分段译码结果。

86.在一些实施例中,译码模块52可包括一个分段译码器,以便依次对该m个第一码元序列进行译码处理。

87.在另一些实施例中,译码模块52可包括l个分段译码器,其中l

×

k=m。将m个第一码元序列分为k组,每一组中包括l个分段。首先利用l个分段译码器并行地对第一组中的l个分段进行译码处理,然后利用l个分段译码器并行地对第二组中的l个分段进行译码处理,依次类推,直到利用l个分段译码器并行地对第k组中的l个分段进行译码处理为止。

88.在又一些实施例中,译码模块52可包括m个分段译码器,以便并行地对m个第一码元序列进行译码处理。

89.在一些实施例中,分段译码器为sc译码器。

90.这里需要说明的是,在分段译码器的数量较多的情况下,可提升译码处理的效率,但占用的空间较多。相反,在分段译码器的数量较少的情况下,译码处理效率会受到影响,但占用的空间较小,在诸如可穿戴设备领域有相应优势。因此可根据需要选择分段译码器的数量。

91.检测模块53被配置为对m个第一分段译码结果进行联合检测判决,以得到m个第二分段译码结果,其中在每个第二分段译码结果中包括信息码元序列、冻结码元序列和相对应的校验码。在每个第二分段译码结果中,校验码占用非冻结码元的比特位。

92.这里需要说明的是,由于联合检测判决本身并不是本公开的发明点所在,因此这里不展开描述。

93.在一些实施例中,校验码为crc校验码、奇偶校验码、哈希校验码、或者其它适当的校验码。

94.校验模块54被配置为在每个第二分段译码结果中,利用校验码对信息码元序列进行校验。

95.第二位置置换模块55被配置为若每个第二分段译码结果中的信息码元序列均通过校验,则按照预设规则将m个第二分段译码结果进行第二位置置换,以得到相应的输出码元序列。

96.需要说明的是,第二位置置换是图1所示实施例中的第一位置置换的逆操作,输出码元序列中的信息码元序列为图1所示实施例中的第一待编码码元序列中的待编码信息码元序列的译码结果。

97.在一些实施例中,校验模块54还被配置为在任意一个第二分段译码结果中的信息码元序列未通过校验的情况下,则判定译码失败,并停止对接收到的编码码字的译码处理。

98.图6是根据本公开另一个实施例的极化码译码器的结构示意图。图6与图5的不同之处在于,在图6所示实施例中,译码模块52包括m个分段译码器521,以便并行地对m个第一码元序列进行译码处理。

99.图7是根据本公开又一个实施例的极化码译码器的结构示意图。如图7所示,极化码译码器包括存储器71、处理器72、通信接口73和总线74。

100.图7与图3的不同之处在于,在图7所示实施例中,处理器72被配置为基于存储器存储的指令执行实现如图4中任一实施例涉及的方法。

101.本公开还提供一种计算机可读存储介质。计算机可读存储介质存储有计算机指令,指令被处理器执行时实现如图4中任一实施例涉及的方法。

102.图8是根据本公开一个实施例的信息传输系统的结构示意图。如图8所示,信息传输系统包括信息发送端81和信息接收端82。信息发送端81中设置有极化码编码器83。信息接收端82中设置有极化码译码器84。极化码编码器83为图2和图3中任一实施例所述的极化码编码器,极化码译码器84为图5-图7中任一实施例所述的极化码译码器。

103.在一些实施例中,上述功能模块可以实现为用于执行本公开所描述功能的通用处理器、可编程逻辑控制器(programmable logic controller,简称:plc)、数字信号处理器(digital signal processor,简称:dsp)、专用集成电路(application specific integrated circuit,简称:asic)、现场可编程门阵列(field-programmable gate array,简称:fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件或者其任意适当组合。

104.至此,已经详细描述了本公开的实施例。为了避免遮蔽本公开的构思,没有描述本领域所公知的一些细节。本领域技术人员根据上面的描述,完全可以明白如何实施这里公开的技术方案。

105.虽然已经通过示例对本公开的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上示例仅是为了进行说明,而不是为了限制本公开的范围。本领域的技术人员应该理解,可在不脱离本公开的范围和精神的情况下,对以上实施例进行修改或者对部分技术特征进行等同替换。本公开的范围由所附权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。