1.本公开主张2020年5月21日申请的美国正式申请案第16/879,944号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

背景技术:

2.当存储器的密度提升时,一存储器元件的存储器胞是变得更加复杂且更容易出现许多缺陷。所述多个缺陷可造成元件错误及/或故障(failures)。在一些例子中,在存储器元件封装之前,所述多个存储器胞是正常的(normal)。在一些例子中,在存储器元件封装之后,是可发生所述多个故障。

3.在一先进存储器中,例如第4代双倍数据率随机存取存储器(double

‑

data

‑

rate ram version 4,ddr4),可包括一所谓的封装后修复(post package repair,ppr)功能。该ppr功能使一相容存储器控制器能够再分配来自一存储器模块的一缺陷列的多个存取(accesses)到为正常的存储器模块的一冗余列。

4.虽然ppr功能可使一存储器元件有效,而无须拆解存储器元件,修复工艺花费许多时间。因此,为了改善修复效率,有需要改善ppr功能。

5.上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明披露本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

技术实现要素:

6.本公开的一实施例提供一种操作一存储器元件的一封装后修复功能的方法。该方法包括提供一存储库(memory bank),该存储库包括一存储器阵列以及一感测放大器(sense amplifier),该感测放大器邻近该存储器阵列设置,其中该存储器阵列包括至少一缺陷列(defective row)以及至少一关联列(associated row),该至少一关联列通过多个位元线而电性连接到该感测放大器;配置一冗余列(redundant row)在邻近该存储器阵列处,其中该冗余列通过该多个位元线而电性连接到该感测放大器;启动该至少一关联列以传送在该至少一关联列中的数据到该感测放大器;闩锁该数据在该感测放大器中;启动该冗余列;以及传送该数据从该感测放大器到该冗余列。

7.在本公开的一些实施例中,该至少一关联列是依据联合电子设备工程委员会(jedec)标准而与该至少一缺陷列相关联。

8.在本公开的一些实施例中,该方法还包括:配置一列解码器在邻近该存储器阵列处,其中在启动该至少一关联列的该步骤中,该列解码器响应于一关联列位址。

9.在本公开的一些实施例中,在启动该冗余列的该步骤中,该列解码器响应于一冗余列位址。

10.在本公开的一些实施例中,该至少一关联列包括多个关联存储器胞,所述多个关联存储器胞是通过一关联字元线而连接。

11.在本公开的一些实施例中,该冗余列包括多个冗余存储器胞,所述多个冗余存储器胞通过一冗余字元线而连接。

12.在本公开的一些实施例中,该存储器元件包括一第4代双倍数据率同步随机存取存储器(double

‑

data

‑

rate fourth generation synchronous dynamic random access memory,ddr4 sdram)模块。

13.在本公开的一些实施例中,该存储器元件还包括一封装后修复(ppr)模块。

14.在本公开的一些实施例中,在启动该至少一关联列之前,是停用(deactivated)该至少一缺陷列。

15.在本公开的一些实施例中,在传送来自该感测放大器的数据到该冗余列之后,在该冗余列中的该数据是相同于在该至少一关联列中的该数据。

16.在本公开的一些实施例中,该方法还包括:确定该存储器元件是否进入一修复模式,该修复模式是响应于接收来自一存储器控制器的一或多个封装后修复命令(ppr commands)。

17.本公开的另一实施例提供一种关于在一封装后修复功能中的操作方法的存储器元件。该存储器元件包括一存储器阵列,包括至少一关联列以及至少一缺陷列;一感测放大器,其中该至少一关联列通过多个位元线而电性连接到该感测放大器;以及一冗余列,通过该多个位元线而电性连接到该感测放大器。

18.在本公开的一些实施例中,在该冗余列中的数据是相同于在该至少一关联列中的数据。

19.在本公开的一些实施例中,该至少一关联列依据联合电子设备工程委员会(jedec)标准而与该至少一缺陷列相关联。

20.在本公开的一些实施例中,该存储器元件还包括一列解码器,位于邻近该存储器阵列处,其中该列解码器响应于一关联列位址。

21.在本公开的一些实施例中,该列解码器响应于一冗余列位址。

22.在本公开的一些实施例中,该至少一关联列包括多个关联存储器胞,所述多个关联存储器胞通过一关联字元线而连接。

23.在本公开的一些实施例中,该冗余列包括多个冗余存储器胞,所述多个冗余存储器胞通过一冗余字元线而连接。

24.在本公开的一些实施例中,该存储器元件包括一第4代双倍数据率同步随机存取存储器(double

‑

data

‑

rate fourth generation synchronous dynamic random access memory,ddr4 sdram)模块。

25.在本公开的一些实施例中,该存储器元件还包括一封装后修复(ppr)模块。

26.依据jedec标准,在执行一软封装后修复(soft post package repair,sppr)之前,需要备份在一ddr4 sdram中的多个关联列。在本公开的一实施例中,因为没有读取操作执行在关联列上,所以不需要知道来自一中央处理单元(cpu)的所述多个关联列的位址信息。因此,当执行sppr功能时,在关联列中的数据不需要重写入到冗余列。反而,因为每一关联存储器胞以及每一冗余存储器胞经由相同的位元线而连接到一感测放大器,所以在关联列中的数据可直接复制到冗余列。因此,可排除重写入在关联列中的数据进入冗余列的操作,借此提升在关联列中的数据的备份效率。

27.上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得优选了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

附图说明

28.参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

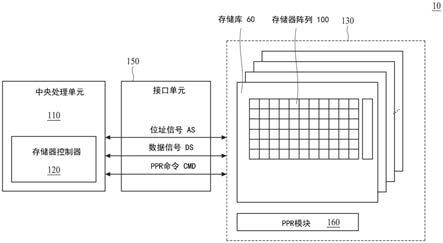

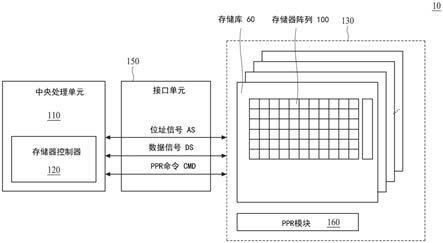

29.图1为依据本公开一些实施例的一电子系统的电路方框示意图。

30.图2为依据本公开一些实施例的该电子系统的外观方框示意图。

31.图3为依据本公开一些实施例的一存储器模块的一代表结构的外观示意图。

32.图4为依据本公开一些实施例的一存储库的一代表结构的外观示意图。

33.图5为依据本公开一些实施例的一存储器阵列的电路示意图。

34.图6为依据本公开一些实施例的图5的近观图。

35.图7为依据本公开一些实施例在所有存储器胞中具有多个分辨逻辑值的存储器阵列的外观示意图。

36.图8为依据本公开一些实施例中一感测放大器的操作原理的示意图。

37.图9为依据本公开一些实施例中被选择在一存储库内的一特定位址的程序的示意图。

38.图10为依据本公开一些实施例中描述一动态随机存取存储器的一读取操作的一方法的流程示意图。

39.图11为依据本公开一些实施例中遭受至少一缺陷的一存储器阵列的外观示意图。

40.图12为依据本公开一些实施例中多个冗余单元的一配置的示意图。

41.图13为依据本公开一些实施例在图2中的该存储库的示意图。

42.图14为依据本公开一比较的实施例在一软封装后修复功能中的一关联列备份程序的dram阵列示意图。

43.图15为依据本公开该比较的实施例在图14中多个关联列的备份完成的dram阵列示意图。

44.图16为依据本公开一实施例在一sppr功能中描述一关联列备份程序的一操作2000的一流程示意图。

45.图17到图19为依据本公开一实施例中该操作的每一阶段的dram阵列示意图。

46.附图标记说明:

47.10:电子系统

48.60:存储库

49.70:感测放大器

50.75:位址缓冲器

51.80:列解码器

52.85:输入/输出缓冲器

53.90:行解码器

54.95:时钟产生器

55.100:存储器阵列

56.101:存储器胞

57.101c:存储电容器

58.101t:存取晶体管

59.102:缺陷存储器胞

60.103:冗余单元

61.110:中央处理单元

62.112:正常列

63.114:缺陷列

64.116:关联列

65.118:冗余列

66.120:存储器控制器

67.130:存储器元件

68.132:存储器模块

69.134:存储器芯片

70.136:印刷电路板

71.138:数据垫

72.150:接口单元

73.160:封装后修复模块

74.200:存储器阵列

75.214:缺陷列

76.216:关联列

77.270:感测放大器

78.280:列解码器

79.1000:方法

80.2000:操作

81.as:位址信号

82.bl:位元线

83.bl0:位元线

84.bl1:位元线

85.bl2:位元线

86.bl3:位元线

87.bl_1~bl_11:位元线

88.bla_1~bla_11:位元线

89.blb_1~blb_11:位元线

90.cmd:封装后修复命令

91.df:缺陷

92.ds:数据信号

93.ra:关联列位址

94.rr:冗余列位址

95.s101:步骤

96.s102:步骤

97.s103:步骤

98.s104:步骤

99.s105:步骤

100.s200:步骤

101.s202:步骤

102.s204:步骤

103.s206:步骤

104.s208:步骤

105.sc1:关联存储器胞

106.sc2:冗余存储器胞

107.wl:字元线

108.wl0:字元线

109.wl1:字元线

110.wl2:字元线

111.wl3:字元线

具体实施方式

112.本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

113.应当理解,虽然用语“第一(first)”、“第二(second)”、“第三(third)”等可用于本文中以描述不同的元件、部件、区域、层及/或部分,但是这些元件、部件、区域、层及/或部分不应受这些用语所限制。这些用语仅用于从另一元件、部件、区域、层或部分中区分一个元件、部件、区域、层或部分。因此,以下所讨论的“第一装置(first element)”、“部件(component)”、“区域(region)”、“层(layer)”或“部分(section)”可以被称为第二装置、部件、区域、层或部分,而不背离本文所启示。

114.本文中使用的术语仅是为了实现描述特定实施例的目的,而并非限制本发明。如本文中所使用,单数形式“一(a)”、“一(an)”,及“该(the)”意欲亦包括多个形式,除非上下文中另作明确指示。将进一步理解,当术语“包括(comprises)”及/或“包括(comprising)”用于本说明书中时,所述多个术语规定所陈述的特征、整数、步骤、操作、元件,及/或组件的存在,但不排除存在或增添一或更多个其他特征、整数、步骤、操作、元件、组件,及/或上述各者的群。

115.此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一

个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所示出的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

116.随机存取存储器(ram)元件,是例如动态随机存取存储器(dram)元件,典型地使用如在计算装置(computing devices)中的主存储器。虽然在近年dram的操作速度已经改善,但是该速度并未达到用于存取一dram的一处理器的速度。在一计算装置中,举例来说,dram的缓慢速度以及周期时间是导致系统瓶颈,尽管系统的处理器的较快的操作速度,其是降低系统的处理能力(throughput)。

117.同步动态随机存取存储器(sdram)为一新款dram技术,其是主要使用一同步时钟(synchronous clock),以控制存储器的输入信号与输出信号。所述多个计算装置包括各式不同类型的sdram,例如ddr sdram。ddr为一存储器传输标准,且表示每一时钟周期有二传输。用于一ddr sdram的多个共用模块(common modules)具有至少一ddr sdram动态直插存储器模块(dimm)。由于技术的改善,在所述多个计算装置中的ddr sdram元件的容量(capacity)是以大大地成长。一ddr sdram亦追朔地称为ddrx sdram。其一系列的标准已包含ddr1到ddr2、ddr4以及ddr4。较新的存储器元件使用相对较新的标准。举例来说,相较于ddr3或ddr2 sdram,ddr4 sdram使用一较低电源供应电压以及较大带宽(bandwidth)。由于在电压标准与实体接口的不一致,所以不同标准是无法相互相容。

118.图1为依据本公开一些实施例的一电子系统10的电路方框示意图。图2为依据本公开一些实施例的该电子系统10的外观方框示意图。请参考图1,电子系统10包括一中央处理单元(cpu)110、一存储器控制器120以及一存储器元件130,存储器控制器120电性连接到中央处理单元110,存储器元件130电性连接到存储器控制器120。中央处理单元110为一装置,用于处理数据与执行来自一外部电路的程序要求,举例来说,外部电路为一计算装置的一主机板(motherboard)。存储器控制器120为一数字电路,其是管理往返于存储器元件130的多个程序要求,其中存储器元件130具有多个存储器模块132。在一些实施例中,如图1所示,存储器控制器120与中央处理单元110是分离的。在其他实施例中,如图2所示,存储器控制器120是与中央处理单元110整合在一起。

119.图3为依据本公开一些实施例的存储器模块132的一代表结构的外观示意图。请参考图3,存储器模块132可为多个dimm,其是采用多个存储器芯片134安装在一印刷电路板(pcb)136上的形式。存储器芯片134用于存储信息、数据或在一计算装置上执行的一程序。通常,存储器模块132包括十六个存储器芯片134,其是安装在印刷电路板136的两侧上。换言之,印刷电路板136的每一侧具有八个存储器芯片134,其中八个存储器芯片134的组合一般称为数据区域(rank)(或称为秩)。因此,存储器模块132总共具有两个数据区域。如图3所示,每一存储器芯片134包括堆叠在一起的多个存储库(banks)60。一存储库60为存储器控制器120可见的最小结构。多个区域60的组合可称为一存储库组(bank group)。每一存储库60与在数据库组中的其他存储库为各自独立操作。

120.请往回参考图2,电子系统10还包括一接口单元150,其是与存储器控制器120及存储器元件130相关联,与图1的架构相反,图1并没有接口单元。在一些实施例中,相较于图2,电子系统10可包括多更多或更少的元件。存储器元件130包括堆叠在一起的多个存储库60。在图2中的其中一个存储库60至少包括一存储器阵列100,其是可执行读取与写入操作,以

响应接收来自中央处理单元110或存储器控制器120的要求。接口单元150提供一接口在存储器控制器120与存储器元件130之间。更特别地,接口单元150提供在存储器控制器120与存储器元件130之间的信号的传输,而信号是例如位址信号as、数据信号ds或其他命令。当一读取操作或一写入操作执行在存储器元件130中时,为了读取来自存储器元件130的数据或是写入数据到存储器元件130中,针对一条需要信息(required information),中央处理单元110是定义一存储位址(memory address)。接着,存储器控制器120确定哪个存储器阵列100是与在多个存储库60之间的存储位址相关联。存储器控制器120可存取一存储器阵列100,其是基于接收来自中央处理单元110的存储位址进行存取。存储器控制器120传送一位址信号as,以存取存储器阵列100的一指定存储器位址(一指定列(row)及行(column))。因此,读取或写入操作可执行在指定的列与行。接下来,存储器控制器120可经由接口单元150传送一数据信号ds从存储器阵列100到中央处理单元110。在一实施例中,存储器元件130可包括一或多个存储器相关模块(memory

‑

related modules)。

121.仍请参考图2,存储器元件130还可包括一封装后修复(ppr)模块160。封装后修复模块160可执行一封装后修复功能,其是依据由存储器控制器120所发出的一封装后修复命令cmd所执行。接口单元150可提供封装后修复命令cmd在存储器控制器120与存储器元件130之间的传输。此外,可以响应于从存储器控制器120接收到一个或多个封装后修复命令cmd及/或位址信号as来确定存储器元件130是否要进入修复模式。在其他实施例中,封装后修复功能可由一控制器(图未示)所控制,而该控制器是在存储器元件130外部。在此实施例中,当存储器控制器120检测到一错误在存储器阵列100中时,存储器控制器120可发出一封装后修复命令cmd到存储器元件130。接下来,存储器元件130可允许一封装后修复序列(ppr sequence)修复该错误。

122.图4为依据本公开一些实施例的存储库60的一代表结构的外观示意图。请参考图4,每一存储库60具有一感测放大器70、一位址缓冲器(address buffer)75、一列解码器80、一输入/输出(i/o)缓冲器85、一行解码器90以及一存储器阵列100。多个位址信号是由位址缓冲器75所接收,并由列解码器80与行解码器90所解码,以存取存储器阵列100。通过使用感测放大器70感测在多个数据线(data lines)上的电压及/或电流变化,即可以从存储器阵列100读取。感测放大器70可读取并闩锁来自存储器阵列100的数据的一页面(page)(意即一列)。更特别是,感测放大器70经由多个位元线bl而电性连接到存储器阵列100。典型地,当存储在存储器阵列100中的数据输出时,数据是载入在所述多个位元线bl上,并由感测放大器70进行放大。接着,在所述多个位元线bl上的数据传送到输入/输出缓冲器85。在输入/输出缓冲器852上的数据经由多个数据垫138(如图3所示)而可传送到一外部装置。当输入数据时,数据输入路径是与如上所述的数据输出路径以相反顺序进行。存储库60还可包括一时钟产生器95,其是电性连接到感测放大器70、位址缓冲器75、列解码器80、输入/输出缓冲器85以及行解码器90。时钟产生器95为一电子电路,其是产生一时钟信号,以用于在dram中的同步操作。

123.图5为依据本公开一些实施例的存储器阵列100的电路示意图。请参考图5,存储器阵列100包括多个存储器胞101,所述多个存储器胞101是以一矩形矩阵配置。所述多个存储器胞101的每一列是通过一字元线连接,且所述多个存储器胞101的每一行是通过一位元线连接。在图5中,经由字元线wl0到wl3以及位元线bl0到bl3以组织并存取十六个存储器胞

101。

124.图6为依据本公开一些实施例的图5的近观图(close

‑

up view)。请参考图6,存储器胞101由一存取晶体管101t以及一存储电容器101c所组成,而存储电容器101c电性连接到存取晶体管101t。尤其是,存取晶体管101t通常为一nmos晶体管,其用于通过开启或关闭存取晶体管101t的栅极以控制到存储器胞101的通道(channel)。存储电容器101c用于存储信息,其是依据存储在其中的电荷(electrical charges)的状态进行存储。在一空(empty)状态的存储电容器101t是表示为一逻辑值0,而空状态是意即没有电荷。在一满电荷(full

‑

charges)状态的存储电容器101c是表示为一逻辑值1。以存储在存储电容器101c中的电荷的两个极端状态的方法,使存储器胞101存储一个位元的数据。请再参考图6,连接到存取晶体管101t的一字元线wl用于控制存取晶体管101t的栅极,其是通过施加一电压给存取晶体管101t以进行控制。一位元线bl是设置垂直于字元线wl,且亦连接到存取晶体管101t。当存取晶体管101t的栅极导通(turned on)时,存取晶体管101t连接存储电容器101c到位元线bl,以使存储在存储电容器101c中的逻辑值将被置放在位元线bl上。然而,存储在存储电容器101c中的电荷数量通常非常小,也因此在空状态与满电荷状态之间的差异是亦非常小。当晶体管101t启动(activated)时,在存储电容器101c中的电荷是与位元线bl共享。位元线bl的电容值(capacitance)是更加大于存储电容器101c的电容值。因此,位元线bl的电压变化微小,且需要分辨(resolve)在存储电容器101c中的确切状态。

125.图7为依据本公开一些实施例在所有存储器胞101中具有多个分辨逻辑值(resolved logic values)的存储器阵列100的外观示意图。请参考图7,来自列解码器90所提供的多个信号是传送到感测放大器70,且最终到存储器阵列100,其中感测放大器70经由所述多个位元线bl而耦接到所述多个存储器胞101的每一列。感测放大器70用于感测来自所述多个位元线bl的小电压及/或电流的变化,其是代表存储在存储器胞101中的一数据位元(1或0),然后放大该小电压到一可识别的逻辑电平(logic level),以便可正确地解读该数据。

126.图8为依据本公开一些实施例中感测放大器70的操作原理的示意图。在操作期间,感测放大器70连接到一邻近对的位元线bl1与bl2。感测放大器70拉起一特定列的位元线bl1与位元线bl2之间的小电压差,并放大存储在存储电容器101c中的信号。因此,无论存储在存储电容器101c中的数据为0或1,是可通过感测放大器70进行确定。感测放大器70的其他功能是即其亦当作一暂时数据存储元件(temporary data storage element)。举例来说,感测并放大包含在存储器胞101中的数据值之后,感测放大器70将继续驱动感测的数据值,直到存储器阵列100预先充电并准备好进行另一次存取。以这种方法,可以从感测放大器70存取在相同列的所述多个存储器胞101中的数据,而无须存取所述多个存储器胞101本身。因此,感测放大器70有效地当作一列缓冲器,其是保留住一整列的数据。因此,感测放大器70的一阵列亦可表示成一列缓冲器。

127.图9为依据本公开一些实施例中被选择在一存储库60内的一特定位址的程序的示意图。请参考图9,为了存储数据并读取来自存储器阵列100的数据,必须提供与数据相关联的列位址与行位址。提供给一存储器阵列100的一存储位址(x,y)是分为一列位址x以及一行位址y,其是分别由一列解码器80以及一行解码器902进行处理。列解码器80与行解码器90用于选择在阵列中的一特定存储位置,其是基于二位元列与行位址进行选择。列位址x与

行位址y是按序选择。尤其是,列位址是在行位址选择之前进行处理。在列解码器80选择一所欲的列之后,数据是传送到感测放大器70,而数据是存储在所选择的列的所选择的所述多个存储器胞101中。接下来,在使用行位址y选择一所欲的行之后,是确定在阵列内的的确切的交叉(x,y)。在此交叉处,一电容器存储一电荷,其是代表正在存取的数据。

128.图10为依据本公开一些实施例中描述动态随机存取存储器的一读取操作的一方法1000的流程示意图。请参考在图10中方法1000的步骤s101,首先,预先充电多个位元线到相同电压,其是介于高逻辑电平与低逻辑电平(1/2vdd)之间。举例来说,预先充电所述多个位元线到0.5v(若是低逻辑电平为0v且高逻辑电平为1v的话)。接下来,在步骤s102中,依据由一列解码器所获取的列位址以选择其中一列。在步骤s103中,确定所欲的列之后,通过施加一电压到所欲的列的一字元线已将其驱动到高逻辑电平,借此导通存取晶体管。这会造成存取晶体管为可导电的,且存储电容器因此经由存取晶体管而连接到位元线。在步骤s104中,若是存储值为1的话,然后一电荷是从存储电容器传送到与其连接的位元线;若是存储值为0的话,然后一电荷是从所连接的位元线传送到存储电容器。在步骤s105中,多个感测放大器是将该电压与临界值比较,以确定该电压是否表示逻辑1或逻辑0。在dram中的读取程序是具有破坏性的,因为其是移动存储在一整列中的所述多个存储器胞中的电荷。在发送位元从一单一行到输出之前,在一芯片上的感测放大器需要重写入数据到所存取的列。

129.在dram的一典型写入操作中,如在一读取操作中,是确定列位址。接着,是施加一电压到位元线,并将被传送到电容器,且被存储在其中。接下来,数据将被提供到感测放大器与行解码器。最后,数据将被提供到所述多个存储器胞,而所述多个存储器胞是位于先前所选的字元线上。旧的数据是被新的数据所取代。总而言之,写入操作解码位址,是以类似读取操作的方式进行。

130.数据作为电荷而是存储在存储电容器中,但所述多个电荷会随时间泄漏。由于存储电容器有随时间流逝而失去电荷的趋势,所以为了维持存储在电容器中的数值,需要周期地更新(periodically refreshed)所述多个存储器胞。每一存储器胞是以dram标准指定的更新间隔而周期地更新。确切的更新间隔是取决于dram形态(意即ddr)以及操作温度。当政在更新dram时,是无法存取dram。

131.当dram尺寸缩减时,所述多个存储器胞的制造与封装变得更困难且容易出现缺陷。所述多个缺陷通常来自制造环境,并可能造成所述多个存储器胞运行不正常,进而造成元件错误及/或故障。存储器元件可具有多个缺陷胞(defective cells)、多个缺陷列(defective rows)或多个缺陷行(defective columns)。在一些例子中,在存储器元件封装之前,所述多个存储器胞是正常的。在一些例子中,在存储器元件以晶封装之后,仅检测到一些故障。封装类型的例子包括环氧树脂囊封(epoxy encapsulation)、陶瓷封装、金属或玻璃封装及类似物。在大部分的情况下,在一存储器元件已经封装之后,举例来说,其是仅可存取封装的多个引脚(pins)到存储器元件。因此,若是在测试期间发现已封装的存储器元件包含多个缺陷存储器胞的话,其是不可能实体取代所述多个缺陷存储器胞。为了改善整体良率并降低成本,其是希望在一存储器元件封装之后能够将其修复。

132.图11为依据本公开一些实施例中遭受至少一缺陷的一存储器阵列100的外观示意图。请参考图11,是表示在存储器阵列100中的一缺陷df。缺陷df可影响一些存储器胞101的

操作。那些无法正常操作的存储器胞101是表示成多个缺陷存储器胞102。为了解决在存储器元件封装之后才发现缺陷df,多个存储器模块的制造厂包括多个冗余单元(redundant units)110,其是邻近存储器阵列100设置并为了取代所述多个缺陷存储器胞102,借此延长一存储器元件的生命周期(lifetime)。举例来说,每一冗余单元103可包括多个冗余列或多个冗余行。由于所述多个冗余单元103,存储器元件仍可为缺陷的,而不需要将其拆解。为了避免所述多个缺陷影响存储器的生产良率,所述多个冗余单元103为一共同使用技术。

133.在ddr4 sdram元件中,是介绍称为封装后修复(ppr)的一技术。ppr使一存储器元件能够在其封装之后被修复。在ddr4的jedec标准中,几乎所有主流存储器制造商军支援ppr功能。ppr具有追踪资源可用性的能力。dram元件确保在启动时在每一存储库中的ppr资源的可用性。可测试存储器元件以确认所述多个缺陷单元。举例来说,所述多个缺陷单元可包括多个缺陷胞、多个缺陷列或多个缺陷行。ppr的原理即在一存储器元件已经封装之后,以一冗余单元取代一缺陷单元。ppr功能可通过使用所述多个冗余存储器胞而提供改善可靠度与可用性,所述多个冗余存储器胞通常配置成在一dram元件中的每一个存储库的大量冗余列。

134.图12为依据本公开一些实施例中多个冗余单元103的一配置的示意图。请参考图12,组织有四个存储器阵列100。在一些实施例中,所述多个存储器阵列100是配置成一矩阵(matrix)架构,且所述多个冗余单元103是位于所述多个存储器单元100的一周围。在一实施例中,两个冗余单元103是并排设置。在一实施例中,一对冗余单元103是位于存储器阵列100的旁边。在一实施例中,一对冗余单元103是位于两个存储器阵列100的旁边。

135.再者,ppr亦支援硬(hppr)及软(sppr)模式,其是分别对应永久及暂时修复。hppr为非挥发性的;然而sppr为挥发性的,其是指该修复将在元件的电源重设(reset)之后进行清除(cleared)。sppr可表示非持续的(non

‑

persistent)但为实时的ppr方法。在一芯片的生命周期期间,内部存储持续老化且可能发生存储问题。当发生这些问题时,优选地是可自动修复该存储,例如使用sppr功能。由于sppr,缺陷单元的位址数据在存储器元件封装之后可以存储在一存储器元件中,而位址数据是例如一缺陷列。sppr功能可依据其位址而修复该缺陷列,而该位址是在存储器元件封装中界定成缺陷列。除了该缺陷列之外,jedec标准需要必须在一sppr功能之前备份在一ddr4 sdram的一存储库中的一些特定列,以修复该缺陷列,而所述多个特定列是表示成关联列。

136.图13为依据本公开一些实施例在图2中的存储库60的示意图。请参考图2及图13,存储器阵列100至少包括多个正常列112、多个缺陷列114、多个关联列116以及多个冗余列118。所述多个缺陷列114为多个列,所述多个列可包含多个缺陷,而所述多个缺陷是将导致元件错误及/或故障。所述多个关联列116是依据jedec标准而关于改等缺陷列114。所述多个冗余列118为多个闲置列(spare rows),所述多个闲置列是由制造商所设计,以取代在存储器阵列100中的一或多个缺陷列114。

137.图14为依据本公开一比较的实施例在一软封装后修复(sppr)功能中的一关联列备份程序(associated row backup process)的dram阵列示意图。请参考图14,所述多个冗余列114是与存储器阵列100分离的,且不专用于存储器阵列100。反而是,无论何时需要执行sppr功能,即是分配所述多个冗余列118。在该比较的实施例中,如图14所示,有三个关联列116以即依个缺陷列114。每一关联列116连接到位元线bla_1到bla_11,每一冗余列118连

接到位元线blb_1到blb_11,而位元线blb_1到blb_11是不同于位元线bla_1到bla_11。在检测到具有在存储器阵列100中的多个存储器胞(在图14中以黑色圆型标示)的缺陷列114之后,所述多个关联列116将在执行一sppr功能之前自动进行备份。在sppr序列期间,在所述多个关联列116中的所有数据是需要重写入所述多个分离的冗余列118。首先,需样获取在所述多个关联列116中的原始数据;意即,需样一读取操作以读取其所有数据。接下来,所述多个关联列116的数据是重写入到所述多个分离的冗余列118。

138.图15为依据本公开该比较的实施例在图14中多个关联列的备份完成的dram阵列示意图。请参考图14及图15,如图15所示的分隔的所述多个冗余列118包含来自所述多个关联列116的数据。因此,在此时,所述多个冗余列118具有如同所述多个关联列116的相同的数据。由于需要重写入数据从所述多个关联列116到所述多个冗余列118,所以在比较的实施例中的包装后修复程序中,关联列的备份程序是耗时的(time

‑

consuming)。

139.图16为依据本公开一实施例在一sppr功能中描述一关联列备份程序的一操作2000的一流程示意图。操作2000包括一步骤s200,即指定一冗余列;一步骤s202,即启动一关联列;一步骤s204,即传送存储在该关联列中的数据到一感测放大器;一步骤s206,即启动该冗余列;以及一步骤s208,即传送被该感测放大器所闩锁的该数据到该冗余列。

140.接下来是描述依据本公开一些实施例的操作2000的一例示程序流程。图17到图19为依据本公开一实施例中该操作2000的每一阶段的dram阵列示意图。请参考图17,一存储库60至少包括一存储器阵列200、一感测放大器270以及一列解码器280,感测放大器270邻近存储器阵列200设置,列解码器280邻近存储器阵列200设置。在一实施例中,感测放大器270电性连接到存储器阵列200。在一实施例中,列解码器280电性连接到存储器阵列200。在一实施例中,存储器阵列200可包括至少一缺陷列214以及至少一关联列216。至少一缺陷列214与至少一关联列216通过多个位元线bl_1到bl_11而电性连接到感测放大器270。尤其是,至少一关联列216包括多个关联存储器胞sc1,其是通过一关联字元线wl1而连接。依据jedec标准,至少一关联列与一缺陷列相关联,且在至少一关联列中的数据必须在一封装后修复执行之前进行备份。在一些实施例中,可在一封装后修复程序开始之前停用至少一缺陷列214。

141.操作2000可在步骤s200开始,其中是指定一冗余列218以配置在邻近存储器阵列200处。在一实施例中,冗余列218是设置在邻近至少一关联列216处。冗余列218电性连接到感测放大器270。尤其是,冗余列218包括多个冗余存储器胞sc2,其是通过一冗余字元线wl2而连接。冗余存储器胞sc2经由多个位元线bl_1到bl_11而电性连接到所述多个关联存储器胞sc1,且还电性连接到感测放大器270。

142.在步骤s202,是启动一特定关联列216。尤其是,在启动特定关联列216的步骤中,列解码器270是响应于一关联列位址ra。

143.在步骤s204,在关联列216启动之后,在关联列216中的数据是经由多个位元线bl_1到bl_11而传送到感测放大器270。感测放大器270感测并放大从关联列216所传送的数据。在此时,感测放大器270暂时闩锁先前存储在关联列216中的数据。

144.在步骤s206,是启动一冗余列218。尤其是,在启动冗余列218步骤中,列解码器280响应于一冗余列位址rr。

145.在步骤s208,在冗余列218启动之后,存储在感测放大器280中的数据是经由多个

位元线bl_1到bl_11而传送到冗余列218。当备份程序完成时,如图19所示,在冗余列218中的数据是相同于在关联列216中的数据。在一些实施例中,操作2000还包括确定存储器元件是否进入一修复模式,以响应于接收来自一存储器控制器的一或多个ppr命令(commands)。

146.在本公开的一实施例中,因为没有读取操作执行在关联列216上,所以不需要知道来自一cpu的关联列216的位址信息。因此,当执行一封装后修复功能时,在关联列216中的数据不需要重写入冗余列218。反而是,因为每一关联存储器胞sc1与每一冗余存储器胞sc2经由例如位元线bl_1的相同位元线而连接到感测放大器270,所以在关联列216中的数据可直接复制到冗余列218。在感测放大器270分辨包含在关联列216中的所述多个关联存储器胞sc1中的数据之后,该数据是已存储在感测放大器270,并可直接传送到在冗余列218中的所述多个冗余存储器胞sc2。

147.本公开的一实施例提供一种操作一存储器元件的一封装后修复功能的方法。该方法包括提供一存储库,该存储库包括一存储器阵列以及一感测放大器,该感测放大器邻近该存储器阵列设置,其中该存储器阵列包括至少一缺陷列以及至少一关联列,该至少一关联列通过多个位元线而电性连接到该感测放大器;配置一冗余列在邻近该存储器阵列处,其中该冗余列通过该多个位元线而电性连接到该感测放大器;启动该至少一关联列以传送在该至少一关联列中的数据到该感测放大器;闩锁该数据在该感测放大器中;启动该冗余列;以及传送该数据从该感测放大器到该冗余列。

148.本公开的另一实施例提供一种关于在一封装后修复功能中的操作方法的存储器元件。该存储器元件包括一存储器阵列,包括至少一关联列以及至少一缺陷列;一感测放大器,其中该至少一关联列通过多个位元线而电性连接到该感测放大器;以及一冗余列,通过该多个位元线而电性连接到该感测放大器。

149.依据jedec标准,在执行一软封装后修复(sppr)之前,需要备份在一ddr4 sdram中的多个关联列。在本公开的一实施例中,因为没有读取操作执行在关联列上,所以不需要知道来自一中央处理单元(cpu)的所述多个关联列的位址信息。因此,当执行sppr功能时,在关联列中的数据不需要重写入到冗余列。反而,因为每一关联存储器胞以及每一冗余存储器胞经由相同的位元线而连接到一感测放大器,所以在关联列中的数据可直接复制到冗余列。因此,可排除重写入在关联列中的数据进入冗余列的操作,借此提升在关联列中的数据的备份效率。

150.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的构思与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

151.再者,本公开的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤是包含于本公开的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。