1.本实用新型涉及数据传输相关技术领域,更具体的说是涉及一种高性能的蓝牙模块。

背景技术:

2.蓝牙模块就是应用蓝牙技术的免持耳机,它能让使用者免除电线的牵绊,自在地以各种方式轻松地使用耳机。蓝牙模块自从问世以来,一直是行动商务族提升效率的好工具,它有单声道、立体声、真无线三个种类,包括hsp、 hfp、a2dp三种规格。

3.随着无线蓝牙的标准越来越高,从蓝牙4.0到蓝牙5.0,传输的速度也越来越高。现在用于蓝牙的音频标准从早期蓝牙4.x的sbc,aac,aptx等,已经出现了24bit96khz的ldac,lhdc,aptx

‑

hd等,随着这类协议的支持,传输音频的数据量越来越大,已经超越了无损音质的要求,走向了高清音频,失真越来越低。不仅满足了普通消费者的音频需要,深度音乐爱好者以及发烧友也对高清蓝牙产生了浓厚的兴趣。

4.目前蓝牙芯片到模拟输出,有二种方式,一种是直接从蓝牙芯片内存da 芯片,模拟输出,一种是基于i2s的标准数字音频输出,外接更高性能的da 芯片,从而获得更好的质量。但现有技术中,因为蓝牙i2s质量不高,高清蓝牙,从32khz~96khz均支持,原蓝牙的锁相环精度是完全达不到真正高保真的 i2s要求,哪怕后端采用高端的解码方案,也使得蓝牙的音质无法与真正的hifi 高端的数字重放或cd机对比。因此研发一种高保真高清的蓝牙是本领域技术人员亟需解决的问题。

技术实现要素:

5.有鉴于此,本实用新型提供了一种高性能的蓝牙模块,用于解决现有技术中蓝牙模块失真问题的发生。

6.为了实现上述目的,本实用新型采用如下技术方案:

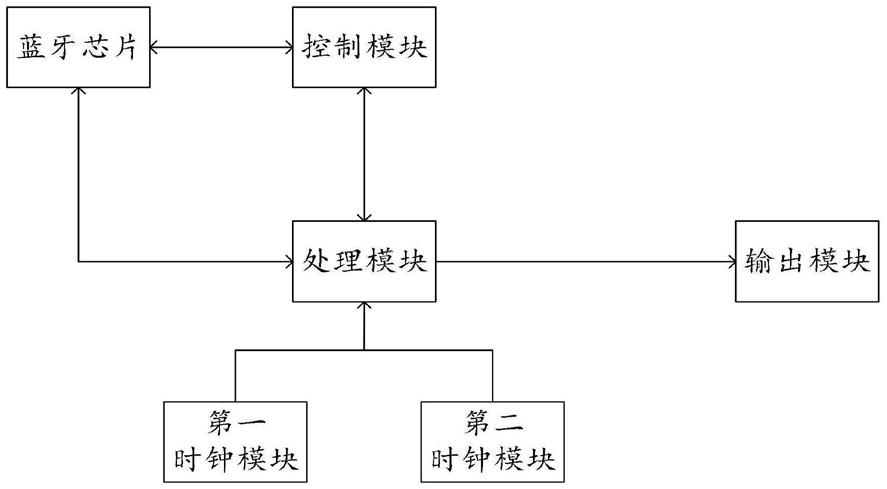

7.一种高性能的蓝牙模块,包括蓝牙芯片、控制模块、处理模块、第一时钟模块、第二时钟模块、输出模块;所述蓝牙芯片分别与所述控制模块、所述处理模块连接;所述处理模块分别与所述第一时钟模块、第二时钟模块、所述输出模块、所述控制模块连接;

8.所述控制模块用于接收所述蓝牙芯片发出的中断信息以及采样信息;

9.所述处理模块用于接收所述控制模块的采样信息以及所述蓝牙芯片的传输信息;并根据接收的所述第一时钟模块和所述第二时钟模块的时钟信息生成对应的i2s时钟信息;将所述i2s时钟信息与所述传输信息发送至所述输出模块;

10.所述第一时钟模块和所述第二时钟模块用于为所述处理模块提供固定频率的倍频时钟信号;

11.所述输出模块用于将从所述处理模块接收的信息转换为模拟信息输出。

12.优选的,所述采样信息包括采样率。

13.优选的,所述处理模块将传输信息与i2s时钟信息对齐生成数字i2s信息,并将数

字i2s信息传送至输出模块。

14.优选的,所述处理模块采用独立的高性能电源。

15.其优点在于,采用独立的高性能电源降低了音频区域的相位噪声以及提高了时钟精度。

16.优选的,所述处理模块包括dsp或frga。

17.经由上述的技术方案可知,与现有技术相比,本实用新型公开提供了一种高性能的蓝牙模块,通过两个独立的倍频双时钟以及从蓝牙芯片直接获取数据信息,解决了蓝牙芯片i2s时钟质量差的问题;通过独立的高性能电源,从而明显降低了音频区域的相位噪声以及提高了时钟精度。

附图说明

18.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

19.图1附图为本实用新型的结构示意图;

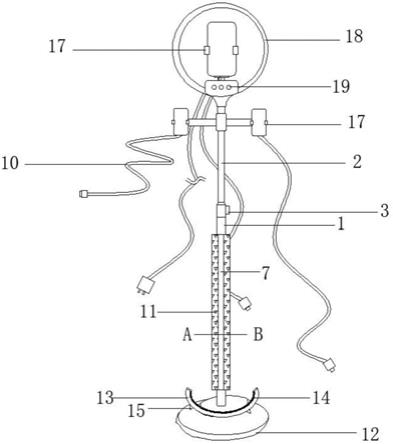

20.图2附图为本实用新型的实施例的具体结构示意图;

21.图3附图为本实用新型的实施例的电路图。

具体实施方式

22.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

23.本实用新型实施例公开了一种高性能的蓝牙模块,如图1所示,包括蓝牙芯片、控制模块、处理模块、第一时钟模块、第二时钟模块、输出模块;所述蓝牙芯片分别与所述控制模块、所述处理模块连接;所述处理模块分别与所述第一时钟模块、所述第二时钟模块、所述输出模块、所述控制模块连接;蓝牙芯片采用高通蓝牙5.0芯片,控制模块为mcu,处理模块为独立的 dsp或frga,或是含有dsp的装置,输出装置为dac,时钟为 11.2896mhz/22.5792mhz和12.288mhz/24.576mhz的时钟。

24.本实施例采用独立的44.1khz,48khz倍频的双音频超低噪声高精度时钟单独通过dsp或fpga输出i2s三个时钟(mclk,lrclk,bclk),同时数据从蓝牙芯片获取,解决了蓝牙芯片i2s时钟质量差的问题。

25.如图2所示,mcu是协调蓝牙芯片与dsp/fpga的工作,同时dsp/fpga 外部输入的两个音频级高性能时钟(低噪声,低抖动),直接用于i2s整数分频,从而保证i2s质量,直接输出给dac,同时dsp/fpga从蓝牙芯片处取得音频数据,并且从mcu处得知目前数据的采样率,位数信息。

26.播放的流程为:

27.蓝牙芯片主动发出中断给mcu,告之有新的音频数据到来,mcu同时读取蓝牙给出

的采样率,位数等信息,发送到dsp/fpga,fpga则采用对应的时钟生成i2s所需的时钟,同时将蓝牙的数据与时钟对齐,发射到dac。

28.具体为:当用户通过蓝牙播放24bit,88.2khz的音乐,蓝牙首先告之有新的数据与采样信息到来,mcu通过中断读取这些信息,通知dsp或fpga, dsp/fpga采直接采用11.2896mhz/22.5792mhz(此频率是88.2khz的倍数关系)倍数合成对应的i2s,并且与蓝牙的数据通读渠道取得数据,与i2s时钟对齐后发射到dac,从而完成了蓝牙i2s的质量改造。

29.因为独立的倍频双时钟,没有任何锁相环,同时dsp/fpga独立采用高性能的电源,降低了音频区域的相位噪声以及提高了时钟精度,充分发挥出高端da芯片的性能。

30.本实施例蓝牙芯片采用csr8675蓝牙5.0芯片模块;时钟采用频率为 22.5792mhz,24.576mhz的双时钟;dsp采用包含dsp的akm4490da芯片。

31.具体电路图为:

32.蓝牙5.0芯片上的引脚1与电阻r5的一端连接,电阻r5的另一端与电容c163的一端连接,电容c163的另一端与分别连接电阻r225、电阻r226 的一端,电阻r225的另一端与引脚10连接,电阻r226的一端接地;从电阻 r225、电阻r226与电容c163连接端引出线与引脚2、引脚3分别与fpga 连接;

33.电容c114一端与引脚10连接,另一端与引脚11连接;引脚10为电源端,引脚11为接地端;

34.引脚16、引脚17、引脚18、引脚29分别与mcu连接;

35.引脚19、引脚20与led连接;

36.电阻r57与引脚22连接,输出1.8v电源;

37.电感l1一端与引脚39连接,一端与电容c145的一端连接,电容c145 的另一端与引脚38连接,引脚39与引脚38之间连接有电容c99;

38.引脚11、引脚30、引脚40均接地。

39.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

40.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本实用新型。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本实用新型的精神或范围的情况下,在其它实施例中实现。因此,本实用新型将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。