一种sram型fpga用户寄存器单粒子翻转故障注入方法

技术领域

1.本发明属于卫星电子系统技术领域,涉及一种sram型fpga用户寄存器单粒子翻转故障注入方法。

背景技术:

2.为了满足大容量、高速、复杂信息处理、在轨可重构等要求,现有卫星电子系统中大量采用了sram型fpga。sram型fpga属于单粒子敏感器件,必须采取单粒子效应防护措施。

3.目前在卫星电子系统中,所采取的sram型fpga的典型防护措施为定时刷新和三模冗余。在工程实施过程中,时常出现防护措施不到位的情况,例如:(1)刷新功能设计存在隐患,造成不刷新、刷新不完整、或误刷新的情况;(2)三模冗余设计存在缺陷,导致重要寄存器三模冗余设计不完整;(3)fpga功能要求越来越复杂,但fpga资源有限,只能选取部分重要寄存器进行三模冗余设计。而人为评估得到的重要寄存器可能存在偏差,导致重要寄存器遗漏,造成一定程度的单粒子翻转隐患。

4.开展sram型fpga单粒子故障注入试验,可以识别上述设计隐患。现有技术中的单粒子故障注入系统,主要借助selectmap或jtag接口向sram型fpga顺序或随机地注入配置数据故障码流。配置数据主要对应的是fpga中的逻辑电路、连通状态等信息,通过配置数据顺序或随机的注入方式并不能准确快速地改变用户寄存器的暂存值。目前公开文献中均没有直接针对sram型fpga用户寄存器进行故障注入的相关信息。

技术实现要素:

5.本发明公开一种sram型fpga用户寄存器单粒子翻转故障注入方法,能够对sram型fpga用户寄存器中的暂存值进行直接的修改,实现sram型fpga用户寄存器的单粒子翻转故障的模拟。

6.本发明通过以下技术方案实现。

7.一种sram型fpga用户寄存器单粒子翻转故障注入方法,包括:

8.分析fpga用户寄存器中复位初值参数和复位极性参数的真值表,获得可将用户寄存器暂存值直接设置为“0”或“1”的真值表项;

9.获取所述用户寄存器复位初值参数、复位极性参数在配置位流数据中的偏移量;

10.通过感兴趣用户寄存器的x、y坐标信息和用户寄存器复位初值参数、复位极性参数的位流偏移量关系,获得感兴趣寄存器故障位流偏移量;

11.根据所述感兴趣寄存器故障位流偏移量进行用户寄存器单粒子翻转故障注入。

12.本发明的有益效果:

13.本发明可获得将用户寄存器直接设置为“0”或“1”的控制参数真值表项。可获得fpga寄存器控制参数在配置位流中的准确偏移量。结合xdl文件中的寄存器x、y坐标信息,得到fpga代码中感兴趣寄存器的准确偏移量。从而可以通过selcetmap或jtag接口对感兴趣寄存器进行快速故障注入。大幅度提高sram型fpga单粒子翻转故障注入效率和准确度,

更有效地识别fpga中用户寄存器单粒子翻转防护中的隐患。

附图说明

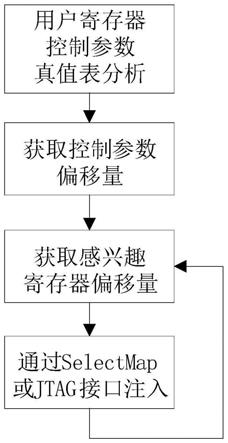

14.图1为本发明sram型fpga用户寄存器单粒子翻转故障注入方法流程图;

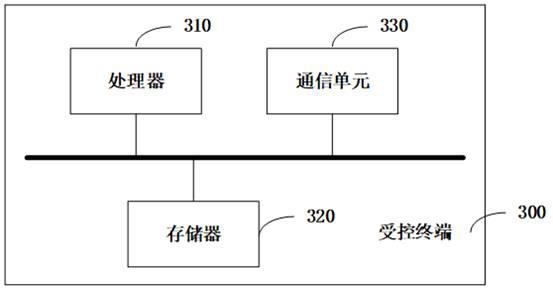

15.图2为本发明具体实施方式中用户寄存器的基本结构图;

16.图3为本发明具体实施方式中用户寄存器单粒子翻转故障注入流程图。

具体实施方式

17.下面结合附图对本发明做进一步说明。

18.如图1所示,本具体实施方式的一种sram型fpga用户寄存器单粒子翻转故障注入方法,包括:

19.步骤一、分析fpga用户寄存器中复位初值参数和复位极性参数的真值表,获得可将用户寄存器暂存值直接设置为“0”或“1”的真值表项;

20.在具体实施时,sram型fpga中的用户寄存器分布于fpga中的slice、iob等部件中。用户寄存器的基本结构如图2所示。用户寄存器有一个复位信号控制端sr,sr控制端的上游有个复位信号极性控制元件,用于控制sr信号的极性,即决定是高电平复位还是低电平复位,该极性控制元件的控制参数可选设置值为:sr、sr_b,该参数可命名为复位极性参数。用户寄存器中包含一个复位初值参数,用于设置复位期间用户寄存器的默认值,该控制参数可选设置值为:srhigh、srlow。

21.当用户寄存器正常运行时,复位信号控制端sr处于非复位状态,此时将复位极性参数取反:(1)原来设置值为sr时,修改为sr_b,(2)原来设置值为sr_b时,修改为sr,则可将用户寄存器的复位控制端sr设置为复位状态。再通过修改复位初值参数,选择srlow或srhigh。可将用户寄存器设置为所期望的

‘0’

或

‘1’

。

22.下表1所示为用户寄存器关于复位初值参数、复位极性参数的真值表。通过表中第3、4项可将用户寄存器暂存值设置为“0”,通过表中第7、8项可将用户寄存器暂存值设置为“1”。

23.表1用户寄存器真值表

[0024][0025]

步骤二、获取用户寄存器复位初值参数、复位极性参数在配置位流数据中的偏移量;

[0026]

本实施例中,所述复位初值参数在配置位流中的偏移量采用下述步骤进行获取:

[0027]

(a)在fpga开发环境ise中编译原始用例,并使用bitgen工具生成原始配置位流数据,标记为配置数据1;

[0028]

(b)在fpga开发环境ise中,打开fpga editor工具,浏览并找到目标寄存器,打开目标寄存器内部结构图;

[0029]

(c)设置fpga editor属性为可编辑状态;

[0030]

(d)修改复位初值参数,设置为与原有状态相反的状态;即原为srhigh时,修改为srlow。原为srlow时,修改为srhigh;

[0031]

(e)保存设置状态,并通过ise bitgen工具生成配置位流数据,标记为配置数据2;

[0032]

(f)逐位比较配置数据1、配置数据2的数据,获得复位初值参数在配置位流数据中的偏移量,标记为sr_offset;

[0033]

(g)在fpga editor中找到相邻行列的用户寄存器,并重复上述步骤(a)~(f),获得相邻行列寄存器复位初值参数在配置位流中的偏移量。

[0034]

在具体实施时,相邻的上下左右四个方向的寄存器偏移量标记为sr_offset_up、sr_offset_down、sr_offset_left、sr_offset_right,根据所述sr_offset、sr_offset_up、sr_offset_down、sr_offset_left、sr_offset_right获得相邻行列控制参数的偏移量的增量,继而推算出所有用户寄存器中复位初值参数在配置位流数据中的偏移量。

[0035]

本实施例中,所述复位极性参数在配置位流数据中的偏移量采用下述步骤进行获取:

[0036]

(a)在fpga开发环境ise中编译原始用例,并使用bitgen工具生成原始配置位流数据,标记为配置数据3;

[0037]

(b)在fpga开发环境ise中,打开fpga editor工具,浏览并找到目标寄存器,打开其目标寄存器内部结构图;

[0038]

(c)设置fpga editor属性为可编辑状态;

[0039]

(d)修改复位极性参数,设置为与原有状态相反的状态;即原来设置值为sr时,修改为sr_b,原来设置值为sr_b时,修改为sr;

[0040]

(e)保存设置状态,并通过ise bitgen工具生成配置位流数据,标记为配置数据4;

[0041]

(f)逐位比较所述配置数据3、配置数据4的数据,可获得复位极性参数在配置位流数据中的偏移量,标记为pol_offset。

[0042]

(g)在fpga editor中找到相邻行列的用户寄存器,并重复上述步骤(a)~(f),获得相邻寄存器复位极性参数在配置位流中的偏移量。

[0043]

在具体实施时,相邻的上下左右四个方向的寄存器偏移量标记为pol_offset_up、pol_offset_down、pol_offset_left、pol_offset_right。根据pol_offset、pol_offset_up、pol_offset_down、pol_offset_left、pol_offset_right获得相邻行列控制参数的偏移量的增量,继而推算出所有用户寄存器中复位极性参数在配置位流数据中的偏移量。

[0044]

步骤三、通过感兴趣用户寄存器的x、y坐标信息和用户寄存器复位初值参数、复位极性参数的位流偏移量关系,获得感兴趣寄存器故障位流偏移量。

[0045]

本实施例中,具体包括以下步骤:

[0046]

(a)从fpga源代码中获取感兴趣用户寄存器的名称;

[0047]

(b)通过ise自带的xdl.exe工具,将fpga工程网表ngc文件,转换为xdl文件格式;转换命令示例为:xdl

‑

ncd2xdlfilename.ncdfilename.xdl;

[0048]

(c)在fpga编译环境的工程文件夹找到xdl文件,通过文本表编辑器打开所述xdl文件,查询所述xdl文件中感兴趣用户寄存器中的布局信息,获得感兴趣用户寄存器的x、y坐标信息;xdl文件中寄存器坐标信息示例:inst"reg""slice",placed r20c36 slice_x71y88,表示寄存器reg坐标信息为横坐标x:71、纵坐标y:88;

[0049]

(d)通过所述感兴趣用户寄存器的x、y坐标信息和用户寄存器复位初值参数、复位极性参数的位流偏移量关系,获得fpga代码中感兴趣用户寄存器故障注入所需的故障位流偏移量。

[0050]

步骤四、根据所述感兴趣寄存器故障位流偏移量进行用户寄存器单粒子翻转故障注入。

[0051]

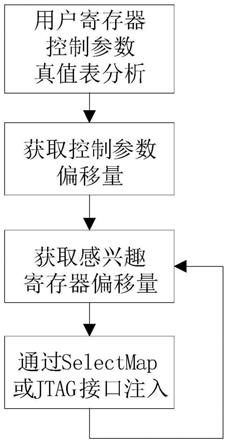

如图3所示,本实施例中,所述故障注入采用故障注入器通过注入接口向sram型fpga注入配置数据。

[0052]

所述注入配置数据包括原始配置数据和故障配置数据,用于对比正常情况和异常情况下fpga的工作状态;所述注入接口包括selectmap和jtag接口。

[0053]

在具体实施时,步骤一、二仅进行一次,步骤三、四可以重复进行。

[0054]

综上所述,以上仅为本发明的典型实例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。