1.本发明涉及光子芯片,并且涉及硅光子芯片中不同高度的组件的耦合。

背景技术:

2.在光子芯片的领域中,经常有必要光学耦合不同尺寸的波导或将波导耦合到其他光学组件,诸如光纤。

3.锥形波导,诸如liao, chun

‑

wei等人的“fiber

‑

core

‑

matched three

‑

dimensional adiabatic tapered couplers for integrated photonic devices”《光波技术期刊》29.5 (2011):770

‑

774中示出的那些,已经被用于这种效果。在该文献中,锥形件的一个端部耦合到大组件,并且锥形件的相对端部耦合到较小组件。3

‑

d锥形件的宽度和高度从耦合到大组件的端部到耦合到小组件的端部逐渐减小。使用3

‑

d锥形件,可以减少由大组件和小组件之间的界面引起的损耗。

4.然而,由于跨芯片的顶表面高度的变化,这样的芯片可能难以随后处理,例如使用化学机械抛光(cmp)。

5.本发明是根据以上考虑而设计的。

技术实现要素:

6.在第一方面,本发明提供了一种光子芯片,包括:硅衬底、在硅衬底上方的低折射率层和在低折射率层上方的锥形波导,锥形波导在锥形波导的第一端部处具有第一高度,并且在锥形波导的第二端部处具有第二高度,第二高度大于第一高度,并且锥形波导具有底表面,该底表面在第二端部处比在第一端部处更靠近衬底。

7.在本技术中,低折射率意味着折射率低于锥形波导的折射率。例如,如果波导由硅形成,则低折射率将是小于硅的折射率的折射率。例如,在1200

‑

8500nm的波长下,低折射率可以小于3.4。通过具有低折射率,低折射率层可以将光限制在波导内。

8.替换地或附加地,本技术中的任何低折射率层可以是绝缘层。此外,在本技术中使用术语绝缘层的情况下,这样的层可以替换地或附加地是低折射率层。

9.由于锥形件的底表面在第二端部比第一端部更靠近衬底,波导的锥形形状至少部分地掩埋在芯片中。这使得锥形件的顶表面能够相对于芯片上的其他波导或器件层的顶表面具有较小的倾斜或没有倾斜,并且因此使得芯片的处理能够更容易。

10.通过从大组件传递穿过锥形波导从第二端部到第一端部然后进入较小组件,光可以传递穿过锥形波导从大组件(例如波导或光纤)到较小组件(例如波导);或者通过从小组件传递穿过锥形波导从第一端部到第二端部然后进入大组件,光可以传递穿过锥形波导从小组件到较大组件。通过传递穿过锥形波导,减小了小组件和大组件之间的光损耗。

11.层或波导的高度是在远离衬底的方向上测量的。层或波导的顶表面是离衬底最远的表面,并且层或波导的底表面是离衬底最近的表面。例如,锥形波导的高度是在正交于衬底表面的方向上从锥形波导的底表面到锥形波导的顶表面测量的。波导的宽度是在垂直于

高度并且垂直于光沿波导传播的方向的方向上测量的。波导的长度是在垂直于高度并且平行于光沿波导传播的方向的方向上测量的。

12.第一高度可以小于550nm,优选在100nm和500nm之间,并且更优选为220nm。第二高度可以在1和10微米之间,优选在2和5微米之间,并且更优选为3微米。锥形波导的长度可以是30微米到1mm,或者优选在50微米 /

‑

10微米之间。

13.沟槽的宽度和/或高度可以从锥形波导的第一端部到第二端部连续变化,以沿着锥形波导的长度给出宽度和/或高度的平滑变化。替换地,锥形波导的宽度和/或高度可以沿着锥形波导的长度逐步变化。台阶可以沿着锥形波导的长度以规则的间隔设置。

14.锥形波导可以由硅形成。

15.锥形波导在第二端部处的宽度可以大于锥形波导在第一端部处的宽度。以这种方式,高度和宽度两者都在锥形件的长度上变化以形成3d锥形件,使得具有不同高度和宽度的组件可以更有效地耦合,同时有减少的损耗。第一端部处的宽度可以是250nm到3000nm,优选500nm /

‑

100nm。第二端部处的宽度可以是1至10微米,优选为3微米。

16.光子芯片还可以包括光学耦合到锥形波导的第一端部的第一波导,第一波导具有第三高度。

17.锥形波导的顶表面可以与第一波导的顶表面共面。由于共面的顶表面,这使得芯片的后续处理(例如通过cmp)能够更简单。

18.替换地,顶表面可以不共面。例如,锥形波导的中心高度可以与第一和/或第二波导的中心高度共面。每个波导的中心高度是离相应波导的底表面和顶表面相等距离的高度。当光要在不同高度的波导之间被引导时,这可能是有益的。

19.锥形波导的模式高度可以与第一和/或第二波导的模式高度共面。锥形波导的芯的高度可以与第一和/或第二波导的芯的高度共面。在锥形波导中形成多个模式的情况下,这些模式中的一个或多个的高度可以与第一和/或第二波导的模式高度对齐。

20.在本公开中,高度差异小于50nm的表面被认为是共面的,因为高度差是可忽略的。这样的高度差可能是由诸如cmp停止层的制造过程导致的。

21.光子芯片还可以包括光学耦合到锥形波导的第二端部的第二波导,第二波导具有第四高度,第四高度大于第三高度。锥形波导的顶表面可以与第二波导的顶表面共面。

22.第二波导的宽度可以大于第一波导的宽度。

23.可选地,第二端部的高度可以是10微米。锥形波导的第二端部可以耦合到光纤和/或可以在光子芯片的边缘。这可以使第二端部能够耦合到未形成在光子芯片上的器件。

24.光子芯片还可以包括在低折射率层上方的顶部器件层、在低折射率层下面的中间器件层和在中间器件层下面的另一低折射率层。光子芯片可以形成在双绝缘体上硅(soi)衬底上,双soi衬底具有由硅形成的顶部器件层;低折射率层在顶部硅器件层下面;中间器件层在低折射率层下面,并且中间器件层由硅形成;该另一低折射率层在中间器件层下面;并且硅衬底在该另一低折射率层下面。

25.锥形波导可以在锥形波导的第一端部处与顶部器件层邻接,和/或可以在第二端部处与中间器件层邻接。术语邻接意味着锥形波导在边界处与层相遇,并且可以与层是连续的(例如,锥形波导可以与层形成单晶),或者可以在波导的内部结构和层不对齐的界面处与层相遇(例如,波导可以是非晶硅,并且层可以是单晶,或者层和波导可以由不同的材

料形成)。

26.锥形波导可以外延生长。替换地,锥形波导可以通过化学气相沉积(cvd)、原子层沉积、蒸发或溅射来沉积。锥形波导可以沉积为多晶或非晶材料,然后稍后热再生长以形成多晶或单晶结构。

27.锥形波导和/或第一波导和/或第二波导可以由多晶硅、非晶硅或单晶硅形成。锥形波导和/或第一波导和/或第二波导可以由锗或氮化硅或氮氧化物以任何组合形成。

28.锥形波导和/或第一波导和/或第二波导可以是条形、肋形或狭缝形波导。

29.锥形波导、第一波导和/或第二波导可以由材料序列形成,并且该序列可以是周期性的。例如,波导中的一个或多个可以由氧化硅和硅的交替片段形成,所述片段的尺寸可以被调整以选择波导的期望折射率。所述片段可以被定尺寸使得它们的长度小于要传递穿过波导的光的波长。

30.在第二方面,本发明提供了一种制造光子芯片的方法,该方法包括:提供包括硅衬底和在硅衬底上方的低折射率层的晶片,蚀刻低折射率层以形成锥形沟槽,该锥形沟槽在锥形沟槽的第一端部处具有第一高度,并且在锥形沟槽的第二端部处具有第二高度,第二高度大于第一高度,并且锥形沟槽具有底表面,该底表面在第二端部处比在第一端部处更靠近衬底,并且在锥形沟槽中形成锥形波导。

31.可以使用反应离子蚀刻来蚀刻沟槽。

32.形成锥形波导的步骤可以包括用多晶硅、非晶硅或单晶硅填充锥形沟槽。

33.形成锥形波导的步骤可以包括在锥形沟槽中外延生长材料。替换地,形成锥形波导的步骤可以包括通过化学气相沉积(cvd)、原子层沉积、蒸发或溅射来沉积材料。锥形波导可以沉积为多晶或非晶材料,然后稍后热再生长以形成多晶或单晶结构。该材料可以是硅。

34.形成锥形波导的步骤可以包括蚀刻沟槽中的材料以形成肋形、条形或狭缝波导。

35.形成锥形波导、第一波导和/或第二波导的步骤可以包括在波导的长度上沉积或生长材料序列。该序列可以是周期性的。例如,波导中的一个或多个可以由氧化硅和硅的交替片段形成,所述片段的尺寸可以被调整以选择波导的期望折射率。所述片段可以被定尺寸使得它们的长度小于要传递穿过波导的光的波长。在cheben p等人的2006年的“subwavelength waveguide grating for mode conversion and light coupling in integrated optics”《光学快报》v14.n11,p4695

‑

4702中给出了用于生产具有材料序列的波导的方法的示例。

36.晶片可以是绝缘体上硅晶片,包括硅衬底、低折射率层和硅器件层。

37.晶片可以是双绝缘体上硅晶片,包括顶部硅器件层、在顶部硅器件层下面的低折射率层、在低折射率层下面的中间器件层、在中间器件层下面的另一低折射率层以及在该另一低折射率层下面的衬底。

38.本发明包括所描述的方面和优选特征的组合,除非这样的组合是明显不允许的或明确避免的。特别地,第二方面的方法可以适应以形成第一方面的光子芯片的任何可选特征。

附图说明

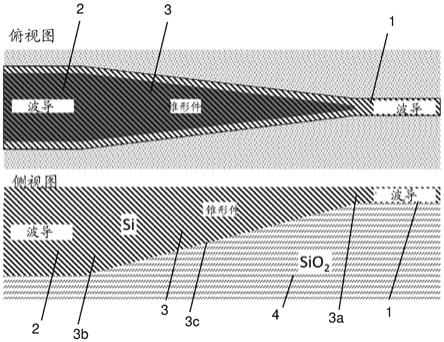

39.现在将参考附图讨论说明本发明的原理的实施例和实验,在附图中:图1示出了根据本发明的光子芯片的一部分的俯视图和侧视横截面视图。

40.图2示出了图1的光子芯片的一部分的侧视横截面视图(上中部)连同沿线1至5的光子芯片的横截面视图。

41.图3a至g示出了根据本发明的光子芯片的制造方法中的步骤的横截面视图。

42.图4示出了根据本发明的光子芯片的一部分的侧视横截面视图(上中部)连同沿线1至5的光子芯片的横截面视图。

43.图5a至h示出了根据本发明的光子芯片的制造方法中的步骤的横截面视图。

具体实施方式

44.现在将参考附图讨论本发明的方面和实施例。对于本领域技术人员来说,另外的方面和实施例将是显而易见的。此文本中提到的所有文献都通过引用并入本文中。

45.图1示出了光子芯片的一部分,其中第一波导1通过锥形波导3耦合到第二波导2。锥形波导3在锥形波导3的第一端部3a处与第一波导1相遇,并且锥形波导3在锥形波导3的第二端部3b处与第二波导2相遇。在锥形波导的第一端部3a处,锥形波导的高度大于锥形波导的第二端部3b处的高度。锥形波导3的宽度在第二端部3b处比在第一端部3a处更大。第一波导1比第二波导2具有更小的高度和更小的宽度。

46.如在侧视图中可以看出的,第一、第二和锥形波导的顶表面是共面的。在其他实施例中,顶表面可以不是共面的。例如,锥形波导的中心高度可以与第一和/或第二波导的中心高度共面。每个波导的中心高度是离相应波导的底表面和顶表面相等距离的高度。当光要在不同高度的波导之间被引导时,这可能是有益的。

47.锥形波导的模式高度可以与第一和/或第二波导的模式高度共面。锥形波导的芯的高度可以与第一和/或第二波导的芯的高度共面。在锥形波导中形成多个模式的情况下,这些模式中的一个或多个的高度可以与第一和/或第二波导的模式高度对齐。

48.在图2中更详细地示出了图1的光子芯片。剖视图示出了跨波导宽度的横截面。视图(1)示出第二波导的剖面,视图(2)、(3)和(4)示出沿锥形波导长度的各位置,并且视图(5)示出第一波导的剖面。

49.图1和2的光子芯片可以形成在soi晶片上,该soi晶片具有衬底5、在衬底上方的绝缘层4和在绝缘层4上方的硅器件层6。第一波导1形成在硅器件层6中。第二波导2延伸穿过硅器件层6并延伸到绝缘层4中的沟槽中。

50.锥形波导的底表面3c相对于在绝缘层4下面的衬底5的表面(图1中未示出)倾斜。以这种方式,锥形件被掩埋在绝缘层4中。

51.在所示的实施例中,绝缘层4由sio2形成,并且波导和衬底由si形成。替换地,波导可以由另一种材料诸如锗、氮化硅或氮氧化物形成。

52.在图2中示出的实施例中,波导是肋形波导。然而,在其他实施例中,其他类型的波导可以用于第一波导、第二波导、锥形波导或波导的任何组合。例如,可以形成条形或狭缝波导。

53.锥形波导可以与第一和/或第二波导连续。例如,锥形波导以及第一和第二波导中

的一个或两者可以由单晶结构形成。

54.现在将参考图3描述制造类似于图1和2中示出的光子芯片的光子芯片的方法。图3a示出了具有衬底5、绝缘层4和硅器件层6的soi衬底。

55.如图3b中示出的,然后在硅器件层6上沉积或生长sio2层7。

56.然后穿过sio2层7、穿过硅器件层6并向绝缘层4中蚀刻沟槽10。沟槽10在沟槽10的第一端部处的宽度小于在沟槽10的第二端部处的宽度。使用反应离子蚀刻(rie)蚀刻沟槽。由于称为rie滞后的现象,沟槽越宽,蚀刻得越深。

57.因此,通过sio2层7的图案化来控制沟槽的宽度,可以控制沟槽10的深度。这意味着沟槽的高度在沟槽的第二端部处(在那里沟槽最宽)大于沟槽在第一端部处(在那里沟槽最窄)的高度。

58.合适的蚀刻过程的示例是感应耦合等离子体反应离子蚀刻。这里,附加的电磁感应等离子体使得能够实现高等离子体密度,并允许控制氩和八氟环丁烷气体组合的电离程度。依赖于沟槽宽度的蚀刻深度可以通过利用rie滞后的物理效应来控制。这种效应主要依赖于氩和八氟环丁烷的气体流量比。这里氩用于控制电离程度和等离子体密度和各向异性蚀刻水平,其中八氟环丁烷控制聚合程度。在这个示例中,腔室压力低,icp功率为几千瓦特,并且rf功率在数百瓦特的范围内。这些参数允许以1.5nm/s至6nm/s之间的蚀刻速率蚀刻二氧化硅。在一个特定的示例中,对于3000nm宽的沟槽,大约2000nm被蚀刻到二氧化硅层中,而对于250nm宽的沟槽,到二氧化硅层中的蚀刻深度仅为200nm。

59.沟槽的宽度以及因此高度可以从第一端部到第二端部连续变化,以沿着沟槽的长度给出高度和宽度的逐渐变化,或者沟槽的宽度以及因此高度可以沿着沟槽的长度逐步变化。

60.如图3d中示出的,然后在沟槽10中沉积硅以填充沟槽。硅可以是非晶硅(a

‑

si)、多晶硅(p

‑

si)或单晶硅(c

‑

si)。可以使用lpcvd、pecvd、原子层沉积、溅射、蒸发和/或外延生长来沉积硅。可以沉积比填充沟槽所需要的更多的硅,因此沟槽可以被过度填充,如图3d中示出的。

61.然后,沉积的硅的顶表面被平坦化,例如使用化学机械抛光(cmp),如图3e中示出的。sio2层7用作平坦化的停止层,使得沟槽中的沉积的硅的顶表面与硅器件层6的顶表面基本上共面。

62.在图3f中,波导8然后被蚀刻到硅器件层6中以形成图1和2的光子芯片。波导8覆盖在沟槽10上面,并且可以比沟槽10更宽。

63.如果锥形波导是肋形波导,则蚀刻锥形件3,以在沉积在沟槽内的硅中形成锥形波导9。锥形波导9形成为使得其在位于沟槽的第一端部处的其第一端部处的宽度小于锥形波导9在位于沟槽的第二端部处的其第二端部处的宽度。由于沟槽在第二端部处比在第一端部处更深,锥形波导9的高度在第一端部处也比在第二端部处更小。因此,锥形波导9具有3d锥形形状,因为其高度和宽度两者沿着锥形波导的长度逐渐变细。

64.在该实施例中,波导8和9是肋形波导,但是在其他实施例中,波导8、9中的一个或两者可以是另一种类型的波导,诸如条形或狭缝波导。波导也可以由如以上所描述的材料序列形成。

65.锥形波导9可以经由形成在硅器件层中的波导8在其第一端部处耦合到第一波导。

波导8可以帮助紧密地保持锥形件中的光被横向限制,并馈入到较窄的第一波导中。

66.图4示出了具有第一、第二和锥形波导的另一光子芯片。剖视图示出跨波导宽度的横截面。视图(1)示出第二波导的剖面,视图(2)、(3)和(4)示出沿锥形波导长度的各位置,并且视图(5)示出第一波导的剖面。

67.图4的光子芯片类似于图2的光子芯片,除了该芯片还具有中间硅器件层16和另一绝缘层14。另一绝缘层14在衬底5上方,中间硅器件层16在该另一绝缘层14上方,绝缘层4在中间硅器件层16上方,并且锥形波导3在绝缘层4上方。

68.第一波导1形成在顶部硅器件层6中。第二波导从中间硅器件层16延伸,经过绝缘层4,并到顶部硅器件层6。因此,第二波导的底部部分由中间硅器件层形成。

69.第一波导1通过锥形波导3耦合到第二波导2。锥形波导3在锥形波导3的第一端部3a处与第一波导1相遇,并且锥形波导3在锥形波导3的第二端部3b处与第二波导2相遇。锥形波导在锥形波导的第一端部处与顶部硅器件层6相遇,并且在锥形波导的第二端部处与中间硅器件层16相遇。

70.在锥形波导的第一端部3a处,锥形波导的高度大于锥形波导的第二端部3b处的高度。锥形波导3的宽度在第二端部3b处比在第一端部3a处更大。第一波导1比第二波导2具有更小的高度和更小的宽度。如在侧视图中可以看出的,第一、第二和锥形波导的顶表面是共面的。

71.图4的光子芯片可以形成在双soi晶片上,该双soi晶片具有顶部硅器件层6、在顶部硅器件层下面的绝缘层4、在绝缘层下面的中间硅器件层16、在中间硅器件层下面的另一绝缘层14以及在该另一绝缘层下面的硅衬底5。

72.锥形波导的底表面3c相对于在绝缘层4下面的衬底5的表面倾斜。以这种方式,锥形件被掩埋在绝缘层4中。

73.以与图2中示出的光子芯片相同的方式,锥形波导的顶表面、中心高度、芯或模式的高度可以与第一和/或第二波导中的相应高度共面。

74.在所示的实施例中,绝缘层4由sio2形成,并且波导和衬底由si形成。替换地,波导可以由另一种材料诸如锗、氮化硅或氮氧化物形成。

75.在图4中示出的实施例中,波导8是肋形波导,并且波导3是条形波导。然而,在其他实施例中,其他类型的波导可以用于第一波导、第二波导、锥形波导或波导的任何组合。例如,可以形成条形或狭缝波导。

76.锥形波导可以与第一和/或第二波导连续。例如,锥形波导以及第一和第二波导中的一个或两者可以由单晶结构形成。

77.图4的锥形波导可以以与参考图3描述的方法类似的方式形成,并且如下文进一步描述的。

78.在顶部硅器件层6上沉积或生长sio2层。然后穿过sio2层、穿过顶部硅器件层6并且向绝缘层4中蚀刻出沟槽。

79.沟槽在沟槽10的第一端部处的宽度小于沟槽的第二端部处的宽度,并且使用rie进行蚀刻,使得沟槽的高度在沟槽最宽的沟槽的第二端部处大于沟槽在沟槽最窄的第一端部处的高度。

80.沟槽在第二端部处一直延伸穿过绝缘层4,使得沟槽到达中间硅层16。以这种方

式,沉积在沟槽中的硅在沟槽的第二端部处与中间硅器件层16相遇。因此,当波导形成在沉积在沟槽中的硅中时,对应于沟槽的第二端部的锥形波导3的第二端部3b与中间硅器件层16相遇。

81.沟槽的宽度以及因此高度可以从第一端部到第二端部连续变化,以沿着沟槽的长度给出高度和宽度的逐渐变化,或者沟槽的宽度以及因此高度可以沿着沟槽的长度逐步变化。

82.然后在沟槽中沉积硅以填充沟槽。硅可以是非晶硅(a

‑

si)、多晶硅(p

‑

si)或单晶硅(c

‑

si)。可以沉积比填充沟槽所需要的更多的硅,因此沟槽可以被过度填充。可以使用lpcvd、pecvd、原子层沉积、溅射、蒸发和/或外延生长来沉积硅。

83.然后,沉积的硅的顶表面被平坦化,例如使用cmp。sio2层用作平坦化的停止层,使得沟槽中的沉积的硅的顶表面与硅器件层6的顶表面基本上共面。

84.然后,波导被蚀刻到硅器件层6中,以形成图4的光子芯片。波导覆盖在沟槽上面,但是可以比沟槽10更宽。

85.如果锥形波导将是肋形波导,则蚀刻锥形件3以在沉积在沟槽内的硅中形成锥形肋形波导。

86.锥形波导可以用于耦合第一波导和第二波导,第一和第二波导具有不同的高度。现在将描述如何可以从双soi衬底开始形成多个高度的波导的示例。

87.首先,在双soi晶片的顶表面上沉积sio2层,其稍后用作cmp停止层。然后沉积掩模并使用光刻法进行图案化。掩模可以是抗蚀剂层或通过蚀刻穿过抗蚀剂层而被图案化的硬掩模材料。然后,通过将cmp停止层、顶部硅器件层6和绝缘层14蚀刻到中间硅器件层16的顶表面以暴露可以用于单晶再生长的种子层,在双soi晶片中形成沟槽。在其他实施例中,蚀刻可以继续进入中间硅器件层16中,使得沟槽延伸到中间硅器件层16中。可以使用干法蚀刻、湿法蚀刻或这两种技术的组合。然后,可以将掩模移除或留在原位用于在稍后的制造步骤中使用。

88.然后可以清洗种子层以准备用于生长的表面。然后可以从沟槽底部的种子层外延生长单晶硅。生长的硅可能过度填充沟槽,使得沟槽中生长的硅的顶表面高于顶部硅器件层6的顶表面。

89.在硅生长之后,可以在生长的硅的顶表面上执行平坦化过程。优选地,该过程降低了生长硅的高度,以匹配顶部硅器件层6的顶表面。合适的平坦化过程的示例是cmp。优选地,生长的硅的顶表面和顶部硅器件层的顶表面将精确匹配。然而,在平坦化之后,生长的硅的顶表面可以略高于顶部硅器件层6的顶表面。这是因为难以准确控制平坦化停止的高度。

90.在该实施例中,使用比硅抛光得更慢的停止层。这意味着可以在停止层的高度内停止抛光,确保在抛光之后,生长的硅的顶表面比顶部硅器件层的顶表面高不超过停止层的厚度。硬掩模可以在其用于早期蚀刻步骤之后留在原位,使得硬掩模可以在平坦化期间用作停止层。

91.在平坦化之后,顶部硅器件层6的顶表面和生长的硅18的顶表面之间的高度差可以近似为10至30nm,这足够小,使得这两个表面可以被认为是共面的。由于平坦化中可能出现的凹陷,其导致生长的硅的中心具有比生长的硅的边缘更低的顶表面,所以生长的硅的

高度可能在其宽度上变化。这引入了50nm、更优选30nm、更优选10nm的另外的公差。如果生长的硅的顶表面以这种方式“凹陷”,则它仍然可以被认为与顶部硅器件层6的顶表面共面。

92.在图5中示出的另一个实施例中,以上描述的方法可以通过从soi晶片(图5a)而不是双soi晶片开始来被修改。soi晶片的绝缘层14形成在以上方法中讨论的另一绝缘层14。如以上所讨论的,soi晶片的硅器件层形成中间硅器件层16。如图5b中示出的,在硅器件层16上生长或沉积sio2以形成以上讨论的绝缘层4。在沉积sio2之前,可以在硅器件层16上生长薄硅层。如图5c中示出的,锥形沟槽然后被蚀刻到绝缘层4中。然后,如图5d中示出的,在锥形沟槽中生长或沉积硅。然后,如图5e中示出的,例如使用cmp对硅进行平坦化以形成顶部硅器件层6。如图5h中示出的,波导8然后可以被蚀刻到顶部硅器件层6中。

93.平坦化步骤可以分成两个步骤,如图5f和5g中示出的。在图5f中,平坦化向下执行到绝缘层4的顶表面,然后将硅沉积到绝缘层的顶表面和填充的锥形沟槽上,以形成硅器件层6。

94.光子芯片然后可以被处理以产生多个高度的波导,波导具有共面的顶表面。

95.例如,肋形波导可以形成在生长的硅中和顶部硅器件层6中,使得第一波导形成在顶部硅器件层6中,并且第二波导形成在生长的硅中。

96.例如,可以通过在顶部硅器件层6中从顶部硅器件层的顶表面蚀刻沟槽到顶部硅器件层6内的某一高度来形成第一波导。沟槽之间的硅形成肋形波导的脊,并且沟槽下面的硅形成肋形波导的平板。第一波导的高度等于顶部硅器件层6的高度,因此第一波导22的顶表面与顶部硅器件层6的顶表面共面。

97.例如,可以通过在生长的硅中从生长的硅的顶表面蚀刻沟槽到中间硅器件层16的顶表面的高度来形成第二波导。沟槽之间的硅形成肋形波导的脊,并且沟槽下面的中间硅器件层16形成肋形波导的平板。第二波导的高度等于中间硅层16和平坦化的生长的硅的组合高度。这近似等于中间硅层16、绝缘层14和顶部硅器件层6的组合高度,使得第一波导的顶表面与顶部硅器件层6的顶表面共面。在对该实施例的修改中,沟槽可以更深,使得平板具有比中间硅器件层16更小的高度,或者沟槽可以更浅,使得平板具有比中间硅器件层16更大的高度。

98.以上示例的锥形波导可以用来耦合两个不同尺寸的波导。替换地,第二波导可以由设备或光纤电缆取代,和/或第一波导或第二波导可以由诸如激光器或调制器的设备取代。例如,锥形波导可以用作边缘耦合器,以将光子芯片上的第一波导耦合到光纤电缆。

99.在前面的描述中,或者在所附权利要求中,或者在附图中公开的特征,其以它们的特定形式或者根据用于执行所公开的功能的手段或用于获得所公开的结果的方法或过程来表达,在适当时可以单独地,或者以这样的特征的任何组合,被用于以其不同的形式来实现本发明。

100.虽然已经结合以上描述的示例性实施例描述了本发明,但是对于本领域技术人员来说,当给出本公开时,许多等同的修改和变化是显而易见的。因此,以上阐述的本发明的示例性实施例被认为是说明性的而非限制性的。在不脱离本发明的精神和范围的情况下,可以对所描述的实施例做出各种改变。

101.为了避免任何疑问,本文提供的任何理论解释都是为了提高读者的理解的目的而

被提供。发明人不希望被任何这些理论解释所束缚。

102.本文中使用的任何章节标题仅用于组织目的,并且不应被解释为限制所描述的主题。

103.贯穿整个说明书,包括所附权利要求,除非上下文另有要求,否则词语“包括”和“包含”以及诸如“包括了”、“包括着”和“包含着”之类的变体将被理解为暗示包括所陈述的整数或步骤或者整数或步骤的组,但不排除任何其他整数或步骤或者整数或步骤的组。

104.必须注意的是,如在说明书和所附权利要求中所使用的,单数形式“一”、“一个”和“该”包括复数指示物,除非上下文另有明确规定。范围在本文中可以表达为从“大约”一个特定值,和/或到“大约”另一个特定值。当表达这样的范围时,另一个实施例包括从该一个特定值和/或到该另一个特定值。类似地,当通过使用先行词“大约”将值表达为近似值时,应当理解,特定值形成另一个实施例。与数值相关的术语“大约”是可选的,并且例如意味着 /

‑ꢀ

10%。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。