1.本发明涉及占空比校准,尤其涉及一种倍频器(frequency multiplier)及延迟复用(delay-reused)占空比校准方法。

背景技术:

2.为了实现双倍频器(frequency doubler),需要将参考信号延迟该参考信号的25%个周期来产生延迟信号,从而,能够根据该参考信号和该延迟信号产生双倍频(doubled frequency)的输出信号。为了最大限度地减少输出杂散,需要输出信号具有精确的50%占空比,这意味着需要精确地生成上述25%个周期的延迟。一些相关技术采用不同的方法来产生此25%个周期的延迟。更具体地,在相关技术中使用模拟构建块,例如,环路滤波器、比较器、无源器件(例如,电阻器或比较器)、偏斜反相器(skew inverter)或运算放大器。

3.22nm、16nm、12nm、7nm等先进工艺提供了一些优势,例如,更少的栅极延迟、更高的操作速度和更少的电路面积。但是,也有一些缺点。先进的工艺是昂贵的。此外,使用先进工艺的模拟设计具有挑战性,更具体地说,会占用大面积并且难以优化性能。此外,用于产生上述25%个周期的延迟的上述模拟构建块在相关技术中可能会遇到一些问题。例如,环路滤波器和无源器件占据大面积,比较器偏移和器件失配会降低所产生延迟的精度,偏斜反相器会受到相位噪声的影响,以及,运算放大器在先进工艺中难以缩小。

4.因此,需要一种新颖的方法和相关架构,以能够通过全数字电路产生上述25%个周期的延迟,以防止遭受上述模拟设计问题,并充分利用先进工艺。

技术实现要素:

5.有鉴于此,本发明的目的在于提供一种倍频器及延迟复用占空比校准方法,以在不太可能会引入副作用的情况下解决相关技术的上述问题。

6.本发明的至少一个实施例提供了一种倍频器。倍频器可以包括第一校准电路、第二校准电路以及耦接该第一校准电路和该第二校准电路的控制器。第一校准电路可以包括被配置为提供第一延迟量的第一延迟单元。第二校准电路被配置为根据输入时钟信号产生输入校准信号。在倍频器的校准模式中,第一延迟单元的输出端耦接第一延迟单元的输入端,第一延迟单元被重复使用m次,以将输入校准信号或其衍生信号延迟第一延迟量的m倍来产生第一延迟信号,m为预定的正整数。此外,控制器根据第一延迟信号控制第一延迟量,以获得目标延迟量,使得目标延迟量的m倍等于输入时钟信号的一个周期。在找到目标延迟量后,第一延迟单元被重复使用m/2次,以将输入校准信号或其衍生信号延迟该目标延迟量的m/2倍来产生第二延迟信号;以及,控制器根据第二延迟信号控制第二校准电路,以使得输入校准信号具有目标占空比。

7.在一实施例中,该倍频器还包括:相位检测器,耦接该控制器,用于检测该第一延迟信号的延迟边沿与该输入校准信号的目标边沿之间的相位差;其中,该控制器控制该第

一延迟量,以使得该第一延迟信号的该延迟边沿与该输入校准信号的该目标边沿对齐。

8.在一实施例中,该第一延迟信号的该延迟边沿是通过延迟该输入校准信号或其衍生信号的第一边沿产生的,以及,该输入校准信号的该目标边沿是比该第一边沿晚一个周期的第二边沿。

9.在一实施例中,该第一校准电路还包括:计数器,耦接该第一延迟单元的输出端,其中,该计数器在该第一延迟单元被重复使用m次时产生该第一延迟信号的该延迟边沿。

10.在一实施例中,该第二校准电路包括:第二延迟单元,用于提供第二延迟量;其中,该控制器根据该第二延迟信号控制该第二延迟量,以使得该输入校准信号具有该目标占空比。

11.在一实施例中,该第二延迟单元包括:单位延迟组件,用于提供单位延迟,其中,该单位延迟组件的输出端耦接该单位延迟组件的输入端;其中,该单位延迟组件被重复使用n次,以使得该第二延迟量等于该单位延迟的n倍,n为正整数,其对应于该控制器控制的数字码。

12.在一实施例中,该第二校准电路还包括:反相器,用于根据该输入时钟信号产生反相时钟信号;以及,多工器,耦接该第二延迟单元,用于根据该输入时钟信号的当前占空比与该目标占空比的比较来选择该输入时钟信号和该反相时钟信号中的一者发送至该第二延迟单元。

13.在一实施例中,当该当前占空比大于该目标占空比时,该多工器选择该输入时钟信号将由该第二延迟单元延迟,以用于校准该输入校准信号;以及,当该当前占空比小于该目标占空比时,该多工器选择该反相时钟信号将由该第二延迟单元延迟,以用于校准该输入校准信号。

14.在一实施例中,该倍频器还包括第三校准电路,该第三校准电路包括:第三延迟单元,用于提供第三延迟量;其中,在获得该目标延迟量之后,该第一延迟单元被重复使用m/4次,以将该输入校准信号或其衍生信号延迟该目标延迟量的m/4倍来产生第三延迟信号;以及,该控制器根据该第三延迟信号控制该第三校准电路,以使得该第三延迟量等于该目标延迟量的m/4倍。

15.在一实施例中,该倍频器还包括:至少一个异或xor逻辑电路,耦接该第一校准电路,用于在该倍频器的正常模式下对该输入校准信号或其衍生信号与最终的延迟信号执行至少一个xor运算,以产生倍频的输出信号,其中,该最终的延迟信号是通过m/4次使用该第一延迟单元产生的,以将该输入校准信号延迟该目标延迟量的m/4倍;或者,该最终的延迟信号是通过m/8次使用该第一延迟单元产生的,以将该输入校准信号的衍生信号延迟该目标延迟量的m/8倍。

16.本发明的至少一个实施例提供了一种延迟复用占空比校准方法。延迟复用占空比校准方法可以包括:将第一延迟单元的输出端耦接到第一延迟单元的输入端(例如,在校准模式中),其中,第一延迟单元位于第一校准电路中,第一延迟单元被配置为提供第一延迟量,且第一延迟单元被重复使用m次,以将输入校准信号或其衍生信号延迟第一延迟量的m倍,从而产生第一延迟信号,其中,m为预定的正整数;控制器根据第一延迟信号控制第一延迟量,以获得第一延迟单元的目标延迟量,使得该目标延迟量的m倍等于输入时钟信号的一个周期,其中,输入校准信号是第二校准电路根据输入时钟信号产生的;在找到目标延迟量

之后,重复使用第一延迟单元m/2次,以将输入校准信号或其衍生信号延迟目标延迟量的m/2倍,从而产生第二延迟信号;以及,根据第二延迟信号控制第二校准电路,以使得输入校准信号具有目标占空比。

17.在一实施例中,该控制器根据该第一延迟信号控制该第一延迟量以获得该目标延迟量包括:检测该第一延迟信号的延迟边沿与该输入校准信号的目标边沿之间的相位差;以及,控制该第一延迟量,以使得该第一延迟信号的延迟边沿与该输入校准信号的目标边沿对齐。

18.在一实施例中,该第一延迟信号的该延迟边沿是通过延迟该输入校准信号或其衍生信号的第一边沿产生的,以及,该输入校准信号的该目标边沿是比该第一边沿晚一个周期的第二边沿。

19.在一实施例中,该第一延迟单元的输出端耦接计数器,以及,该计数器在该第一延迟单元被重复使用m次时产生该第一延迟信号的该延迟边沿。

20.在一实施例中,该第二校准电路包括第二延迟单元,该第二延迟单元用于提供第二延迟量,以及,根据该第二延迟信号控制该第二校准电路以使得该输入校准信号具有该目标占空比包括:根据该第二延迟信号控制该第二延迟量,以使得该输入校准信号具有该目标占空比。

21.在一实施例中,该第二延迟单元包括单位延迟组件,该单位延迟组件用于提供单位延迟,该单位延迟组件的输出端耦接该单位延迟组件的输入端,以及,控制该第二延迟量包括:重复使用该单位延迟组件n次,以使得该第二延迟量等于该单位延迟的n倍,n为正整数,其对应于该控制器控制的数字码。

22.在一实施例中,根据该第二延迟信号控制该第二校准电路来使得该输入校准信号具有该目标占空比还包括:根据该输入时钟信号的当前占空比与该目标占空比的比较来选择该输入时钟信号和反相时钟信号中的一者发送至该第二延迟单元,其中,该反相时钟信号是该输入时钟信号的反相信号。

23.在一实施例中,根据该输入时钟信号的当前占空比与该目标占空比的比较来选择该输入时钟信号和该反相时钟信号中的一者发送至该第二延迟单元包括:响应于指示该当前占空比大于该目标占空比的比较,选择该输入时钟信号将由该第二延迟单元延迟,以用于校准该输入校准信号。

24.在一实施例中,根据该输入时钟信号的当前占空比与该目标占空比的比较来选择该输入时钟信号和该反相时钟信号中的一者发送至该第二延迟单元包括:响应于指示该当前占空比小于该目标占空比的比较,选择该反相时钟信号将由该第二延迟单元延迟,以用于校准该输入校准信号。

25.在一实施例中,该方法还包括:在获得该目标延迟量之后,重复使用该第一延迟单元m/4次,以用于将该输入校准信号或其衍生信号延迟该目标延迟量的m/4倍来产生第三延迟信号;以及,根据该第三延迟信号控制第三校准电路,以使得该第三校准电路内的第三延迟单元提供的第三延迟量等于该目标延迟量的m/4倍。

26.本发明实施例能够使得第一延迟单元被重复使用m次,以获得对应于输入时钟信号的周期的1/m倍的精确时间,且第一延迟单元被进一步重复使用m/2次、m/4次、m/8次,以生成对应于输入时钟信号ckin的周期的50%、25%、12.5%的精确时间,且对应于输入时钟

信号ckin的周期的50%、25%、12.5%的精确时间能够得到保证。由于本发明不存在器件失配和偏移等问题,因此可以解决相关技术的上述问题。

27.本领域技术人员在阅读附图所示优选实施例的下述详细描述之后,可以毫无疑义地理解本发明的这些目的及其它目的。详细的描述将参考附图在下面的实施例中给出。

附图说明

28.通过阅读后续的详细描述以及参考附图所给的示例,可以更全面地理解本发明,其中:

29.图1是根据本发明实施例示出的一种双倍频器(frequency doubler)的简化示意图。

30.图2是根据本发明实施例说明图1所示的双倍频器的详细电路图的示意图。

31.图3是根据本发明实施例示出的一些信号在校准第一延迟量的阶段的期间的时序示意图。

32.图4是根据本发明另一实施例示出的一些信号在校准第一延迟量的阶段的期间的时序示意图。

33.图5是根据本发明实施例示出的一些信号在校准第二延迟量的阶段的期间的时序示意图。

34.图6是根据本发明另一实施例示出的一些信号在校准第二延迟量的阶段的期间的时序示意图。

35.图7是根据本发明实施例示出的一些信号在校准完成之后的时序示意图。

36.图8是根据本发明实施例示出的四倍频器(frequency quadrupler)的简化示意图。

37.图9是根据本发明实施例说明图8所示的四倍频器的详细电路图的示意图。

38.图10是根据本发明实施例示出的一些信号在校准第一延迟量的阶段的期间的时序示意图。

39.图11是根据本发明实施例示出的一些信号在校准第二延迟量的阶段的期间的时序示意图。

40.图12是根据本发明实施例示出的一些信号在校准第三延迟量的阶段的期间的时序示意图。

41.图13是根据本发明实施例示出的一些信号在完成校准之后的时序示意图。

42.图14是根据本发明实施例示出的延迟复用占空比校准方法的流程示意图。

43.在下面的详细描述中,为了说明的目的,阐述了许多具体细节,以便本领域技术人员能够更透彻地理解本发明实施例。然而,显而易见的是,可以在没有这些具体细节的情况下实施一个或多个实施例,不同的实施例可根据需求相结合,而并不应当仅限于附图所列举的实施例。

具体实施方式

44.以下描述为本发明实施的较佳实施例,其仅用来例举阐释本发明的技术特征,而并非用来限制本发明的范畴。在通篇说明书及权利要求书当中使用了某些词汇来指称特定

的元件,所属领域技术人员应当理解,制造商可能会使用不同的名称来称呼同样的元件。因此,本说明书及权利要求书并不以名称的差异作为区别元件的方式,而是以元件在功能上的差异作为区别的基准。本发明中使用的术语“元件”、“系统”和“装置”可以是与计算机相关的实体,其中,该计算机可以是硬件、软件、或硬件和软件的结合。在以下描述和权利要求书当中所提及的术语“包含”和“包括”为开放式用语,故应解释成“包含,但不限定于

…”

的意思。此外,术语“耦接”意指间接或直接的电气连接。因此,若文中描述一个装置耦接于另一装置,则代表该装置可直接电气连接于该另一装置,或者透过其它装置或连接手段间接地电气连接至该另一装置。

45.其中,除非另有指示,各附图的不同附图中对应的数字和符号通常涉及相应的部分。所绘制的附图清楚地说明了实施例的相关部分且并不一定是按比例绘制。

46.文中所用术语“基本”或“大致”是指在可接受的范围内,本领域技术人员能够解决所要解决的技术问题,基本达到所要达到的技术效果。举例而言,“大致等于”是指在不影响结果正确性时,技术人员能够接受的与“完全等于”有一定误差的方式。

47.为了产生两倍于原始时钟信号频率的双倍频率,原始时钟信号被与延迟信号执行异或(xor)运算,以产生具有双倍频率的双倍频时钟信号,其中,原始时钟信号被延迟了原始时钟信号的25%个周期(简称“25%延迟”),以产生25%延迟信号(即延迟了25%个周期的信号)。针对锁相环(phase locked loop,pll)的杂散相关要求,使得该双倍频时钟信号的占空比等于或基本等于50%且至少采用两次校准操作是优选的。应用于原始时钟信号的延迟(即前述25%延迟)需要被校准,以及,原始时钟信号的占空比也需要被校准。产生四倍于原始时钟信号频率的四倍频的机制是类似的,除了25%延迟外,还需要进一步产生和校准12.5%延迟(可以理解地,即对应原始时钟信号的12.5%个周期的延迟)。因此,本发明旨在提供占空比校准的实施例,更特别地,校准上述25%延迟和/或12.5%延迟。

48.图1是根据本发明实施例示出的一种倍频器(frequency multiplier)的简化示意图,例如,双倍频器(frequency doubler)10,其中,双倍频器10可以应用在pll中。如图1所示,双倍频器10可以包括:至少一个xor(异或)逻辑电路(例如,xor逻辑电路100(为了简洁起见,其被标记为“xor”)),第一校准电路(例如,延迟校准电路120),第二校准电路(例如,输入占空比校准电路140),以及,控制器(例如,数字控制电路160)。延迟校准电路120可以包括第一延迟单元(first delay cell)122,第一延迟单元122被配置为提供第一延迟量(first delay)τ1,其中,“τ1”被标记在第一延迟单元122上以便于更好的理解。延迟校准电路120还可以包括多工器(multiplexer)124,其被使能信号(enable signal)en控制,其中,使能信号en可以是从锁相环(pll)的控制电路或从数字控制电路160传输过来的,但本发明并不限于此。输入占空比校准电路140可被配置为根据输入时钟信号(input clock signal)ckin产生输入校准信号(input calibration signal)ck1x,例如,输入占空比校准电路140调整输入时钟信号ckin的占空比,以藉助第二延迟量τ2(其被标记在输入占空比校准电路140上,以便更好地理解)来产生输入校准信号ck1x。

49.例如,当双倍频器10工作在校准模式(calibration mode)下时,使能信号en可以被设置为“1”,以及,第一延迟单元122的输出端通过多工器124耦接到该第一延迟单元的输入端(例如,第一延迟单元122与多工器形成环形振荡器(ring-oscillator,ro)型延迟单元),因此,第一延迟单元122被重复使用多次(例如,m次,其中,m为预定的正整数,例如四),

以将输入校准信号ck1x或其衍生信号(例如,输入校准信号ck1x的衍生信号)延迟第一延迟量τ1的倍数(例如,延迟m

×

τ1)来产生延迟信号ckout或其衍生信号(例如,延迟信号ckout的衍生信号)。在另一示例中,当双倍频器10工作在正常模式(normal mode)下时,使能信号en可以被设置为“0”,以及,第一延迟单元122的输出端上的(一个或多个)信号将不会反馈到第一延迟单元122的输入端,因此,第一延迟单元122仅被使用一次,以将输入校准信号ck1x(或其衍生信号)延迟第一延迟量τ1来产生延迟信号ckout,以及,异或(xor)逻辑电路100可被配置为对输入校准信号ck1x(或其衍生信号)与最终的延迟信号(例如,延迟信号ckout)执行至少一个xor运算,以产生具有倍频(multiplied frequency)的输出信号,例如,双倍频的时钟信号ck2x。

50.在本实施例中,当第一延迟单元122接收到上升沿(rising edge)时,第一延迟单元122将输出具有第一延迟量τ1的下降沿(falling edge);以及,当第一延迟单元122接收到下降沿时,第一延迟单元122将输出具有第一延迟量τ1的上升沿。

51.在本实施例中,数字控制电路160可以耦接第一校准电路(如延迟校准电路120)和第二校准电路(如输入占空比校准电路140),用于在校准模式中调整第一延迟量τ1和第二延迟量τ2(为简洁起见,被标记为“调整τ1”和“调整τ2”)。举例来说,第一延迟单元122可被重复使用m次(例如,四次),用于将输入校准信号ck1x(或其衍生信号)延迟第一延迟量τ1的m倍(例如,延迟m

×

τ1)来产生第一延迟信号。数字控制电路160可根据第一延迟信号控制第一延迟量τ1(例如,调整τ1),以获得(find)目标延迟量(target delay),使得该目标延迟量的m倍等于输入时钟信号ckin的一个周期(cycle period)。也就是说,该目标延迟量等于输入时钟信号ckin的1/m个周期,这可以是前述25%延迟的示例。在找到目标延迟量后,第一延迟单元122可被重复使用m/2次(例如,两次),用于将输入校准信号ck1x(或其衍生信号)延迟该目标延迟量的m/2倍(其可等于输入时钟信号ckin的50%个周期)来产生第二延迟信号。数字控制电路160可根据第二延迟信号控制输入占空比校准电路140,使得输入校准信号ck1x具有目标占空比,例如50%,例如,第二延迟信号携带与精确的50%占空比相对应的时间间隔(time interval)相关的信息,该信息可以作为校准输入校准信号ck1x的占空比的参考。

52.在该实施例中,双倍频器10还可以包括耦接数字控制电路160的相位检测器(phase detector,pd)180。具体地,当校准第一延迟量τl时,相位检测器180可以检测第一延迟信号的延迟边沿(delayed edge)与输入校准信号ck1x的目标边沿(target edge)之间的相位差,以及,数字控制电路160可以根据该相位差控制第一延迟量τ1,以使得第一延迟信号的延迟边沿与输入校准信号ck1x的目标边沿对齐(align)。例如,第一延迟信号的延迟边沿可以通过延迟输入校准信号ck1x(或其衍生信号)的第一边沿来产生,以及,输入校准信号ck1x的目标边沿可以是晚于第一边沿的一个周期的第二边沿。也就是说,当第一延迟信号的延迟边沿与输入校准信号ck1x的目标边沿对齐时,m

×

τ1等于输入时钟信号ckin(或输入校准信号ck1x)的一个周期,从而获得等于输入时钟信号ckin的1/m个周期的目标延迟量。在找到该目标延迟量后,相位检测器180基于第二延迟信号和输入校准信号ck1x产生另一相位差,以及,数字控制电路160根据此相位差校准输入校准信号ck1x的占空比。为便于理解与说明,在本发明实施例中,延迟边沿、目标边沿、第一边沿和第二边沿以上升沿为例进行示例说明,但本发明并不限于此,例如,也可以是下降沿,只要能够获得输入时钟信号

ckin的1/m个周期的目标延迟量均可。

53.图2是根据本发明实施例示出图1所示的双倍频器10的详细电路图的示意图,在该示例中,延迟校准电路120还可以包括计数器(counter)126,其耦接到第一延迟单元122的输出端。在校准第一延迟量τ1的阶段的过程中,计数器126可以在第一延迟单元122已被重复使用m次时产生第一延迟信号的边沿(例如,第一延迟信号的上述延迟边沿)。例如,计数器126每隔第一延迟量τ1的间隔从第一延迟单元122接收延迟信号ckout的转变边沿(transition edge),以及,当计数器126从第一延迟单元122接收到第m个延迟信号ckout的转变边沿时(这意味着经过m

×

τ1的持续时间),计数器126可以输出第一延迟信号(例如,计数器126的输出信号可被视为延迟信号ckout的衍生信号)的延迟边沿至相位检测器180。在校准第二延迟量τ2的阶段中,当第一延迟单元122已被重复使用m/2次时(例如,当计数器126从第一延迟单元122接收到第(m/2)个转变边沿时,这意味着经过了(m/2)

×

τ1的持续时间),计数器126可以产生第二延迟信号的边沿。

54.如图2所示,输入占空比校准电路140可以包括and(与门)逻辑电路141(为了简洁,其被标记为“and”)和第二延迟单元,其中,第二延迟单元可以被配置为提供第二延迟量τ2,以及,数字控制电路160可根据第二延迟信号控制第二延迟量τ2,以使得输入校准信号ck1x具有目标占空比。在该实施例中,第二延迟单元可以包括单位延迟组件142(为了更好的理解,其被标记为“τ2”)、多工器143和计数器144,其中,单位延迟组件142被配置为提供单位延迟,以及,多工器143由控制信号control1控制。此外,输入占空比校准电路140还可以包括反相器(inverter)145以及耦接至第二延迟单元的多工器146,其中,反相器145用于根据输入时钟信号ckin产生反相时钟信号(inverted clock signal),多工器146被配置为根据输入时钟信号ckin的当前占空比与目标占空比的比较来选择输入时钟信号ckin和反相时钟信号中的一者发送至第二延迟单元。举例来说,多工器146可根据极性信号(polarity signal)pl选择输入时钟信号ckin与反相时钟信号中的一者作为选定时钟信号(selected clock signal)ckin_pl,选定时钟信号ckin_pl用于被传送至第二延迟单元,其中,极性信号pl可代表前述比较,其可以指示输入时钟信号ckin的当前占空比是否大于目标占空比。特别地,当该当前占空比大于目标占空比时,极性信号pl为“1”,以及,多工器146可选择输入时钟信号ckin由第二延迟单元进行延迟,以用于校准输入校准信号ck1x;以及,当该当前占空比小于目标占空比时,极性信号pl为“0”,以及,多工器146可选择反相时钟信号由第二延迟单元进行延迟,以用于校准输入校准信号ck1x。此外,and逻辑电路142可以对该选定时钟信号和从第二延迟单元输出的延迟信号执行与逻辑运算,其中,第二延迟单元将该选定时钟信号延迟第二延迟量τ2,以产生该延迟信号。

55.具体地,当检测到该选定时钟信号ckin_pl的转变边沿时(例如,由数字控制电路160或pll的控制电路检测到),控制信号controll可以被触发并从低拉到高(例如,从逻辑值“0”变为逻辑值“1”),以及,单位延迟组件142的输出端通过多工器143耦接到单位延迟组件142的输入端,从而形成ro型延迟单元,以产生第二延迟量τ2。例如,单位延迟组件142可被重复使用n1次,以使得第二延迟量τ2等于单位延迟组件142提供的单位延迟的n1倍,其中,计数器144被配置为输出被第二延迟单元延迟的信号。计数器144的操作可以根据计数器126的操作类推,此处不再赘述。在本实施例中,n1可以是正整数,其对应于数字控制电路160控制的数字码(digital code),以及,数字控制电路160可以通过控制该数字码来控制

第二延迟量τ2,从而控制单位延迟组件142被重复使用的次数。需要说明的是,单位延迟组件142上标注“τ2”只是为了说明,而第二延迟量τ2实际上是通过重复使用单位延迟组件142来产生的(例如,τ2等于单位延迟组件142提供的单位延迟的n1倍)。

56.在本实施例中,当单位延迟组件142接收到上升沿时,单位延迟组件142将输出具有该单位延迟的下降沿;以及,当单位延迟组件142接收到下降沿时,单位延迟组件142将输出具有该单位延迟的上升沿。

57.图3为根据本发明实施例说明一些信号在校准第一延迟量τ1的阶段的期间的时序示意图(例如,图2所示的输入校准信号ck1x、使能信号en、延迟m次后最终输出的延迟信号ckout和计数器126的输出信号),其中,计数器126的输出信号由图3中的计数器输出信号counter表示。如图3所示,在输入校准信号ck1x的奇数周期(odd periods)中,重复使用第一延迟量τ1的操作被执行,标记为“奇数周期:重复使用延迟(odd period:reuse delay)”;而在输入校准信号ck1x的偶数周期(even periods)中,计算第一延迟量τ1的调整的操作被执行,标记为“偶数周期:计算(even period:calculate)”。在本实施例中,在输入校准信号ck1x的奇数周期的开始处(例如,当接收到输入校准信号ck1x的第一个上升沿时),使能信号en被触发并被拉高,以及,重复使用第一延迟单元122的操作开始。当第一延迟单元122已被重复使用四次并且因此产生如图3中被圈出的部分所示的计数器输出信号counter的上升沿时,输入校准信号ck1x的第二个上升沿和计数器输出信号counter的该上升沿之间的相位差能够被检测到。假设第一延迟量的原始值为τ1',以及,检测到的相位差表明第一延迟量τ1'的四倍大于输入校准信号ck1x的一个周期(或输入时钟信号ckin的一个周期)。相应地,数字控制电路160可以调整(例如,减少)第一延迟量从τ1’到τ1,以使得计数器输出信号counter的该上升沿与输入校准信号ck1x的上升沿对齐,如图3中被圈出的部分所示。

58.在另一实施例中,如图4所示,假设检测到的相位差表示第一延迟量τ1'的四倍小于输入校准信号ck1x的一个周期(或输入时钟信号ckin的一个周期)。相应地,数字控制电路160可调整(例如,增加)第一延迟量从τ1'至τ1,以使得计数器输出信号counter的该上升沿与输入校准信号ck1x的上升沿对齐,如图4中被圈出的部分所示。

59.图5是根据本发明实施例说明一些信号(例如,输入时钟信号ckin、极性信号pl、选择信号ckin_pl、输入校准信号ck1x、使能信号en、延迟信号ckout和图2所示的计数器126的输出信号)在校准第二延迟量τ2的阶段的期间的时序示意图,其中,计数器126的输出信号由图5中的计数器输出信号counter示出。如图5所示,计数器126在第一延迟单元126已被重复使用两次时产生计数器输出信号counter的上升沿,以及,该上升沿能够被用作校准输入校准信号ck1x的占空比的参考边沿。假设输入时钟信号ckin的占空比大于目标占空比(例如,输入时钟信号ckin的占空比为53%,其大于50%),极性信号pl被设置为“1”,以及,输入时钟信号ckin被选择作为选定时钟信号ckin_pl。输入占空比校准电路140减少输入校准信号ck1x为“1”的时间,以降低输入校准信号ck1x的占空比。更具体地,数字控制电路160可调整第二延迟量τ2,以使得输入校准信号ck1x的下降沿与该参考边沿对齐,如图5中圈出的部分所示。

60.在另一实施例中,假设输入时钟信号ckin的占空比小于目标占空比(例如,输入时钟信号ckin的占空比为47%,其小于50%),极性信号pl被设置为“0”,以及,根据输入时钟信号ckin产生的反相时钟信号被选择作为选定时钟信号ckin_pl,因此,ckin_pl的占空比

可以大于目标占空比(例如,ckin_pl的占空比为53%,其大于50%),如图6所示。输入占空比校准电路140可以减少输入校准信号ck1x为“1”的时间,以减小输入校准信号ck1x的占空比。更具体地,数字控制电路160可调整第二延迟量τ2,以使得输入校准信号ck1x的下降沿与参考边沿对齐,如图6中圈出的部分所示。

61.在第一延迟量τ1和第二延迟量τ2的校准完成后,输入校准信号ck1x的占空比能够等于或基本等于(substantially equal)50%,以及,第一延迟量τ1能够等于或基本等于输入时钟信号ckin(或输入校准信号ck1x)的一个周期的25%,如图7所示。基于此校准结果,xor逻辑电路100可以通过对输入校准信号ck1x和最终的延迟信号ckout执行xor运算来产生双倍频的时钟信号ck2x,其中,双倍频的时钟信号的占空比能够等于或基本上等于50%。

62.图8是根据本发明实施例示出的倍频器(例如,四倍频器80)的简化示意图,其中,四倍频器80可以通过修改图1所示的双倍频器10来获得。四倍频器80可应用在锁相环中。除了xor逻辑电路100、延迟校准电路120、输入占空比校准电路140和数字控制电路160之外,四倍频器80还可以包括xor逻辑电路200、第三校准电路(例如,延迟校准电路220)和相位检测器181/182。在本实施例中,延迟校准电路220可被配置为将输入校准信号ck1x延迟第三延迟量τ3以产生延迟信号ck1x_25,其中,“τ3”被标记在延迟校准电路220上以便更好理解。异或(xor)逻辑电路200对输入校准信号ck1x和延迟信号ck1x_25执行异或(xor)运算,以产生双倍频时钟信号ck2x,其中,双倍频时钟信号ck2x可以是输入校准信号ck1x的衍生信号(derivative)的一种例子。

63.在本实施例中,校准第一延迟量τ1的操作可以通过重复使用第一延迟单元122m次(例如,八次)来执行,用于将双倍频时钟信号ck2x延迟第一延迟量τ1的m倍(例如,8

×

τ1)来产生延迟信号ckout或其衍生信号。相位检测器181检测延迟信号ckout衍生信号的延迟边沿与输入校准信号ck1x的目标边沿之间的相位差,以及,数字控制电路160根据该相位差控制第一延迟量τ1(例如,调整τ1)。在第一延迟量τ1的校准完成后(例如,找到第一延迟单元122的目标延迟量),第一延迟单元122可被重复使用m/2次(例如,四次),用于将双倍频时钟信号ck2x延迟第一延迟量τ1的m/2倍(例如,4

×

τ1),以提供用于校准输入校准信号ck1x的占空比的参考边沿(更具体地,用于校准/调整第二延迟量τ2),以及,第一延迟单元122可被重复使用m/4次(例如,两次),用于将双倍频时钟信号ck2x延迟第一延迟量τ1的m/4倍(例如,2

×

τ1),以产生第三延迟信号并借助相位检测器182提供第三延迟信号的参考边沿,其用于校准/调整第三延迟量τ3(例如,校准延迟信号ck1x_25)。例如,数字控制电路160根据第三延迟信号控制延迟校准电路220,以使得第三延迟量τ3等于目标延迟量的m/4倍(例如,2

×

τ1)。

64.在第一延迟量τ1、第二延迟量τ2和第三延迟量τ3的校准完成后,第一延迟单元122被重复使用m/8次(例如,一次),以产生最终的延迟信号,例如,在四倍频器80的正常模式下的延迟信号ckout或其衍生信号,以及,异或(xor)逻辑电路100对双倍频时钟信号ck2x与最终的延迟信号(例如,延迟信号ckout或其衍生信号)执行异或(xor)运算,以生成四倍频时钟信号ck4x。由于第一延迟量τ1和第二延迟量τ2的校准与上述实施例类似,因此,第三延迟量τ3的校准可以在第一延迟量τ1和第二延迟量τ2的校准基础上类推,为简洁起见,此处省略相关细节。

65.图9是根据本发明实施例示出图8所示的四倍频器80的详细电路图的示意图,其

中,延迟校准电路120和输入占空比校准电路140的实现方式与图2的实施例相同,因此,此处不再赘述相关细节。在本实施例中,多工器143由控制信号control1控制。此外,延迟校准电路220可以包括被配置为提供第三延迟量τ3的第三延迟单元。类似于输入占空比校准电路140内的第二延迟单元,第三延迟单元可以包括单位延迟组件222、多工器223和计数器226,其中,单位延迟组件222被配置为提供单位延迟,以及,多工器223由控制信号control2控制。在一实施例中,单位延迟组件222提供的单位延迟可以与单位延迟组件142提供的单位延迟相同。在其它实施例中,单位延迟组件222提供的单位延迟可以不同于单位延迟组件142提供的单位延迟。

66.详细而言,当检测到输入校准信号ck1x的转变边沿时(例如,由数字控制电路160或pll的控制电路检测得到),控制信号control2被触发并从低拉至高(例如,从逻辑值“0”到逻辑值“1”),以及,单位延迟组件222的输出端可以通过多工器223耦接到单位延迟组件222的输入端,从而形成ro型延迟单元,以用于产生第三延迟量τ3。例如,单位延迟组件222可以被重复使用n2次,以使得第三延迟量τ3等于单位延迟组件222提供的单位延迟的n2倍,其中,计数器224用于输出经过第三延迟单元延迟的延迟信号ck1x_25。计数器226的操作可以根据计数器126和144的操作进行类推,为简洁起见,此处不再赘述。在本实施例中,n2可以是数字控制电路160控制的数字码对应的正整数,以及,数字控制电路160可以通过控制该数字码来控制第三延迟量τ3,从而控制单位延迟组件222被重复使用的次数。

67.在本实施例中,当单位延迟组件222接收到上升沿时,单位延迟组件222将输出具有其单位延迟的下降沿;以及,当单位延迟组件222接收到下降沿时,单位延迟组件222将输出具有其单位延迟的上升沿。

68.图10是根据本发明实施例说明一些信号(例如,输入校准信号ck1x、双倍频时钟信号ck2x、使能信号en、延迟信号ckout和图9中所示的计数器126的输出信号)在校准第一延迟量τ1的阶段的期间的时序示意图,其中,计数器126的输出信号由图10中的计数器输出信号counter说明。在本实施例中,在输入校准信号ck1x的奇数周期的开始处(更具体地,当接收到输入校准信号ck1x的第一个上升沿时),使能信号en由双倍频时钟信号ck2x的上升沿触发并拉高,以及,重复使用第一延迟单元122的操作开始。当第一延迟单元122已被重复使用八次并且因此产生如图10中被圈出的部分所示的计数器输出信号counter的上升沿时,能够检测到输入校准信号ck1x的第二个上升沿和计数器输出信号counter的上升沿之间的相位差。图10示出了减小第一延迟量以使得8

×

τ1等于输入校准信号ck1x的一个周期(被标记为“参考周期(reference period)”),而增大第一延迟量τ1以进行校准的情况可以类推,故此处省略。

69.图11是根据本发明实施例说明一些信号(例如,输入时钟信号ckin、极性信号pl、选定时钟信号ckin_pl、输入校准信号ck1x、使能信号en、延迟信号ckout和图10所示的计数器输出信号counter)在校准第二延迟量τ2的阶段的期间的时序示意图。如图11所示,当第一延迟单元126已被重复使用四次时,计数器126产生计数器输出信号counter的上升沿,且该上升沿用作校准输入校准信号ck1x的占空比,如图11中被圈出的部分所示。四倍频器80中的反相器145和多工器146的操作与双倍频器10中的相同,此处不再赘述。

70.图12是根据本发明实施例说明一些信号(例如,输入时钟信号ckin、极性信号pl、选定时钟信号ckin_pl、输入校准信号ck1x、使能信号en、延迟信号ckout和图10所示的计数

器输出信号counter)在校准第三延迟量τ3的阶段的期间的时序示意图。如图12所示,当第一延迟单元126已被重复使用两次时,计数器126可产生计数器输出信号counter的上升沿,且该上升沿可用作校准输入校准信号ck2x的占空比的参考边沿,如图12中被圈出的部分所示。具体地,第三延迟量τ3可以被校准为等于第一延迟量τ1的两倍,第三延迟量τ3等于输入校准信号ck1x的一个周期的25%。

71.在第一延迟量τ1、第二延迟量τ2和第三延迟量τ3的校准完成后,输入校准信号ck1x的占空比能够等于或基本等于50%,第三延迟量τ3(其对应于双倍频时钟信号ck2x的占空比)能等于或基本等于输入时钟信号ckin(或输入校准信号ck1x)的一个周期的25%,以及,第一延迟量τ1(其对应于四倍频时钟信号ck4x的占空比)能等于或基本等于输入时钟信号ckin(或输入校准信号ck1x)的一个周期的12.5%,如图13所示。基于此校准结果,异或(xor)逻辑电路100产生的四倍频时钟信号ck4x的占空比能等于或基本等于50%。

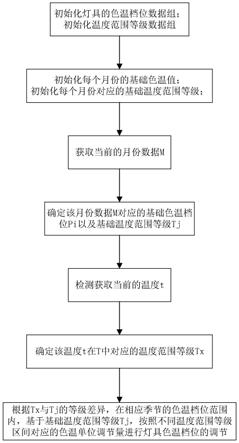

72.图14为本发明实施例提供的延迟复用占空比校准方法(delay-reused duty cycle calibration method)的工作流程示意图,其中,该延迟复用占空比校准方法可以应用于倍频器,如双倍频器10、四倍频器80等。需要注意的是,图14所示的工作流程仅用于说明目的,并不意味着对本发明的限制。在图14所示的工作流程中可以增加、删除或修改一个或多个步骤。另外,如果可以得到相同的结果,则这些步骤不必按图14所示的确切顺序执行。

73.在步骤1410中,倍频器可以通过第一校准电路(例如,延迟校准电路120)将第一延迟单元(例如,第一延迟单元122)的输出端耦接到第一延迟单元的输入端,其中,第一校准电路包括第一延迟单元,第一延迟单元被配置为提供第一延迟量(例如,τ1),以及,第一延迟单元被重复使用m次,用于将输入校准信号(例如,输入校准信号ck1x)或其衍生信号(例如,双倍频时钟信号ck2x)延迟第一延迟量的m倍来产生第一延迟信号。

74.在步骤1420中,倍频器可以由控制器(例如,数字控制电路160)根据第一延迟信号控制第一延迟量,以找到第一延迟单元的目标延迟量,使得目标延迟量的m倍等于输入时钟信号(例如,输入时钟信号ckin)的一个周期,其中,输入校准信号是由第二校准电路(例如,输入占空比校准电路140)根据输入时钟信号产生的。

75.在步骤1430中,在找到目标延迟量之后,倍频器可以重复使用第一延迟单元m/2次,用于将输入校准信号或其衍生信号延迟目标延迟量的m/2倍来产生第二延迟信号。

76.在步骤1440中,倍频器可根据第二延迟信号控制第二校准电路,以使得输入校准信号具有目标占空比(例如,50%)。

77.需要说明的是,校准第二延迟量τ2和校准第三延迟量τ3的顺序并非对本发明的限制。一旦校准第一延迟量τ1的操作完成(例如,当建立/找到第一延迟单元122的目标延迟量时),校准第二延迟量τ2和校准第三延迟量τ3的顺序可以改变。

78.需要说明的是,m的值并不意味着对本发明的限制。更具体地说,如果m的值增加(称为更高的重复使用/复用次数),第一延迟量τ1可以被减少,因为τ1被预计是输入时钟信号ckin的周期的1/m倍,以及,第一延迟单元的电路面积可以被减少。然而,较高的复用次数会导致调整τ1/τ2/τ3的分辨率较低,以及,pll的杂散相关性能会降低。因此,在复用次数(其对应于电路面积成本)和分辨率(其对应于杂散相关性能)之间存在折衷。在一定的杂散相关要求下(例如《80dbc),可以通过仿真获得双倍频器10的优化m值(例如,32),以及,在某

些杂散相关要求下(例如,《80dbc),可以通过仿真获得四倍频器80的优化m值(例如,16)。

79.计数器126、144和226优选地通过二进制计数器(binary counter)来实现,以及,优选地,m的值为2的幂方(例如,4、8、16、32、64、128等),但是本发明不限于此。可以将四的任意倍数应用于双倍频器10中的m值,以及,可以将八的任意倍数应用于四倍频器80中的m值。应注意,某些m值可能导致第一延迟量τ1被期望重复校准为输入时钟信号ckin的周期的十进制百分比(例如,针对双倍频器10,当m=12时,第一延迟量τ1被校准为大约是周期的8.3333%;以及,针对四倍频器80,当m=24时,第一延迟量τ1被校准为大约是周期的4.1667%。但是,只要调整τ1/τ2/τ3的分辨率足够小,重复的十进制百分比(decimal percentage)引入的误差将不会成为校准整体量化误差的主导项。

80.优选地,通过固定的延迟组件(例如,具有固定传播延迟的反相器)来实现单位延迟组件142和单位延迟组件222中的任一者(例如每一个),其中,调整第二延迟量τ2的操作可以通过调整单位延迟组件142的复用次数(例如n1)来执行,而调整第二延迟量τ2的操作可以通过调整单位延迟组件142的复用次数(例如,n1)来执行,但本发明并不限于此。在一些实施例中,第二延迟单元和第三延迟单元中的任一者可以通过模拟电路来实现,以及,调整第二延迟量τ2和/或第三延迟量τ3的操作可以通过模拟方式(例如,调整第二延迟单元和/或第三延迟单元中的传播载荷或驱动强度)来执行。同理,调整第一延迟单元122所提供的第一延迟量τ1的操作也不限于任何特定的机制,其中,图2和图9的实施例中所说明的调整第二延迟量τ2和第三延迟量τ3的操作可应用于调整第一延迟量τ1的操作,但本发明并不限于此。在一些实施例中,调整第一延迟量τ1的操作可以以上述类似的方式进行。由于第一延迟单元122被重复使用m次,以用于获得对应于输入时钟信号ckin的1/m个周期的精确时间间隔,且被进一步重复使用m/2次、m/4次和m/8次,以产生对应于输入时钟信号ckin的周期的50%、25%和12.5%的精确时间间隔,以模拟方式调整第一延迟量τ1不会受到器件失配或偏移等模拟电路相关问题的影响,并且可以保证对应于输入时钟信号ckin的周期的50%、25%和12.5%的时间间隔的精度。

81.虽然本发明已经通过示例的方式以及依据优选实施例进行了描述,但是,应当理解的是,本发明并不限于公开的实施例。相反,它旨在覆盖各种变型和类似的结构(如对于本领域技术人员将是显而易见的),例如,不同实施例中的不同特征的组合或替换。因此,所附权利要求的范围应被赋予最宽的解释,以涵盖所有的这些变型和类似的结构。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。