技术特征:

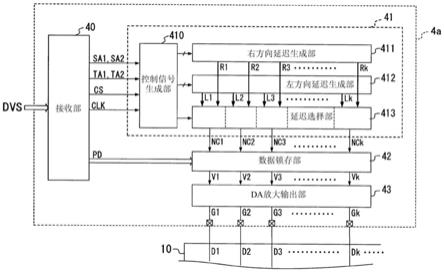

1.一种显示驱动器,具有输出分别与由影像信号表示的各像素的亮度水平对应的第一像素驱动电压~第k像素驱动电压的第一输出通道~第k输出通道,其中k为2以上的整数,其特征在于具有:输出时机控制部,生成表示所述第一输出通道~第k输出通道各者中的输出时机的第一输出时机信号~第k输出时机信号;及输出部,在由所述第一输出时机信号~第k输出时机信号各者表示的所述输出时机分别输出所述第一像素驱动电压~第k像素驱动电压;所述输出时机控制部具有:控制信号生成部,接收所述第一输出通道及第k输出通道各者中的输出时机的指定,在所指定的所述第一输出通道的输出时机生成第一延迟脉冲信号,并且在所指定的所述第k输出通道的输出时机生成第二延迟脉冲信号;第一延迟生成部,接收所述第一延迟脉冲信号,生成经过从所述第一输出通道向所述第k输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现所述第一延迟脉冲信号的第一第一方向延迟移位信号~第k第一方向延迟移位信号;第二延迟生成部,接收所述第二延迟脉冲信号,生成经过从所述第k输出通道向所述第一输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现所述第二延迟脉冲信号的第一第二方向延迟移位信号~第k第二方向延迟移位信号;及延迟选择部,针对所述第一输出通道~第k输出通道的每一个,从对应于同一输出通道的信号彼此中、即所述第一第一方向延迟移位信号~第k第一方向延迟移位信号各者与所述第一第二方向延迟移位信号~第k第二方向延迟移位信号各者中,选择出现所述延迟脉冲信号的时机早的一者,并针对所述第一输出通道~第k输出通道的每一个,将所述选择的信号作为所述第一输出时机信号~第k输出时机信号输出。2.根据权利要求1所述的显示驱动器,其特征在于,所述第一延迟生成部包括分别与所述第一输出通道~第k输出通道对应的第一延迟电路~第k延迟电路以第一~第k的排列顺序级联连接的第一延迟电路组,且构成为向所述第一延迟电路组的所述第一延迟电路输入所述第一延迟脉冲信号,并且将所述第一延迟电路组的所述第一延迟电路~第k延迟电路的各输出作为所述第一第一方向延迟移位信号~第k第一方向延迟移位信号,且所述第二延迟生成部包括分别与所述第一输出通道~第k输出通道对应的第一延迟电路~第k延迟电路以第k~第一的排列顺序级联连接的第二延迟电路组,且构成为将所述第二延迟脉冲信号输入至所述第二延迟电路组的所述第k延迟电路,并且将所述第二延迟电路组的所述第一延迟电路~第k延迟电路的各输出作为所述第一第二方向延迟移位信号~第k第二方向延迟移位信号。3.根据权利要求2所述的显示驱动器,其特征在于,所述第一延迟电路组及所述第二延迟电路组中分别包含的所述延迟电路是触发器,所述第一延迟电路组包括第一移位寄存器,所述第一移位寄存器构成为与所述第一输出通道~第k输出通道对应的第一触发器~第k触发器以第一触发器~第k触发器的排列顺序级联连接,并且将所述第一延迟脉冲信号输入至所述第一触发器,且所述第二延迟电路组包括第二移位寄存器,所述第二移位寄存器构成为与所述第一输

出通道~第k输出通道对应的第一触发器~第k触发器以第k触发器~第一触发器的排列顺序级联连接,并且将所述第二延迟脉冲信号输入至所述第k触发器。4.根据权利要求2所述的显示驱动器,其特征在于,所述第一延迟电路组及所述第二延迟电路组中分别包含的所述延迟电路是包括相互级联连接的一对反相器元件的反相器电路,所述第一延迟电路组构成为与所述第一输出通道~第k输出通道对应的第一反相器电路~第k反相器电路以第一~第k的排列顺序级联连接,且将所述第一延迟脉冲信号输入至所述第一反相器电路,且所述第二延迟电路组构成为与所述第一输出通道~第k输出通道对应的第一反相器电路~第k反相器电路以第k~第一的排列顺序级联连接,且将所述第二延迟脉冲信号输入至所述第k反相器电路。5.根据权利要求2至4中任一项所述的显示驱动器,其特征在于,所述控制信号生成部生成与所述影像信号中的水平同步信号相应的复位信号,所述延迟选择部包括分别与所述第一输出通道~第k输出通道对应的第一延迟选择电路~第k延迟选择电路,且所述第一延迟选择电路~第k延迟选择电路分别包括:或门,接收所述第一延迟电路组中包含的所述第一延迟电路~第k延迟电路以及所述第二延迟电路组中包含的所述第一延迟电路~第k延迟电路中,对应于同一输出通道的所述第一延迟电路组中的所述延迟电路的输出与所述第二延迟电路组中的所述延迟电路的输出;及复位置位触发器,利用置位端子接收所述复位信号及所述或门的输出中的一者,并利用复位端子接收另一者,其中将从所述第一延迟选择电路~第k延迟选择电路各者的所述复位置位触发器分别输出的信号作为所述第一输出时机信号~第k输出时机信号输出。6.根据权利要求2至4中任一项所述的显示驱动器,其特征在于,所述控制信号生成部生成与所述影像信号中的水平同步信号相应的复位信号,所述延迟选择部包括分别与所述第一输出通道~第k输出通道对应的第一延迟选择电路~第k延迟选择电路,且所述第一延迟选择电路~第k延迟选择电路分别包括:第一节点;第一晶体管,根据所述复位信号对所述第一节点进行预充电;第二晶体管,根据所述第一延迟电路组中包含的所述第一延迟电路~第k延迟电路以及所述第二延迟电路组中包含的所述第一延迟电路~第k延迟电路中,对应于同一输出通道的一对所述延迟电路的其中一者的输出来对所述第一节点进行放电;及第三晶体管,根据所述一对所述延迟电路的另一者的输出对所述第一节点进行放电,其中将第一延迟选择电路~第k延迟选择电路各者的所述第一节点中分别产生的信号作为所述第一输出时机信号~第k输出时机信号输出。7.根据权利要求1所述的显示驱动器,其特征在于,所述控制信号生成部生成与所述影

像信号中的水平同步信号相应的复位信号,所述输出时机控制部、所述第一延迟生成部及第二延迟生成部以及所述延迟选择部包括分别与所述第一输出通道~第k输出通道对应的第一电路块~第k电路块级联连接而成的结构,且所述第一电路块~第k电路块分别包括:第一节点;p通道型的第一晶体管,根据所述复位信号对所述第一节点进行预充电;n通道型的第二晶体管及第三晶体管,对所述第一节点进行放电;及反相器,使所述第一节点的信号反相,其中所述第一电路块~第k-1电路块各者中包含的所述第二晶体管根据后级的所述电路块中包含的所述反相器的输出对所述第一节点进行放电,所述第二电路块~第k电路块各者中包含的所述第三晶体管根据前级的所述电路块中包含的所述反相器的输出对所述第一节点进行放电,所述第一电路块中包含的所述第三晶体管根据所述第一延迟脉冲信号对所述第一节点进行放电,所述第k电路块中包含的所述第二晶体管根据所述第二延迟脉冲信号对所述第一节点进行放电,且将所述第二电路块~第k电路块各者中包含的所述第一节点中分别产生的信号作为所述第一输出时机信号~第k输出时机信号输出。8.根据权利要求3所述的显示驱动器,其特征在于,所述控制信号生成部接收第一单位延迟时间及第二单位延迟时间的指定,生成与所述第一单位延迟时间对应的周期的第一时钟信号,并供给至所述第一延迟电路组的所述第一触发器~第k触发器的时钟端子,并且生成与所述第二单位延迟时间对应的周期的第二时钟信号,并供给至所述第二延迟电路组的所述第一触发器~第k触发器的时钟端子。9.根据权利要求4所述的显示驱动器,其特征在于,所述第一延迟电路组及所述第二延迟电路组各者的所述第一反相器电路~第k反相器电路能够基于延迟控制信号变更输出延迟时间,且所述控制信号生成部接收第一单位延迟时间及第二单位延迟时间的指定,将表示所指定的所述第一单位延迟时间的第一延迟控制信号供给至所述第一延迟电路组的所述第一反相电路~第k反相电路各者,并且将表示所指定的所述第二单位延迟时间的第二延迟控制信号供给至所述第二延迟电路组的所述第一反相电路~第k反相电路各者。

技术总结

本发明提供一种显示驱动器。在本发明中,接收显示驱动器的第一及第k输出通道各者中的输出时机的指定,在第一输出通道的输出时机生成第一延迟脉冲信号,并在第k输出通道的输出时机生成第二延迟脉冲信号。生成经过从第一向第k输出通道针对每一个输出通道所增加的延迟而出现第一延迟脉冲信号的第一~第k第一方向延迟移位信号。生成经过从第k输出通道向第一输出通道针对每一个输出通道所增加的延迟而出现第二延迟脉冲信号的第一~第k第二方向延迟移位信号。从第一~第k第一方向延迟移位信号各者与第一~第k第二方向延迟移位信号各者中,选择出现延迟脉冲信号的时机早的一者,将针对每一个输出通道所选择的信号作为第一~第k输出时机信号。第k输出时机信号。第k输出时机信号。

技术研发人员:樋口钢児

受保护的技术使用者:拉碧斯半导体株式会社

技术研发日:2021.08.18

技术公布日:2022/2/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。