1.本发明涉及一种根据影像信号驱动显示面板的显示驱动器。

背景技术:

2.在作为显示图像的显示面板的例如液晶显示面板中,在二维画面的水平方向上延伸的多条栅极线与在二维画面的垂直方向上延伸的多条源极线以交叉的方式配置。进而,在液晶显示面板中搭载有:源极驱动器,对源极线各者施加与由输入影像信号表示的各像素的亮度水平对应的灰阶显示电压;及栅极驱动器,对栅极线施加选择作为驱动对象的显示线的栅极信号。

3.作为这种源极驱动器,提出了如下源极驱动器:将1水平同步期间量的多个显示数据个别地取入至n(n为2以上的整数)个锁存器各者中,并将具有与取入至各锁存器中的显示数据对应的电压值的驱动电压施加至各源极线(例如,参照专利文献1)。

4.在所述源极驱动器中,设置与基准时机信号同步地将单一脉冲的延迟脉冲信号依次向下一级移位并取入的n(n为2以上的整数)级触发器(称为ff(flip-flop)),并将所述ff各者的输出作为取入信号个别地分别供给至n个锁存器。由此,各驱动电压被施加至源极线各者的时机错开,因此避免了同时发生流入源极线组中的电流急剧变化的状态,抑制了在这种状态下产生的噪声。

5.[现有技术文献]

[0006]

[专利文献]

[0007]

[专利文献1]日本专利特开2015-143780号公报

技术实现要素:

[0008]

[发明所要解决的问题]

[0009]

近年来,在大型化且高精细化的显示面板中,将源极驱动器分割为多个集成电路(integrated circuit,ic)芯片而构筑的多个源极驱动器ic被设置于源极线组的一端侧。

[0010]

在驱动这种显示面板的情况下,由于栅极线及源极线的线长长,因此,因伴随其线长的配线电阻而栅极信号及驱动电压的波形钝化。另外,其波形的钝化程度根据显示面板的画面内的位置而不同。例如,在显示面板的画面中央的位置,与画面两端的位置相比,距各驱动器的线长长,因此栅极信号及驱动电压的波形钝化,即延迟时间变大。因此,在显示面板的画面中央的位置与画面端部的位置,对于栅极信号而言的适当的驱动电压的输出时机不同。

[0011]

因而,考虑应用专利文献1的技术,使将驱动电压施加至各源极线的时机朝向显示面板的画面中央分别阶段性地延迟规定的单位延迟量,由此进行结合栅极信号的到达时机的驱动。

[0012]

但是,在利用多个源极驱动器进行显示面板的驱动的情况下,若相互邻接的源极驱动器彼此的相邻的输出通道间的驱动电压的输出时机的偏差量变大,则在其边界部产生

显示不均。

[0013]

因此,为了抑制这种显示不均,考虑在各源极驱动器中进行减小输出通道间的驱动电压的输出时机的延迟时间差的调整。

[0014]

然而,为了进行这种调整,需要减小决定驱动电压的输出时机的单位延迟量的电路的高频化,而产生导致电路规模增大的问题。

[0015]

另外,通过变更单位延迟量,最末尾的输出通道中的驱动电压的输出时机也会发生变化。因此,为了相对于源极驱动器的最末尾的输出通道中的驱动电压的输出时机,减小延迟时间差,还需要变更与所述源极驱动器邻接的源极驱动器的最前头的输出通道中的输出时机,因此存在所述调整变得复杂的问题。

[0016]

因而,本发明的目的在于提供一种显示驱动器,在利用多个显示驱动器来驱动显示面板时,不会导致电路规模的增大,且可容易地进行抑制显示不均的输出时机的调整。

[0017]

[解决问题的技术手段]

[0018]

本发明的显示驱动器具有输出分别与由影像信号表示的各像素的亮度水平对应的第一像素驱动电压~第k(k为2以上的整数)像素驱动电压的第一输出通道~第k输出通道,所述显示驱动器具有:输出时机控制部,生成表示所述第一输出通道~第k输出通道各者中的输出时机的第一输出时机信号~第k输出时机信号;及输出部,在由所述第一输出时机信号~第k输出时机信号各者表示的所述输出时机分别输出所述第一像素驱动电压~第k像素驱动电压;并且所述输出时机控制部具有:控制信号生成部,接收所述第一输出通道及第k输出通道各者中的输出时机的指定,在所指定的所述第一输出通道的输出时机生成第一延迟脉冲信号,并且在所指定的所述第k输出通道的输出时机生成第二延迟脉冲信号;第一延迟生成部,接收所述第一延迟脉冲信号,生成经过从所述第一输出通道向所述第k输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现所述第一延迟脉冲信号的第一第一方向延迟移位信号~第k第一方向延迟移位信号;第二延迟生成部,接收所述第二延迟脉冲信号,生成经过从所述第k输出通道向所述第一输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现所述第二延迟脉冲信号的第一第二方向延迟移位信号~第k第二方向延迟移位信号;及延迟选择部,针对所述第一输出通道~第k输出通道的每一个,从对应于同一输出通道的信号彼此中、即所述第一第一方向延迟移位信号~第k第一方向延迟移位信号各者与所述第一第二方向延迟移位信号~第k第二方向延迟移位信号各者中,选择出现所述延迟脉冲信号的时机早的一者,并针对所述第一输出通道~第k输出通道的每一个,将所述选择的信号作为所述第一输出时机信号~第k输出时机信号输出。

[0019]

[发明的效果]

[0020]

在本发明中,在调整显示驱动器的第一输出通道~第k(k为2以上的整数)输出通道各者的输出时机时,首先,接收第一输出通道及第k输出通道中的输出时机的指定。其次,在所指定的第一输出通道的输出时机生成第一延迟脉冲信号,并在所指定的第k输出通道的输出时机生成第二延迟脉冲信号。此处,生成经过从第一输出通道向第k输出通道针对每一个输出通道所增加的延迟而出现第一延迟脉冲信号的第一第一方向延迟移位信号~第k第一方向延迟移位信号。进而,生成经过从第k输出通道向第一输出通道针对每一个输出通道所增加的延迟而出现第二延迟脉冲信号的第一第二方向延迟移位信号~第k第二方向延迟移位信号。其次,从对应于同一输出通道的信号彼此中、即第一第一方向延迟移位信号~

第k第一方向延迟移位信号各者与第一第二方向延迟移位信号~第k第二方向延迟移位信号各者中,选择出现延迟脉冲信号的时机早的一者。然后,将针对第一输出通道~第k输出通道的每一个所选择的信号作为第一输出时机信号~第k输出时机信号,在依照所述第一输出时机信号~第k输出时机信号的输出时机,输出与各像素对应的第一像素驱动电压~第k像素驱动电压。

[0021]

由此,在利用多个显示驱动器来驱动显示面板时,通过针对每一个显示驱动器指定第一输出通道及第二输出通道各者中的输出时机,能够进行以下调整:在不缩短单位延迟时间的情况下,减小相互邻接的显示驱动器彼此的边界部的输出时机的延迟时间差。

[0022]

因此,根据本发明,在利用多个显示驱动器来驱动显示面板时,不会导致电路规模的增大,且可容易地进行抑制显示不均的输出时机调整。

附图说明

[0023]

图1是表示包括本发明的显示驱动器的显示装置100的概略结构的框图。

[0024]

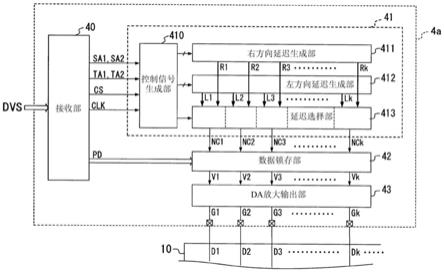

图2是表示驱动器ic 4a的内部结构的一例的框图。

[0025]

图3是表示基于右方向延迟移位信号r1~右方向延迟移位信号rk的延迟特性dr、以及基于左方向延迟移位信号l1~左方向延迟移位信号lk的三个系统的延迟特性dl1~延迟特性dl3的例子的图。

[0026]

图4a是表示r移位模式中的输出时机延迟特性的图。

[0027]

图4b是表示l移位模式中的输出时机延迟特性的图。

[0028]

图4c是表示v移位模式中的输出时机延迟特性的图。

[0029]

图5是表示根据开始时机设定数据ta1及开始时机设定数据ta2的指定进行调整后的输出时机的延迟形态的一例的图。

[0030]

图6是表示根据开始时机设定数据ta1及开始时机设定数据ta2进行调整后的驱动器ic4a及驱动器ic 4b各者中的输出时机的延迟形态的一例的图。

[0031]

图7是表示右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的内部结构的一例的电路图。

[0032]

图8是表示右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的动作的一例的时序图。

[0033]

图9是表示右方向延迟生成部411、及左方向延迟生成部412的内部结构的另一例的电路图。

[0034]

图10是表示延迟选择部413的内部结构的一例的电路图。

[0035]

图11是表示延迟选择部413的内部结构的另一例的电路图。

[0036]

图12是表示将右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的功能以经简化的结构来实现的电路的电路图。

[0037]

符号的说明

[0038]

10:显示面板

[0039]

20:驱动控制部

[0040]

40:源极驱动器

[0041]

41:输出时机控制部

[0042]

42:数据锁存部

[0043]

410:控制信号生成部

[0044]

411:右方向延迟生成部

[0045]

412:左方向延迟生成部

[0046]

413:延迟选择部

具体实施方式

[0047]

以下,参照附图详细说明本发明的实施例。

[0048]

图1是表示包括本发明的显示驱动器的显示装置100的概略结构的图。如图1所示,所述显示装置100包括驱动控制部20、栅极驱动器30a及栅极驱动器30b、源极驱动器40以及显示面板10。此外,源极驱动器40包括分别具有相同结构的多个半导体ic(integrated circuit)芯片。例如在图1所示的实施例中,源极驱动器40包括五个驱动器ic 4a~驱动器ic 4e,所述五个驱动器ic 4a~驱动器ic 4e分别具有将源极驱动器40的n个(n为2以上的自然数)输出通道5分割后的k个(k为2以上的整数)输出通道。

[0049]

显示面板10例如包括液晶或有机电致发光(electroluminescence,el)面板等。在显示面板10中包括分别在二维画面的水平方向上延伸的m个(m为2以上的整数)水平扫描线s1~水平扫描线sm、以及分别在二维画面的垂直方向上延伸的n个数据线d1~数据线dn。在栅极线及源极线的各交叉部形成有担载像素的显示单元。

[0050]

驱动控制部20接收作为显示对象的影像信号,从所述影像信号中提取水平同步信号及垂直同步信号,并将水平同步信号供给至栅极驱动器30a及栅极驱动器30b。

[0051]

另外,驱动控制部20基于所述影像信号,针对每一个像素,生成用例如8位来表示所述像素的亮度水平的像素数据pd的系列。

[0052]

进而,驱动控制部20将包括以下的延迟移位量设定数据sa1及延迟移位量设定数据sa2、开始时机设定数据ta1及开始时机设定数据ta2、以及同步信号cs的影像数据信号dvs与像素数据pd的系列及基准时钟信号clk一起供给至源极驱动器40。

[0053]

同步信号cs例如包括水平同步信号。

[0054]

延迟移位量设定数据sa1是针对驱动器ic 4a~驱动器ic 4e的每一个指定从第一输出通道向第k输出通道(也称为右方向),阶段性地增加对输出时机实施的延迟时的单位延迟时间的数据。

[0055]

延迟移位量设定数据sa2是针对驱动器ic 4a~驱动器ic 4e的每一个指定从第k输出通道向第一输出通道(也称为左方向),阶段性地增加对所述输出时机实施的延迟时的单位延迟时间的数据。

[0056]

开始时机设定数据ta1是针对驱动器ic 4a~驱动器ic 4e的每一个指定第一输出通道中的输出时机的数据。

[0057]

开始时机设定数据ta2是针对驱动器ic 4a~驱动器ic 4e的每一个指定第k输出通道中的输出时机的数据。

[0058]

栅极驱动器30a与栅极线s1~栅极线sm各者的一端连接,栅极驱动器30b与栅极线s1~栅极线sm各者的另一端连接。栅极驱动器30a及栅极驱动器30b与水平同步信号同步地生成栅极脉冲,并将栅极脉冲依次施加至显示面板10的栅极线s1~栅极线sm各者。

[0059]

源极驱动器40基于所述影像数据信号dvs,生成分别与显示面板10的源极线d1~源极线dn对应的n个像素驱动电压g1~像素驱动电压gn,并输出至源极线d1~源极线dn。

[0060]

此处,构成源极驱动器40的驱动器ic 4a生成分别与显示面板10的源极线d1~源极线dn中的k个源极线d1~源极线dk对应的像素驱动电压g1~像素驱动电压gk,并将它们分别输出至源极线d1~源极线dk。驱动器ic 4b生成分别与源极线d1~源极线dn中的k个源极线dk 1~源极线dr(r为2

·

k)对应的像素驱动电压gk 1~像素驱动电压gr,并将它们分别输出至源极线dk 1~源极线dr。驱动器ic 4c生成分别与源极线d1~源极线dn中的k个源极线dr 1~源极线dy(y为3

·

k)对应的像素驱动电压gr 1~像素驱动电压gy,并将它们分别输出至源极线dr 1~源极线dy。驱动器ic 4d生成分别与源极线d1~源极线dn中的k个源极线dy 1~源极线dq(q为4

·

k)对应的像素驱动电压gy 1~像素驱动电压gq,并将它们分别输出至源极线dy 1~源极线dq。驱动器ic 4e生成分别与源极线d1~源极线dn中的k个源极线dq 1~源极线dn对应的像素驱动电压gq 1~像素驱动电压gn,并将它们分别输出至源极线dq 1~源极线dn。

[0061]

图2是从驱动器ic 4a~驱动器ic 4e中抽取驱动器ic 4a,来表示源极驱动器的内部结构的框图。

[0062]

如图2所示,驱动器ic 4a包括接收部40、输出时机控制部41、数据锁存部42、以及数字模拟(digital analog,da)放大输出部43。

[0063]

接收部40接收影像数据信号dvs,从所述影像数据信号dvs中提取像素数据pd的系列、延迟移位量设定数据sa1及延迟移位量设定数据sa2、开始时机设定数据ta1及开始时机设定数据ta2、以及同步信号cs。接收部40将提取出的延迟移位量设定数据sa1及延迟移位量设定数据sa2、开始时机设定数据ta1及开始时机设定数据ta2、以及同步信号cs供给至输出时机控制部41,并且将提取出的像素数据pd的系列供给至数据锁存部42。

[0064]

输出时机控制部41接收所述同步信号cs及基准时钟信号clk、以及包括延迟移位量设定数据sa1及延迟移位量设定数据sa2、以及开始时机设定数据ta1及开始时机设定数据ta2的输出延迟控制数据。

[0065]

输出时机控制部41基于这些同步信号cs、基准时钟信号clk以及输出延迟控制数据(sa1、sa2、ta1、ta2),生成表示第一输出通道~第k输出通道各者的输出时机的输出时机信号nc1~输出时机信号nck。即,输出时机控制部41在延迟各输出通道中的输出时机时,生成针对每一个输出通道变化了其延迟时间后的输出时机信号nc1~输出时机信号nck。输出时机控制部41将所生成的输出时机信号nc1~输出时机信号nck供给至数据锁存部42。

[0066]

数据锁存部42锁存从接收部40供给的像素数据pd的系列中的连续的k个像素数据pd,并将它们分别作为像素数据v1~像素数据vk,在由输出时机信号nc1~输出时机信号nck表示的各输出时机输出至da放大输出部43。

[0067]

da放大输出部43将像素数据v1~像素数据vk转换为具有与各自所表示的亮度水平对应的模拟的电压值的k个灰阶电压,将个别地放大这些k个灰阶电压后的电压作为像素驱动电压g1~像素驱动电压gk输出。

[0068]

由此,驱动器ic 4a基于输出延迟控制数据(sa1、sa2、ta1、ta2),在针对每一个输出通道变化了其延迟时间后的输出时机输出像素驱动电压g1~像素驱动电压gk。从驱动器ic 4a输出的像素驱动电压g1~像素驱动电压gk被施加至显示面板10的源极线d1~源极线

dk。

[0069]

此外,如图2所示,输出时机控制部41包括控制信号生成部410、右方向延迟生成部411、左方向延迟生成部412、及延迟选择部413。

[0070]

控制信号生成部410基于输出延迟控制数据(sa1、sa2、ta1、ta2),在与基准时钟信号clk及同步信号cs同步的时机,生成控制右方向延迟生成部411及左方向延迟生成部412的各种控制信号。进而,控制信号生成部410在与同步信号cs同步的时机生成控制延迟选择部413的控制信号。

[0071]

右方向延迟生成部411生成从第一输出通道向第k输出通道,每一个输出通道分别延迟单位延迟时间而出现单一的延迟脉冲信号的右方向延迟移位信号r1~右方向延迟移位信号rk。

[0072]

具体而言,右方向延迟生成部411生成以同步信号cs(水平同步信号)为基点的、在由开始时机设定数据ta1指定的输出时机出现延迟脉冲信号的右方向延迟移位信号r1。而且,右方向延迟生成部411生成从第一输出通道向第k输出通道,每一个输出通道分别延迟由延迟移位量设定数据sa1指定的单位延迟时间而出现延迟脉冲信号的右方向延迟移位信号r2~右方向延迟移位信号rk。

[0073]

右方向延迟生成部411将如上所述那样生成的右方向延迟移位信号r1~右方向延迟移位信号rk供给至延迟选择部413。

[0074]

左方向延迟生成部412基于从控制信号生成部410供给的各种控制信号,生成从第k输出通道向第一输出通道,每一个输出通道分别延迟单位延迟时间而出现单一的延迟脉冲信号的左方向延迟移位信号l1~左方向延迟移位信号lk。

[0075]

具体而言,左方向延迟生成部412生成以同步信号cs(水平同步信号)为基点的、在由开始时机设定数据ta2指定的输出时机出现延迟脉冲信号的左方向延迟移位信号lk。而且,左方向延迟生成部412生成从第k输出通道向第一输出通道,每一个输出通道分别延迟由延迟移位量设定数据sa2指定的单位延迟时间而出现延迟脉冲信号的左方向延迟移位信号lk-1~左方向延迟移位信号l1。

[0076]

左方向延迟生成部412将如上所述那样生成的左方向延迟移位信号l1~左方向延迟移位信号lk供给至延迟选择部413。

[0077]

延迟选择部413针对各输出通道的每一个,从对应于同一输出通道的信号彼此中、即右方向延迟移位信号(r1~rk)及左方向延迟移位信号(l1~lk)中,选择出现延迟脉冲信号的时机早的一者。而且,延迟选择部413针对第一输出通道~第k输出通道的每一个,将如上所述那样选择的信号作为输出时机信号nc1~输出时机信号nck供给至数据锁存部42。

[0078]

例如,当在与第一输出通道对应的右方向延迟移位信号r1及左方向延迟移位信号l1中,右方向延迟移位信号r1的出现延迟脉冲信号的时机早时,延迟选择部413选择右方向延迟移位信号r1。此时,延迟选择部413将所选择的右方向延迟移位信号r1作为输出时机信号nc1供给至数据锁存部42。另外,当在与第二输出通道对应的右方向延迟移位信号r2及左方向延迟移位信号l2中,左方向延迟移位信号l2的出现延迟脉冲信号的时机早时,延迟选择部413选择左方向延迟移位信号l2。此时,延迟选择部413将所选择的左方向延迟移位信号l2作为输出时机信号nc2供给至数据锁存部42。

[0079]

图3是表示基于右方向延迟移位信号r1~右方向延迟移位信号rk的延迟脉冲的延

迟特性dr的一例、及作为基于左方向延迟移位信号l1~左方向延迟移位信号lk的延迟脉冲的延迟特性的三系统的延迟特性dl1~延迟特性dl3的例子的图。

[0080]

延迟特性dl1是在利用开始时机设定数据ta2指定较延迟特性dr中的第k输出通道的输出时机晚的时机时获得的特性。此时,与延迟特性dr对应的右方向延迟移位信号r(t)(t为1~k的整数)和与延迟特性dl1对应的左方向延迟移位信号l(t)相比,出现延迟脉冲信号的时机早。

[0081]

因此,在接收到与延迟特性dr对应的右方向延迟移位信号r1~右方向延迟移位信号rk、及与延迟特性dl1对应的左方向延迟移位信号l1~左方向延迟移位信号lk的情况下,延迟选择部413选择右方向延迟移位信号r1~右方向延迟移位信号rk,将它们分别作为输出时机信号nc1~输出时机信号nck输出。根据所述输出时机信号nc1~输出时机信号nck,如图4a所示,沿着从第一输出通道向第k输出通道,输出时机的延迟时间增加的输出时机延迟特性(r移位模式),输出分别与第一输出通道~第k输出通道对应的像素驱动电压g1~像素驱动电压gn。

[0082]

延迟特性dl2是在以与第一输出通道对应的输出时机早于由开始时机设定数据ta1指定的输出时机的方式设定了开始时机设定数据ta2时获得的特性。此时,与延迟特性dl2对应的左方向延迟移位信号l(t)(t为1~k的整数)和与延迟特性dr对应的右方向延迟移位信号r(t)相比,出现延迟脉冲信号的时机早。

[0083]

因此,在接收到与延迟特性dr对应的右方向延迟移位信号r1~右方向延迟移位信号rk、及与延迟特性dl2对应的左方向延迟移位信号l1~左方向延迟移位信号lk的情况下,延迟选择部413选择左方向延迟移位信号l1~左方向延迟移位信号lk,将它们分别作为输出时机信号nc1~输出时机信号nck输出。根据所述输出时机信号nc1~输出时机信号nck,如图4b所示,沿着从第k输出通道向第一输出通道输出时机的延迟时间增加的输出时机延迟特性(l移位模式),输出分别与第一输出通道~第k输出通道对应的像素驱动电压g1~像素驱动电压gn。

[0084]

延迟特性dl3是在以使左方向延迟移位信号l1晚于右方向延迟移位信号r1,且左方向延迟移位信号lk早于右方向延迟移位信号rk的方式指定了开始时机设定数据ta2时获得的特性。

[0085]

如图3所示,与沿着延迟特性dr的第一输出通道~第w(w为2~k-1范围内的整数)输出通道对应的右方向延迟移位信号r(u)(u为1~w的整数)和沿着延迟特性dl3的第一输出通道~第w输出通道中的左方向延迟移位信号l(u)相比,出现延迟脉冲信号的时机早。另外,沿着延迟特性dl3的第w 1输出通道~第k输出通道中的左方向延迟移位信号l(x)(x为w 1~k的整数)和沿着延迟特性dr的第w 1输出通道~第k输出通道中的右方向延迟移位信号r(x)相比,出现延迟脉冲信号的时机早。

[0086]

因此,延迟选择部413从左方向延迟移位信号l1~左方向延迟移位信号lk及右方向延迟移位信号r1~右方向延迟移位信号rk中选择右方向延迟移位信号r1~右方向延迟移位信号rw及左方向延迟移位信号lw 1~左方向延迟移位信号lk,并将它们作为输出时机信号nc1~输出时机信号nck输出。根据所述输出时机信号nc1~输出时机信号nck,如图4c所示,沿着以第w输出通道为边界在输出时机所施加的延迟时间的变化倾向从增加切换为降低的输出时机延迟特性(v移位模式),输出分别与第一输出通道~第k输出通道对应的像

素驱动电压g1~像素驱动电压gn。

[0087]

此外,在所述v移位模式中,可通过指定开始时机设定数据ta2,不变更所述单位延迟时间地调整第k输出通道中的输出时机。

[0088]

图5是表示根据开始时机设定数据ta1及开始时机设定数据ta2的指定进行调整后的输出时机的延迟形态的一例的图。

[0089]

如图5所示,在将由开始时机设定数据ta2指定的第k输出通道中的输出时机设为“a”的情况下,第k输出通道中的输出时机比第一输出通道中的输出时机晚延迟时间ta。另外,如图5所示,在将由开始时机设定数据ta2指定的第k输出通道中的输出时机设为比“a”晚的“b”的情况下,第k输出通道中的输出时机比第一输出通道中的输出时机晚延迟时间tb(ta<tb)。此时,如图5所示,第k输出通道中的延迟时间越长,成为从第一输出通道向第k输出通道在各输出时机所施加的延迟时间从增加的倾向切换为降低的倾向的边界的输出通道越接近第k输出通道侧。

[0090]

图6是表示从图1所示的驱动器ic 4a~驱动器ic 4e中抽取相互邻接配置的驱动器ic 4a及驱动器ic 4b,由开始时机设定数据ta1及开始时机设定数据ta2调整后的输出时机的延迟形态的一例的图。

[0091]

在图6所示的一例中,向驱动器ic 4a供给指定“a1”作为第一输出通道中的输出时机的开始时机设定数据ta1、及指定“a2”作为第k输出通道中的输出时机的开始时机设定数据ta2。另一方面,向与所述驱动器ic 4a邻接配置的驱动器ic 4b供给指定“a2”或“a2”附近的值作为第一输出通道中的输出时机的开始时机设定数据ta1。

[0092]

因此,根据输出时机控制部41,通过指定开始时机设定数据ta1及开始时机设定数据ta2,可在不缩短单位延迟时间的情况下,进行减小相互邻接的驱动器ic(源极驱动器)彼此的相邻的输出通道间的输出时机的延迟时间差的调整。

[0093]

因此,根据本发明,不会导致电路规模的增大,且可容易地进行抑制显示不均的输出时机的调整。

[0094]

以下,对图2所示的输出时机控制部41中包含的右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的具体结构进行说明。

[0095]

图7是表示右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的内部结构的一例的电路图。

[0096]

此外,在采用图7所示的结构的情况下,控制信号生成部410基于输出延迟控制数据(sa1、sa2、ta1、ta2)、基准时钟信号clk及同步信号cs,生成以下的延迟脉冲信号ldr、延迟脉冲信号ldl、复位信号rst、时钟信号clk1及时钟信号clk2。

[0097]

即,控制信号生成部410使用基准时钟信号clk生成如图8所示的时钟信号clk1,所述时钟信号clk1以由延迟移位量设定数据sa1指定的单位延迟时间为一个周期。另外,控制信号生成部410使用基准时钟信号clk生成如图8所示的时钟信号clk2,所述时钟信号clk2以由延迟移位量设定数据sa2指定的单位延迟时间为一个周期。

[0098]

此外,在图8所示的一例中,在时钟信号clk1及时钟信号clk2的周期相同,但是由延迟移位量设定数据sa1及延迟移位量设定数据sa2指定的单位延迟时间互不相同的情况下,时钟信号clk1及时钟信号clk2的周期也互不相同。

[0099]

另外,控制信号生成部410根据同步信号cs(水平同步信号)来生成如图8所示的单

一脉冲的复位信号rst。

[0100]

另外,控制信号生成部410在以图8所示的复位信号rst的上升边缘部的时机为基点的、由开始时机设定数据ta1指定的输出时机,生成如图8所示的单一脉冲的延迟脉冲信号ldr。

[0101]

进而,控制信号生成部410在以图8所示的复位信号rst的上升边缘部的时机为基点的、由开始时机设定数据ta2指定的输出时机,生成如图8所示的单一脉冲的延迟脉冲信号ldl。

[0102]

控制信号生成部410将时钟信号clk1及延迟脉冲信号ldr供给至右方向延迟生成部411,并将时钟信号clk2及延迟脉冲信号ldl供给至左方向延迟生成部412。另外,控制信号生成部410将复位信号rst供给至延迟选择部413。

[0103]

右方向延迟生成部411包括如下移位寄存器:如图7所示,作为分别与第一输出通道~第k输出通道对应的第一延迟电路~第k延迟电路的触发器df1~触发器dfk以第一~第k的排列顺序级联连接。触发器df1~触发器dfk利用各自的时钟端子接收时钟信号clk1。触发器df1接收图8所示的单一脉冲的延迟脉冲信号ldr,并将其在时钟信号clk1的时机输出,供给至下一级的触发器df2。同样,触发器df2~触发器dfk分别将前一级的触发器df所输出的延迟脉冲信号ldr在时钟信号clk1的时机供给至下一级的触发器df。

[0104]

在右方向延迟生成部411中,将从触发器df1~触发器dfk中分别输出的输出信号作为右方向延迟移位信号r1~右方向延迟移位信号rk,供给至延迟选择部413。

[0105]

左方向延迟生成部412包括如下移位寄存器:如图7所示,作为分别与第一输出通道~第k输出通道对应的第一延迟电路~第k延迟电路的触发器df11~触发器df1k以第k~第一的排列顺序级联连接。触发器df1k~触发器df11利用各自的时钟端子接收时钟信号clk2。触发器df1k接收图8所示的单一脉冲的延迟脉冲信号ldl,并将其在时钟信号clk2的时机输出,供给至下一级的触发器df1k-1。同样,触发器df1k-1~触发器df11分别将前一级的触发器df所输出的延迟脉冲信号ldl在时钟信号clk2的时机供给至下一级的触发器df。

[0106]

在左方向延迟生成部412中,将从触发器df11~触发器df1k中分别输出的输出信号作为左方向延迟移位信号l1~左方向延迟移位信号lk,供给至延迟选择部413。

[0107]

延迟选择部413具有分别对应于第一输出通道~第k输出通道而设置的延迟选择电路se1~延迟选择电路sek。延迟选择电路se1~延迟选择电路sek分别包括同一电路结构,分别接收复位信号rst。进而,延迟选择电路se1~延迟选择电路sek分别接收与自身的输出通道对应的一对右方向延迟移位信号r(f)(f为1~k的整数)及左方向延迟移位信号l(f)。例如,如图8所示,延迟选择电路se1接收右方向延迟移位信号r1及左方向延迟移位信号l1。另外,延迟选择电路se2接收右方向延迟移位信号r2及左方向延迟移位信号l2。

[0108]

如图8所示,延迟选择电路se1~延迟选择电路sek在复位信号rst的上升边缘部的时机一起将各自所输出的输出时机信号nc1~输出时机信号nck从逻辑电平0复位为逻辑电平1的状态。其后,延迟选择电路se1~延迟选择电路sek分别在自身所接收的右方向延迟移位信号r(f)及左方向延迟移位信号l(f)中,在出现延迟脉冲信号的时机早的时机,使输出时机信号nc(f)转变为逻辑电平0。

[0109]

例如,在图8所示的一例中,在右方向延迟移位信号r1及左方向延迟移位信号l1中,右方向延迟移位信号r1的出现延迟脉冲信号的时机早。因此,如图8所示,接收所述一对

右方向延迟移位信号r1及左方向延迟移位信号l1的延迟选择电路se1选择右方向延迟移位信号r1,并在其上升边缘部的时机,使输出时机信号nc1从逻辑电平1转变为逻辑电平0的状态。

[0110]

此外,在采用图7所示的电路结构作为右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的情况下,图8所示的输出时机信号nc1~输出时机信号nck各者的下降边缘部的时点成为输出时机。由此,数据锁存部42在输出时机信号nc1~输出时机信号nck各者的后边缘部的时机输出锁存的k个像素数据pd。

[0111]

图9是表示右方向延迟生成部411、及左方向延迟生成部412的内部结构的另一例的电路图。此外,在图9中,延迟选择部413的内部结构与图7所示的相同,因此省略其说明。

[0112]

在图9所示的结构中,代替作为右方向延迟生成部411的延迟电路而所采用的图7所示的触发器df1~触发器dfk,而采用包括相互级联连接的一对反相器元件的反相器电路iv1~反相器电路ivk。另外,作为左方向延迟生成部412的延迟电路,代替图7所示的触发器df1k~触发器df11,而采用包括级联的两级反相器的反相器电路iv1k~反相器电路iv11。此外,反相器电路iv1~反相器电路ivk及反相器电路iv1k~反相器电路iv11分别是从接收输入信号到进行输出为止所需的元件延迟时间能够根据延迟控制信号进行变更的延迟可变元件。

[0113]

另外,控制信号生成部410将表示由延迟移位量设定数据sa1指定的单位延迟时间的延迟控制信号dc1代替时钟信号clk1而供给至反相器电路iv1~反相器电路ivk。由此,反相器电路iv1~反相器电路ivk分别使从前一级供给的延迟脉冲信号ldr延迟由延迟控制信号dc1所示的延迟时间,并输出至下一级的反相器电路。

[0114]

另外,控制信号生成部410将表示由延迟移位量设定数据sa2指定的单位延迟时间的延迟控制信号dc2代替时钟信号clk2而供给至反相器电路iv1k~反相器电路iv11。由此,反相器电路iv1k~反相器电路iv11分别使从前一级供给的延迟脉冲信号ldl延迟由延迟控制信号dc2所示的延迟时间,并输出至下一级的反相器电路。

[0115]

图10是表示实现图8所示的动作的、图7或图9所示的延迟选择电路se1~延迟选择电路sek的内部结构的一例的电路图。

[0116]

如图10所示,延迟选择电路se1~延迟选择电路sek分别包含同一结构,即或门(or gate)51及复位置位(reset set,rs)触发器52。

[0117]

或门51接收对应于同一输出通道的一对右方向延迟移位信号r(f)(f为1~k的整数)及左方向延迟移位信号l(f),将两者的逻辑和的结果供给至rs触发器52的复位端子。此外,或门51在右方向延迟移位信号r(f)及左方向延迟移位信号l(f)中至少一者表示逻辑电平1的情况下,将促使复位的逻辑电平1的信号供给至rs触发器52的复位端子。

[0118]

另外,rs触发器52利用自身的置位端子接收复位信号rst。rs触发器52在自身的置位端子接收到逻辑电平1的复位信号rst时成为置位状态,输出逻辑电平1的信号。另一方面,在自身的复位端子接收到逻辑电平1的信号时成为复位状态,输出逻辑电平0的信号。

[0119]

延迟选择电路se1~延迟选择电路sek将从各自的rs触发器52输出的信号作为输出时机信号nc1~输出时机信号nck输出至数据锁存部42。

[0120]

此外,在图10所示的一例中,将或门51的逻辑和结果,即或门的输出供给至rs触发器52的复位端子,将复位信号rst供给至rs触发器52的置位端子,但也可将或门的输出供给

至置位端子,将复位信号rst供给至复位端子。此时,输出时机信号nc1~输出时机信号nck各者的上升边缘部的时点成为输出时机。总之,只要是将或门的输出供给至rs触发器52的复位端子及置位端子中的其中一者,将复位信号rst供给至rs触发器52的复位端子及置位端子中的另一者的结构即可。

[0121]

图11是表示实现图8所示的动作的、图7或图9所示的延迟选择电路se1~延迟选择电路sek的内部结构的另一例的电路图。

[0122]

此外,当采用图11所示的电路结构作为延迟选择电路se1~延迟选择电路sek各者时,控制信号生成部410生成使复位信号rst的逻辑电平反相的反相复位信号xrst,来代替图8所示的所述复位信号rst。

[0123]

如图11所示,延迟选择电路se1~延迟选择电路sek分别包含同一结构,即p通道金属氧化物半导体(metal oxide semiconductor,mos)型晶体管q1、n通道mos型晶体管q2及n通道mos型晶体管q3。

[0124]

晶体管q1利用自身的栅极接收图8所示的反相复位信号xrst。晶体管q1在所述反相复位信号xrst处于逻辑电平0的状态的期间成为导通状态,通过将基于电源电压vdd的电流送出至节点n1,而在所述节点n1蓄积电荷(预充电)。晶体管q1通过所述预充电而使所述节点n1的电压上升,从而达到逻辑电平1的状态。

[0125]

晶体管q2利用自身的栅极接收对应于同一输出通道的一对右方向延迟移位信号r(f)(f为1~k的整数)及左方向延迟移位信号l(f)中的右方向延迟移位信号r(f)。晶体管q2在右方向延迟移位信号r(f)处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点n1中的电荷放电(放电)。由此,晶体管q2使所述节点n1达到逻辑电平0的状态。

[0126]

晶体管q3利用自身的栅极接收对应于同一输出通道的一对右方向延迟移位信号r(f)及左方向延迟移位信号l(f)中的左方向延迟移位信号l(f)。晶体管q3在左方向延迟移位信号l(f)处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点n1中的电荷放电(放电)。由此,晶体管q3使所述节点n1达到逻辑电平0的状态。

[0127]

延迟选择电路se1~延迟选择电路sek将各自的节点n1的电压作为输出时机信号nc1~输出时机信号nck输出至数据锁存部42。

[0128]

在图11所示的结构中,在图8所示的反相复位信号xrst为逻辑电平0的期间,延迟选择电路se1~延迟选择电路sek各者的节点n1被晶体管q1预充电,节点n1被设定为逻辑电平1的状态。由此,对于分别与节点n1的状态对应的输出时机信号nc1~输出时机信号nck,如图8所示,也一起设定为逻辑电平1的状态。其后,在右方向延迟移位信号r(f)及左方向延迟移位信号l(f)中,在先成为逻辑电平1的状态的一者中,晶体管q2或晶体管q3对蓄积于节点n1中的电荷进行放电。由此,输出时机信号nc从逻辑电平1转变为逻辑电平0的状态。

[0129]

例如,如图8所示,在与第一输出通道对应的右方向延迟移位信号r1及左方向延迟移位信号l1中,右方向延迟移位信号r1先转变为逻辑电平1的状态。因此,如图8所示,通过在右方向延迟移位信号r1的上升边缘部的时机,延迟选择电路se1的晶体管q2对节点n1进行放电,如图8所示,作为延迟选择电路se1的输出的输出时机信号nc1转变为逻辑电平0的状态。

[0130]

图12是表示将由图2所示的右方向延迟生成部411、左方向延迟生成部412及延迟选择部413带来的功能以经简化的结构来实现的电路的电路图。

[0131]

图12所示的电路具有分别与第一输出通道~第k输出通道对应的、分别包括相同电路结构的电路块bc1~电路块bck。

[0132]

电路块bc1~电路块bck分别包括反相器it、p通道mos型晶体管u1、n通道mos型晶体管u2及n通道mos型晶体管u3。

[0133]

电路块bc1~电路块bck各者的晶体管u1利用自身的栅极接收图8所示的反相复位信号xrst。晶体管u1在所述反相复位信号xrst处于逻辑电平0的状态的期间成为导通状态,将基于电源电压vdd的电流送出至节点nd,在所述节点nd蓄积电荷(预充电)。晶体管u1通过所述预充电而使所述节点nd的电压上升,从而达到逻辑电平1的状态。

[0134]

电路块bc1~电路块bck中,除与第k输出通道对应的电路块bck以外的各电路块bc的晶体管u2利用自身的栅极接收从与下一级的输出通道对应的电路块bc输出的反相输出时机信号。晶体管u2在所述反相输出时机信号处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点nd中的电荷放电(放电)。由此,晶体管u2使所述节点nd达到逻辑电平0的状态。

[0135]

与第k输出通道对应的电路块bck的晶体管u2利用自身的栅极接收基于开始时机设定数据ta2的延迟脉冲信号ldl。电路块bck的晶体管u2在延迟脉冲信号ldl处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点nd中的电荷放电(放电)。由此,所述晶体管u2使所述节点nd达到逻辑电平0的状态。

[0136]

电路块bc1~电路块bck中,与第一输出通道对应的电路块bc1的晶体管u3利用自身的栅极接收基于开始时机设定数据ta1的延迟脉冲信号ldr。电路块bc1的晶体管u3在延迟脉冲信号ldr处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点nd中的电荷放电(放电)。由此,电路块bc1的晶体管u3使所述节点nd达到逻辑电平0的状态。

[0137]

电路块bc1的反相器it将使节点nd的逻辑电平反相后的信号作为所述反相输出时机信号供给至下一级的电路块bc1的晶体管u3的栅极。

[0138]

电路块bc1~电路块bck中的bc2~bck-1各者的反相器it将使节点nd的逻辑电平反相后的信号作为所述反相输出时机信号,供给至下一级的电路块bc各者的晶体管u3及前一级的电路块bc各者的晶体管u2的栅极。

[0139]

电路块bck的反相器it将使节点nd的逻辑电平反相后的信号作为所述反相输出时机信号供给至前一级的电路块bck-1的晶体管u2的栅极。

[0140]

电路块bc2~电路块bck各者的晶体管u3接收从前一级的电路块bc输出的反相输出时机信号,在所述反相输出时机信号处于逻辑电平1的状态的期间成为导通状态,使蓄积于节点nd中的电荷放电(放电)。由此,电路块bc2~电路块bck各者的晶体管u3使所述节点nd达到逻辑电平0的状态。

[0141]

电路块bc1~电路块bck将各自的节点nd的电压作为输出时机信号nc1~输出时机信号nck输出至数据锁存部42。

[0142]

在图12所示的结构中,如图8所示,首先,根据逻辑电平0的反相复位信号xrst,电路块bc1~电路块bck各者的晶体管u1对节点nd进行预充电。由此,如图8所示,输出时机信号nc1~输出时机信号nck一起成为逻辑电平1的状态。

[0143]

继而,当图8所示的延迟脉冲信号ldr被供给至电路块bc1的晶体管u3的栅极时,电路块bc1的节点nd被放电,如图8所示,输出时机信号nc1转变为逻辑电平0。由此,电路块bc1

的反相器it将逻辑电平1的反相输出时机信号供给至下一级的电路块bc2的晶体管u3的栅极。于是,通过电路块bc2的晶体管u3而所述电路块bc2的节点nd被放电,如图8所示,输出时机信号nc2转变为逻辑电平0。

[0144]

另外,在此期间,当图8所示的延迟脉冲信号ldl被供给至电路块bck的晶体管u2的栅极时,电路块bck的节点nd被放电,如图8所示,输出时机信号nck转变为逻辑电平0。由此,电路块bck的反相器it将逻辑电平1的反相输出时机信号供给至前一级的电路块bck-1的晶体管u2的栅极。于是,通过电路块bck-1的晶体管u2而所述电路块bck-1的节点nd被放电,如图8所示,输出时机信号nck-1转变为逻辑电平0。

[0145]

如上所述,在采用图12所示的结构作为右方向延迟生成部411、左方向延迟生成部412及延迟选择部413的情况下,也可实现图3~图6及图8所示的动作。

[0146]

此外,在图2所示的一例中,通过在输出时机信号nc1~输出时机信号nck的输出时机输出由数据锁存部42锁存的k个像素数据pd,来调整像素驱动电压g1~像素驱动电压gk的各输出通道的每一个的输出时机,但也可在输出时机信号nc1~输出时机信号nck的输出时机输出像素驱动电压g1~像素驱动电压gk。

[0147]

总之,作为本发明的显示驱动器(例如4a~4e),只要是具有以下的输出时机控制部及输出部的驱动器即可。

[0148]

输出时机控制部(41)生成表示第一输出通道~第k输出通道各者中的输出时机的第一输出时机信号~第k输出时机信号(nc1~nck)。输出部(42、43)在由第一输出时机信号~第k输出时机信号各者表示的输出时机分别输出第一像素驱动电压~第k像素驱动电压(g1~gk)。

[0149]

此外,输出时机控制部(41)包括以下的控制信号生成部、第一延迟生成部及第二延迟生成部以及延迟选择部。

[0150]

控制信号生成部接收第一输出通道及第k输出通道各者中的输出时机的指定(ta1、ta2),并在所指定的第一输出通道的输出时机生成第一延迟脉冲信号(ldr)。进而,在所指定的第k输出通道的输出时机生成第二延迟脉冲信号(ldl)。

[0151]

第一延迟生成部(411)接收所述第一延迟脉冲信号,生成经过从第一输出通道向第k输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现第一延迟脉冲信号的第一第一方向延迟移位信号~第k第一方向延迟移位信号(r1~rk)。

[0152]

第二延迟生成部(412)接收所述第二延迟脉冲信号,生成经过从第k输出通道向第一输出通道,每一个输出通道分别增加了单位延迟时间的延迟而出现第二延迟脉冲信号的第一第二方向延迟移位信号~第k第二方向延迟移位信号(l1~lk)。

[0153]

延迟选择部(413)针对第一输出通道~第k输出通道的每一个,从对应于同一输出通道的信号彼此中、即第一第一方向延迟移位信号~第k第一方向延迟移位信号各者及第一第二方向延迟移位信号~第k第二方向延迟移位信号各者中,选择出现延迟脉冲信号的时机早的一者,将针对第一输出通道~第k输出通道的每一者所选择的信号作为第一输出时机信号~第k输出时机信号(nc1~nck)输出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。